Brigham Young University BYU ScholarsArchive

Theses and Dissertations

2017-07-01

# Vivado Design Interface: Enabling CAD-Tool Design for Next Generation Xilinx FPGA Devices

Thomas James Townsend Brigham Young University

Follow this and additional works at: https://scholarsarchive.byu.edu/etd

Part of the Electrical and Computer Engineering Commons

# **BYU ScholarsArchive Citation**

Townsend, Thomas James, "Vivado Design Interface: Enabling CAD-Tool Design for Next Generation Xilinx FPGA Devices" (2017). *Theses and Dissertations*. 6492. https://scholarsarchive.byu.edu/etd/6492

This Thesis is brought to you for free and open access by BYU ScholarsArchive. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of BYU ScholarsArchive. For more information, please contact scholarsarchive@byu.edu, ellen\_amatangelo@byu.edu.

Vivado Design Interface: Enabling CAD-Tool Design for

Next Generation Xilinx FPGA Devices

Thomas James Townsend

A thesis submitted to the faculty of Brigham Young University in partial fulfillment of the requirements for the degree of

Master of Science

Brent E. Nelson, Chair Michael J. Wirthlin Jeffrey B. Goeders

Department of Electrical and Computer Engineering

Brigham Young University

Copyright  $\bigodot$  2017 Thomas James Townsend

All Rights Reserved

# ABSTRACT

# Vivado Design Interface: Enabling CAD-Tool Design for Next Generation Xilinx FPGA Devices

Thomas James Townsend Department of Electrical and Computer Engineering, BYU Master of Science

The popularity of field-programmable gate arrays (FPGA) has grown in recent years due to their potential performance advantages over sequential software, and as a prototyping platform for application-specific integrated circuits (ASIC). Vendors such as Xilinx offer automated tool suites that can be used to program FPGAs based on a RTL description. These tool suites are sufficient for general users, but they usually don't provide the opportunity to integrate custom computer-aided design (CAD) tools into the regular design flow.

Xilinx first offered this capability in their ISE tool suite with the Xilinx Design Language (XDL). Using XDL, a Xilinx design could be extracted from the regular CAD flow, run through an external tool, and injected back into the flow. Research tools targeting commercial FPGAs have most commonly been based on XDL. Vivado (Xilinx's newest tool suite) no longer supports XDL, preventing similar tools from being created for next-generation devices. Instead, Vivado includes a Tcl interface that exposes Xilinx's internal design and device data structures. Considerable challenges still remain to users attempting to leverage this Tcl interface to develop external CAD tools.

This thesis presents the Vivado Design Interface (VDI), a set of file formats and Tcl functions that address the challenges of exporting and importing designs to and from Vivado. To demonstrate its use, VDI has been integrated with RapidSmith2, an external FPGA CAD framework. To the best of our knowledge this work is the first successful attempt to provide an opensource tool-flow that can export designs from Vivado, manipulate them with external CAD tools, and re-import an equivalent representation back into Vivado.

#### ACKNOWLEDGMENTS

I would like to dedicate this thesis to my wife Michelle and daughter Aubrey. Michelle, you constantly inspire me by how hard you work to achieve your own dreams, and give me the extra push to do the same with mine. Aubrey, you are, without a doubt, the light of our lives. Your laugh gave me many enjoyable moments between the late nights spent studying and completing the research of this thesis. It is a great feeling to know that there will always be such love and support at home from both of you, even after a difficult day.

I must also express my thanks to my parents Daniel and Gillian Townsend. Mom and Dad, you have always been supportive of my life decisions and pursuits, and for that I will be forever grateful. You have taught me with love and patience (even through my difficult teenage years), and I will always cherish our wonderful memories together. I must also thank all members of my family and extended family, who have supported me throughout this journey.

Of course, I owe tremendous gratitude to my adviser, Dr. Brent Nelson, who oversaw and guided me as this thesis took shape. Not only did he introduce me to the Configurable Computing Lab three years ago, but he weathered the storm during a project switch after my first year in graduate school. His insight and guidance was very helpful in keeping my mind focused on the most important tasks moving forward, which was integral in the completion of this research.

I would also like to thank all professors in the Electrical and Computer Engineering Department whose courses turned me into a better learner and engineer. This is especially true of Dr. Mike Wirthlin and Dr. Brad Hutchings, whose courses on digital design and embedded systems inspired me to work with FPGAs. I also owe special thanks to Dr. Jeff Goeders who agreed to be on my committee at the last minute, and made several useful suggestions to improve this document.

Finally, I would like to thank all students in the Configurable Computing Lab who I took coursework with or who helped brainstorm ideas for my research. Specifically, I would like to thank Travis Haroldsen, Brad White, Bond Denhalter, and Mark Crossen for their help in making this thesis possible.

# TABLE OF CONTENTS

| List of Tables |                                         |   |     |  |  |   |         |   |       |     |     |   |     |    |

|----------------|-----------------------------------------|---|-----|--|--|---|---------|---|-------|-----|-----|---|-----|----|

| List of l      | Figures                                 | • |     |  |  | • | <br>    | • | <br>• |     | •   | • |     | ix |

| Chapte         | r 1 Introduction                        | • |     |  |  |   | <br>    |   |       |     |     |   |     | 1  |

| 1.1            | Motivation                              | • |     |  |  |   | <br>    | • |       |     |     |   |     | 1  |

| 1.2            | Problem Statement and Goals             | • |     |  |  |   | <br>    | • |       |     |     |   |     | 2  |

| 1.3            | Contributions                           |   |     |  |  |   |         |   |       |     |     |   |     |    |

| 1.4            | Thesis Organization                     | • |     |  |  | • | <br>    | • |       |     | •   |   |     | 4  |

| Chapte         | r 2 Background and Related Work         | • |     |  |  |   | <br>    |   |       |     |     |   |     | 5  |

| 2.1            | Xilinx FPGA Architecture                | • |     |  |  |   | <br>    |   |       |     |     |   |     | 6  |

|                | 2.1.1 Tiles                             |   |     |  |  |   |         |   |       |     |     |   |     |    |

|                | 2.1.2 Sites                             |   |     |  |  |   |         |   |       |     |     |   |     |    |

|                | 2.1.3 Wires and PIPs                    | • |     |  |  |   | <br>    |   |       |     |     |   |     | 9  |

| 2.2            | Xilinx Netlist Structure                |   |     |  |  |   |         |   |       |     |     |   |     |    |

| 2.3            | Vivado Tool Suite                       | • |     |  |  |   | <br>    |   |       |     |     |   |     | 11 |

| 2.4            | Tincr                                   |   |     |  |  |   |         |   |       |     |     |   |     |    |

| 2.5            | Xilinx Design Language (XDL)            | • |     |  |  |   | <br>    | • |       |     |     |   |     | 13 |

| 2.6            | RapidSmith                              |   |     |  |  |   |         |   |       |     |     |   |     |    |

|                | 2.6.1 RapidSmith2                       | • |     |  |  |   | <br>    |   |       |     |     |   |     | 16 |

| 2.7            | Vivado Design Interface                 | • | • • |  |  | • | <br>••• | • | <br>• |     | •   | • | ••• | 17 |

| Chapte         | r 3 VDI: Device Export                  | • |     |  |  |   | <br>    |   |       |     |     |   |     | 19 |

| 3.1            | XDLRC                                   |   |     |  |  |   |         |   |       |     |     |   |     |    |

| 0.11           | 3.1.1 Site PAD Names                    |   |     |  |  |   |         |   |       |     |     |   |     |    |

|                | 3.1.2 Floating VCC/GND Sources          |   |     |  |  |   |         |   |       |     |     |   |     |    |

|                | 3.1.3 Vivado Subsite Routing Tool       |   |     |  |  |   |         |   |       |     |     |   |     |    |

| 3.2            | Family Info XML                         |   |     |  |  |   |         |   |       |     |     |   |     |    |

|                | 3.2.1 Algorithm                         |   |     |  |  |   |         |   |       |     |     |   |     |    |

|                | 3.2.2 Alternate Types                   |   |     |  |  |   |         |   |       |     |     |   |     |    |

|                | 3.2.3 Compatible Types                  |   |     |  |  |   |         |   |       |     |     |   |     |    |

|                | 3.2.4 BEL Routethroughs                 |   |     |  |  |   |         |   |       |     |     |   |     |    |

|                | 3.2.5 Site PIP Corrections              |   |     |  |  |   |         |   |       |     |     |   |     |    |

|                | 3.2.6 Pin Direction Corrections         |   |     |  |  |   |         |   |       |     |     |   |     |    |

| 3.3            | Device Info XML                         |   |     |  |  |   |         |   |       |     |     |   |     | 33 |

| 3.4            | Cell Library XML                        | • |     |  |  |   | <br>    | • |       |     |     |   |     | 34 |

|                | 3.4.1 Finding Device Compatible Cells . |   |     |  |  |   |         |   |       |     |     |   |     |    |

|                | 3.4.2 Cell Placement Locations          |   |     |  |  |   |         |   |       |     |     |   |     |    |

|                | 3.4.3 Configurable Cell Properties      |   |     |  |  |   |         |   |       |     |     |   |     |    |

|                | 3.4.4 Macro Primitives                  | • |     |  |  |   | <br>    |   |       | • • | · • |   |     | 39 |

| 3.5            | Conclusion                              |   |     |  |  |   | <br>    |   |       |     |     |   |     | 41 |

| Chapte  | r 4 VDI: Design Import/Export      | 43 |

|---------|------------------------------------|----|

| 4.1     | Design Export                      | 44 |

|         |                                    | 44 |

|         | 4.1.2 Netlist.edf                  | 45 |

|         |                                    | 46 |

|         | 4.1.4 Macros.xml                   | 46 |

|         | 4.1.5 Placement.rsc                | 47 |

|         | 4.1.6 Routing.rsc                  | 49 |

| 4.2     | Design Import                      | 56 |

|         | 4.2.1 Placement.xdc                | 57 |

|         | 4.2.2 Routing.xdc                  | 57 |

| 4.3     | Vivado Tcl Interface Challenges    | 58 |

|         | 4.3.1 Ambiguous ROUTE Strings      | 59 |

|         | 4.3.2 Alternate Site Pins          | 60 |

|         | 4.3.3 VCC/GND BEL Pins             | 61 |

|         | 4.3.4 SLICE Placement Order        | 62 |

|         | 4.3.5 Macro Placement              | 63 |

|         | 4.3.6 LUT Routethroughs            | 64 |

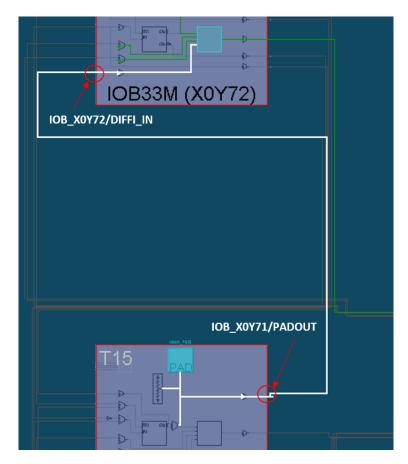

|         | 4.3.7 Routing Differential Pairs   | 65 |

| 4.4     | Why Two Design Checkpoint Formats? | 66 |

| 4.5     | Conclusion                         | 67 |

|         |                                    |    |

| Chapte  |                                    | 68 |

| 5.1     |                                    | 69 |

|         |                                    | 70 |

|         |                                    | 71 |

|         | 8                                  | 72 |

| 5.2     | $\mathbf{I} = \mathbf{S}$          | 74 |

| 5.3     |                                    | 76 |

| 5.4     | Conclusion                         | 79 |

| Chanta  | r 6 VDI Testing                    | 80 |

| Chapter |                                    |    |

| 6.1     |                                    | 81 |

| 6.2     |                                    | 83 |

| 6.3     |                                    | 85 |

|         | 8                                  | 86 |

|         | 5 8                                | 86 |

|         | 8                                  | 87 |

|         |                                    | 88 |

|         |                                    | 89 |

| 6.4     |                                    | 90 |

| 6.5     | Conclusion                         | 93 |

| Chapte  | r 7 Conclusion                     | 94 |

| 7.1     | Sustain      | nability                                         |

|---------|--------------|--------------------------------------------------|

| 7.2     | Contrib      | outions                                          |

| 7.3     | Future       | Work                                             |

| Referen | ices         |                                                  |

| Append  | ix A R       | apidSmith2 Documentation                         |

|         |              | s                                                |

|         |              | Device Data Structures                           |

|         | A.1.2        | Loading a Device                                 |

|         | A.1.3        | Supported Device Files                           |

| A.2     |              | s                                                |

|         | A.2.1        |                                                  |

|         | A.2.2        | The Cell Library                                 |

| A.3     | Placem       | nent                                             |

| A.4     |              | g                                                |

|         |              | Wires and Wire Connections                       |

|         | A.4.2        | Traversing Wire Objects                          |

|         | A.4.3        | Other Types of Connections                       |

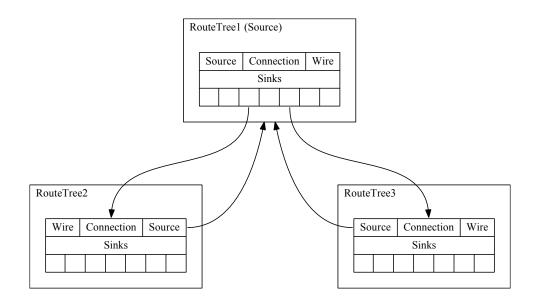

|         | A.4.4        | RouteTrees                                       |

|         | A.4.5        | Three Part Routing                               |

|         | A.4.6        | Intrasite Routing                                |

| A.5     | Design       | Import/Export                                    |

| A.6     | •            | ng New Device Files                              |

|         | A.6.1        | Creating New Device Files for Supported Families |

|         | A.6.2        | Supporting New Device Families                   |

|         | A.6.3        | Series7 Family Info Hand Edits                   |

|         | A.6.4        | UltraScale Family Info Hand Edits                |

|         |              |                                                  |

|         |              | SRT Documentation                                |

|         |              | uction                                           |

| B.2     |              | ution                                            |

|         | <b>B.2.1</b> | Tool Facts                                       |

|         | B.2.2        | Requirements                                     |

|         | B.2.3        | Steps                                            |

| B.3     |              | ology                                            |

|         | B.3.1        | Vivado Devices and XDLRC files                   |

|         | B.3.2        | Primitive Definitions                            |

|         | B.3.3        | VSRT GUI                                         |

| B.4     | User G       |                                                  |

|         | <b>B.4.1</b> | Regular Mode                                     |

|         | B.4.2        | Single-Bel Mode                                  |

| B.5     |              | es                                               |

|         | B.5.1        | Wire Hiding                                      |

|         | B.5.2        | Shape Border Colors                              |

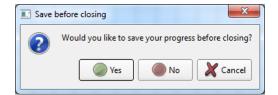

|         | B.5.3   | Saving                                 | 5         |

|---------|---------|----------------------------------------|-----------|

|         | B.5.4   | INOUT Pins                             | 5         |

|         | B.5.5   | Undo/Redo Functionality                | 6         |

|         | B.5.6   | Deleting Elements                      | 6         |

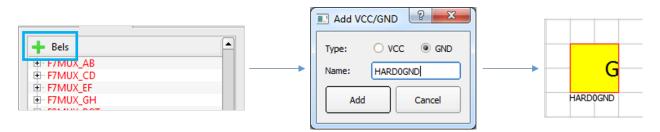

|         | B.5.7   | Adding VCC/GND BELs                    | 57        |

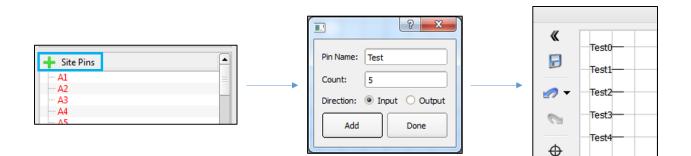

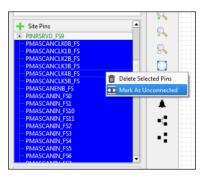

|         | B.5.8   | Manipulating Site Pins                 | 58        |

|         | B.5.9   | Configuration Options                  | <u>i9</u> |

|         | B.5.10  | Moving Shapes                          | 0'        |

|         | B.5.11  | Tool Bar Buttons and Shortcuts         | 0'        |

| B.6     | Known   | Issues                                 | 2         |

|         | . ~ ~.  |                                        |           |

| Appendi | ix C Si | imulated Annealing Placement Algorithm | 5         |

| C.1     | Anneal  | ling Schedule                          | 5         |

| C.2     | Cost Fu | unction                                | 6         |

| C.3     | Data St | tructures                              | 7         |

| C.4     | Sample  | e Output                               | 8         |

# LIST OF TABLES

| 2.1         | Vivado Device Families (organized by series) |

|-------------|----------------------------------------------|

| 6.1         | VDI Benchmarks                               |

| 6.2         | Nexys4 Test Designs                          |

| 6.3         | Series7 Placer Results                       |

| 6.4         | VDI Import/Export Times                      |

| A.1         | Cell Pin Types and Directions                |

| A.2         | Artix7 Alternate Pin Mappings                |

| <b>B</b> .1 | INOUT Pin Connections                        |

# LIST OF FIGURES

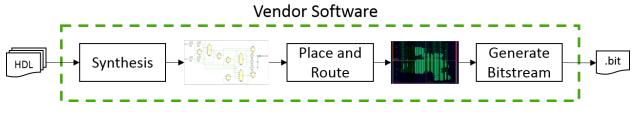

| 1.1        | Simplified FPGA Design Flow                                                                                                                                                | 1      |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

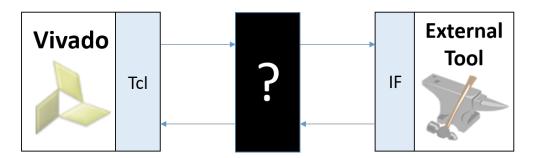

| 2.1<br>2.2 | External FPGA CAD Flow (the blue boxes represent interfacing software)                                                                                                     | 5      |

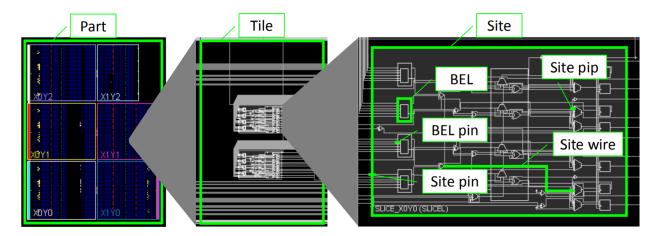

| 2.2        | Xilinx Device Hierarchy [1]          Artix7 Tiles                                                                                                                          | 6<br>7 |

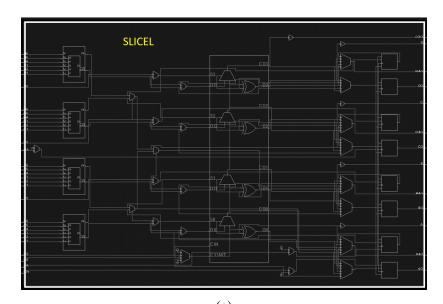

| 2.5<br>2.4 | Series7 SLICEL Site (a), and Highlighted Site Components (b)                                                                                                               | 8      |

| 2.4        | An example switchbox tile. The green wire represents a source wire, and the red wires represent all possible sink wires in the switchbox. The highlighed white sections of | 0      |

| 2.6        | the figure are PIP connections                                                                                                                                             | 9      |

|            | are ports.                                                                                                                                                                 | 10     |

| 2.7        | Original RapidSmith Tool Flow Using XDL                                                                                                                                    | 15     |

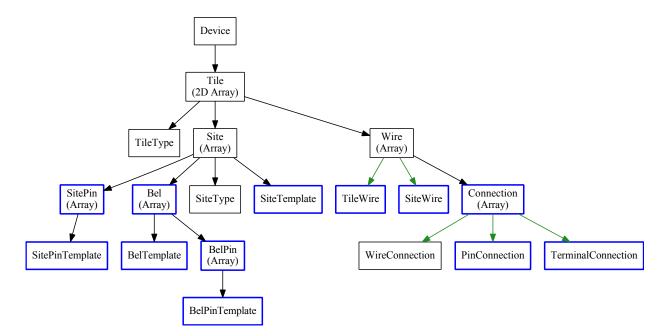

| 2.8        | RapidSmith <sup>2</sup> Device data structure tree. Classes and interfaces bolded in blue are sub-site components new to RapidSmith <sup>2</sup>                           | 16     |

| 2.9        | Components of the Vivado Design Interface (VDI)                                                                                                                            | 18     |

| 3.1        | VDI Device Files                                                                                                                                                           | 19     |

| 3.2        | IOB Site in Vivado's Device Browser                                                                                                                                        | 20     |

| 3.3        | UltraScale SYSMONE1 Package Pins                                                                                                                                           | 21     |

| 3.4        | Series7 TIEOFF                                                                                                                                                             | 21     |

| 3.5        | UltraScale floating GND BEL (top), and the GND primitive site replacement for XDLRC                                                                                        |        |

|            | files (bottom).                                                                                                                                                            | 22     |

| 3.6        | Vivado Subsite Routing Tool GUI.                                                                                                                                           | 24     |

| 3.7        | BITSLICE_RX_TX Alternate Types                                                                                                                                             | 26     |

| 3.8        | IPAD Alternate Types (there are none)                                                                                                                                      | 27     |

| 3.9        | Example Alternate Site Pin Renaming                                                                                                                                        | 28     |

| 3.10       | A group of cells placed on a SLICEL site (left) and a SLICEM site (right).                                                                                                 | 29     |

|            | Compatibility Testing for Single-BEL Sites                                                                                                                                 | 30     |

|            | Site PIP Decomposition                                                                                                                                                     | 32     |

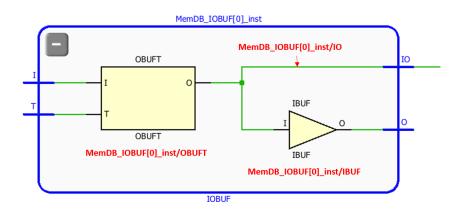

| 3.13       | Vivado Macro Cell                                                                                                                                                          | 39     |

| 4.1        | Vivado Design Interface (VDI) Design Flows                                                                                                                                 | 43     |

| 4.2        | Example Cell Placement                                                                                                                                                     | 48     |

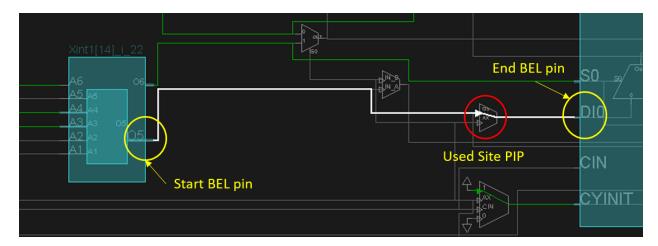

| 4.3        | Site PIP Usage                                                                                                                                                             | 50     |

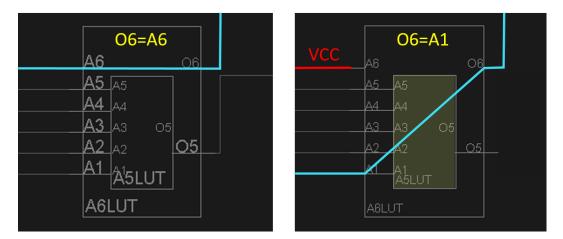

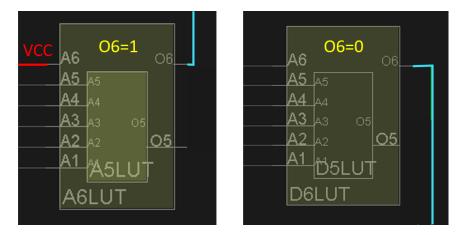

| 4.4        | Two examples of LUTs configured as routethroughs in Vivado. The net highlighted in red represents VCC.                                                                     | 51     |

| 4.5        | Flip-Flop BEL Configured as a Permanent Latch in Vivado                                                                                                                    | 52     |

| 4.6        | Two LUTs Configured as Static Sources in Vivado                                                                                                                            | 53     |

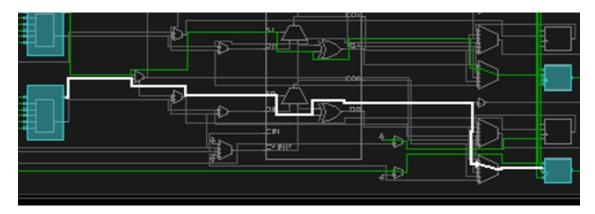

| 4.7        | Vivado Intrasite Net (highlighted in white)                                                                                                                                | 54     |

| 4.8        | Vivado Intersite Net (highlighted in white)                                                                                                                                | 55     |

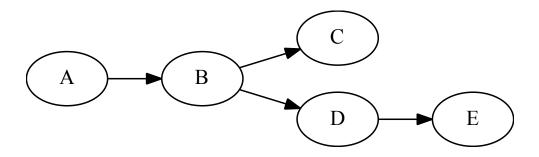

| 4.9        | Sample Route (A, B, C, D, and E represent device wires)                                                                                                                    | 58     |

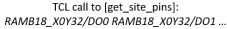

| 4.10       | Sumple Route $(\Lambda, D, C, D, and D)$ represent device whes $(\Lambda, D, C, D, and D)$                                                                                 | 20     |

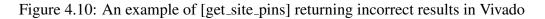

| 4.12                     | An example of VCC routing to an unused BEL pin (A6)                                                                                                                         | 61<br>62       |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|                          | representation of a SLICEL site.                                                                                                                                            | 63             |

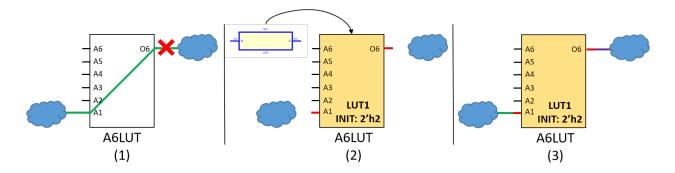

|                          | Visualization for how to replace a LUT routethrough with a LUT1 Xilinx cell Differential Pair Net                                                                           | 64<br>65       |

| 5.1                      | RapidSmith2 Supported Design Flows (the red box represents VDI)                                                                                                             | 68             |

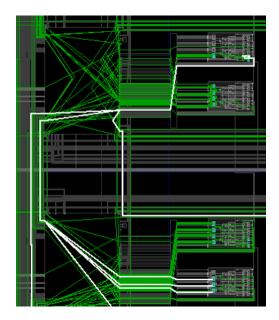

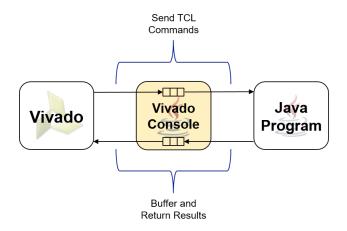

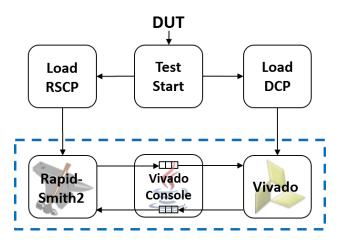

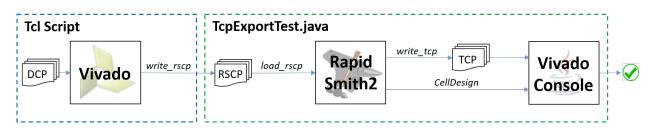

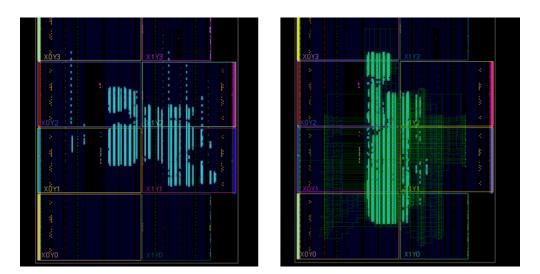

| 6.1<br>6.2<br>6.3<br>6.4 | Vivado Console                                                                                                                                                              | 81<br>82<br>83 |

| 6.5<br>6.6               | inal Vivado design                                                                                                                                                          | 84<br>88       |

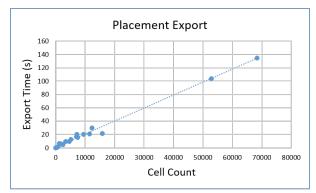

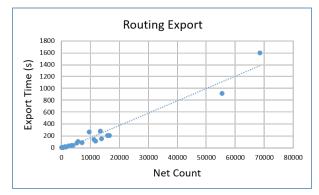

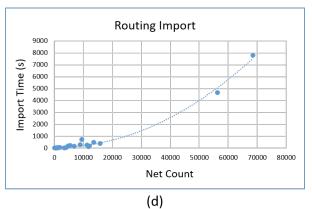

| 6.7                      | annealing placer (right)       VDI Import/Export Trends                                                                                                                     | 89<br>91       |

| A.1                      | RapidSmith2 Device data structure tree. Green arrows represent inheritance, and black arrows represent association. Classes and Interfaces bolded in blue are new to Rapid- |                |

| A.2                      | Smith 2                                                                                                                                                                     | 101            |

| A.3                      | of the netlist                                                                                                                                                              | 105            |

|                          | part of the same net.                                                                                                                                                       | 110            |

| A.4                      | Bidirectional Net                                                                                                                                                           | 110            |

| A.5                      | Example INTRASITE Net (left) and INTERSITE Net (right)                                                                                                                      |                |

| A.6                      | Properties of a Vivado FDCE Cell                                                                                                                                            |                |

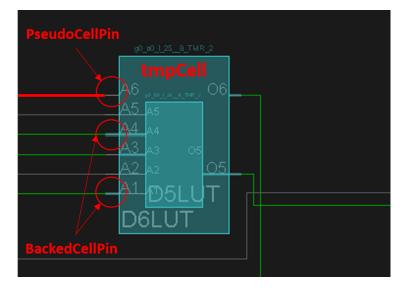

| A.7                      | Pseudo Cell Pin Example                                                                                                                                                     |                |

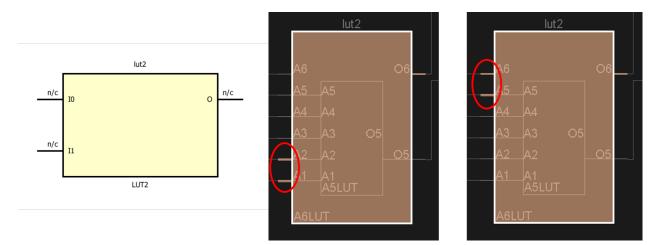

|                          | LUT Pin Permutation Example                                                                                                                                                 |                |

|                          | Multi-Tile Xilinx Wire                                                                                                                                                      |                |

|                          | Visual Representation of a RapidSmith2 RouteTree                                                                                                                            |                |

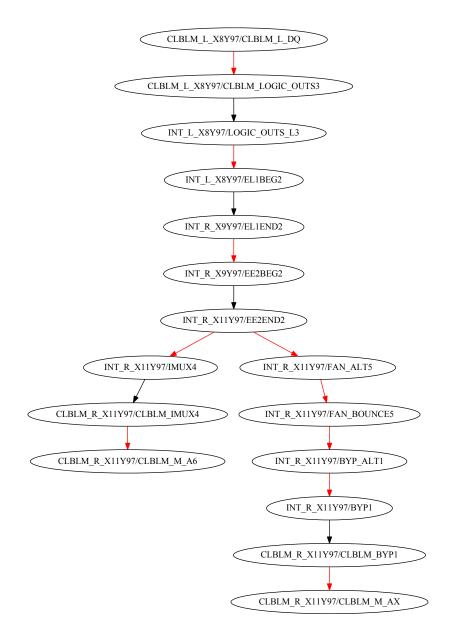

|                          | Sample RapidSmith2 RouteTree (red edges represent PIP connections)                                                                                                          |                |

| A.12                     | Three-Part Routing                                                                                                                                                          | 129            |

| <b>B</b> .1              | XDLRC Creation Flow                                                                                                                                                         | 143            |

| B.2                      | VSRT GUI Start View (Top) and Primitive Site View (Bottom)                                                                                                                  | 151            |

| B.3                      | VSRT GUI Start Screen                                                                                                                                                       |                |

| <b>B.</b> 4              | User Mode Prompt                                                                                                                                                            | 155            |

| B.5                      | BUFGCTRL Site in VSRT                                                                                                                                                       | 156            |

| B.6                      | Adding a BEL to the Drawing Pane                                                                                                                                            |                |

| <b>B</b> .7              | Wire Connections in VSRT                                                                                                                                                    |                |

| B.8                      | BUFGCTRL Site in Vivado                                                                                                                                                     |                |

| B.9                      | Completed BUFGCTRL in VSRT                                                                                                                                                  | 158            |

| <b>B.</b> 10 | VSRT Save Prompt                                                                     |

|--------------|--------------------------------------------------------------------------------------|

| <b>B.</b> 11 | How to mark a site as complete in VSRT                                               |

|              | GTHE3_CHANNEL in VSRT                                                                |

|              | Complete GTHE3_CHANNEL in VSRT                                                       |

|              | How to mark site pins as unconnected in VSRT                                         |

|              | Wiring Hiding Options                                                                |

|              | Shape Border Colors                                                                  |

|              | Save Progress Prompt                                                                 |

| <b>B</b> .18 | Vivado GND BEL (shown in the red box)                                                |

|              | How to add new VCC/GND BELs to a site                                                |

| B.20         | How to add new site pins to a site                                                   |

|              | How to mark site pins as unconnected or remove them in VSRT                          |

| B.22         | BEL Configuration Popup Window                                                       |

| B.23         | Site Pin Moving Bug                                                                  |

| B.24         | Missing Site Pin Names in Vivado (shown in red)                                      |

| B.25         | Example of multiple drivers on a site wire. Output BEL pins are highlighted with red |

|              | boxes and input BEL pins are highlighted with green boxes                            |

| <b>C</b> 1   |                                                                                      |

| C.1          | Example Bounding Box                                                                 |

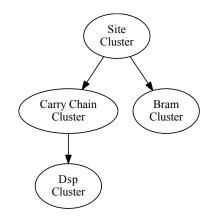

| C.2          | Site Cluster Inheritance Tree                                                        |

| C.3          | Sample Placement Output                                                              |

# CHAPTER 1. INTRODUCTION

# 1.1 Motivation

The popularity of field-programmable gate arrays (FPGA) has grown in recent years due to their potential performance advantages over sequential software, and as a prototyping platform for application specific integrated circuits (ASIC). Several companies fabricate FPGAs, including Xilinx, Intel (Altera), Microsemi, and Lattice. Each of these vendors offer a set of design automation tools to help customers implement hardware designs on their devices. Figure 1.1 shows the typical implementation flow for FPGA-based systems using these automated tools.

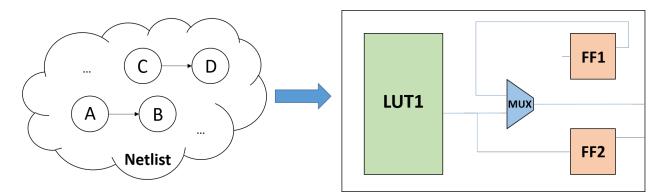

Figure 1.1: Simplified FPGA Design Flow

As the figure shows, the process begins with a hardware circuit that has been expressed using a hardware description language (HDL). Common HDLs include VHDL, Verilog, and SystemVerilog. The HDL description is passed into the FPGA vendor software, where it is synthesized into a device-compatible netlist. The logical netlist is then mapped onto the physical components of the FPGA, and a bitstream (.bit file) is generated that can be loaded into the FPGA's configuration memory. Once the design is loaded into the configuration memory, the FPGA is dynamically configured to implement the corresponding circuit.

Due to the proprietary nature of vendor tools, however, it is difficult to customize the FPGA implementation flow with user created computer-aided design (CAD) tools. For example, it is not possible to create a plug-in for Xilinx's ISE or Vivado tool suite that runs an experimental placer

or router instead of the proprietary version. This lack of control limits the type of research that can be done with vendor software, and motivates the use of external, open-source FPGA CAD tools. Over the past few decades, a significant amount of CAD tool research for FPGA-based systems has been pursued outside the confines of vendor tools.

The most common approach to creating external tools has been to use the extremely successful VPR/VTR CAD suite [2] [3]. VTR (verilog-to-routing) offers a complete open-source FPGA CAD flow that includes algorithms for synthesis, technology mapping, packing, placement, routing, and timing and area estimation. Users of VTR can define hypothetical FPGA architectures, and run tools against those architectures to see how they perform. Alternatively, they can modify any stage of the implementation flow (such as the packer, placer, or router) to test and evaluate new CAD ideas and algorithms. VTR has helped lead to many significant contributions in the area of FPGA CAD research, but has had little success in targeting commercial devices.

Targeting commercial FPGA devices has traditionally been more difficult. Most research experiments and open-source CAD tools that aim to do this have been built upon the Xilinx Design Language (XDL), which is capable of interfacing with Xilinx's ISE tool suite <sup>1</sup>. The contributions of projects leveraging XDL have been many. Frameworks such as RapidSmith [5] and Torc [6] provide easy-to-use APIs to modify XDL netlists in a variety of useful ways. [7] and [8] create partial reconfiguration frameworks, capable of swapping logic segments at runtime. [9] and [10] look at ways to decrease the implementation times of FPGA designs and increase designer productivity. [11] and [12] look to create reliable, fault-tolerant FPGA systems. And [13] tries to bridge the gap between the VPR CAD flow with real Xilinx devices. Many significant contributions using XDL have also been made in other areas of FPGA research such as security and debugging.

# **1.2 Problem Statement and Goals**

Clearly, analyzing and modifying commercial FPGA designs outside of vendor tools has proven useful. With the release of Vivado, however, Xilinx discontinued support for XDL, making external tools and frameworks that rely on the interface incompatible with next-generation Xilinx devices (such as UltraScale and Ultrascale+). Vivado instead provides access to its internal design and device data structures through a Tcl application programming interface (API) exposed to the

<sup>&</sup>lt;sup>1</sup>Tools that target other vendor parts have been created [4], but are less common.

user. The same information that was contained within XDL can now be extracted through Tcl API calls, but there are many challenges associated with using Tcl for this purpose. The first goal of this work is to navigate through the challenges of Vivado's Tcl interface to create a general-purpose way to export design information from Vivado, and import design information back into Vivado (i.e. a XDL replacement). The second goal is to integrate the Vivado XDL replacement with an existing CAD Tool Framework for testing and verification. The third goal is to create an example CAD tool, to demonstrate the possible applications for Vivado CAD tools.

# 1.3 Contributions

The work described in this thesis is the first successful attempt to provide an open-source tool-flow that can export designs from Vivado, manipulate them with external CAD tools, and re-import valid design representations back into Vivado. The main contributions of this thesis are listed below, and demonstrate why the work is novel:

- It provides insight into the many low-level details of a fully implemented Xilinx design, and how to best represent those details in an external format. It also documents how to successfully reconstruct a design in Vivado.

- It introduces the Vivado Design Interface (VDI), an extension of *Tincr* [14]. VDI uses Vivado Tcl commands to define an organized framework for interfacing with Vivado designs and devices. Specifically, VDI allows users to extract complete design and device information from Vivado to be used with external tools. It also allows users to import modified designs back into Vivado. The performance characteristics of VDI (i.e. how long it takes to import/export designs) are presented.

- It describes the integration of VDI with RapidSmith2 [15], an external CAD tool framework. This integration enables a variety of CAD tools to be written for Vivado designs.

- It demonstrates the correctness of VDI and RapidSmith2 through two methods of verification: (1) Java unit tests which verify that the RapidSmith2 design representation matches the corresponding Vivado design, and (2) On-board hardware tests which verify that designs are still functionally correct after being passed through RapidSmith2 and back into Vivado.

- It presents the implementation and results of a simulated-annealing placer that has been implemented in RapidSmith2.

- It introduces support for UltraScale devices in RapidSmith2. CAD tools targeting UltraScale devices can now be created, which was previously impossible.

- It documents the open-source release of RapidSmith2 at GitHub to allow FPGA CAD researchers across the country and world to develop Vivado CAD algorithms.

One other important contribution to note is that the work presented in this thesis has also been formatted into a conference paper that was accepted into Field Programmable Logic and Applications (FPL) 2017. The title of the FPL paper is "Vivado Design Interface: An Export/Import Capability for Vivado FPGA Designs," and presents many of the same concepts introduced in this thesis.

# **1.4 Thesis Organization**

The remainder of the thesis is outlined as follows. Chapter 2 provides required background for the remainder of the document. This includes an overview of FPGA architecture, Xilinx netlists, Vivado's Tcl interface, Tincr, and the VDI flow. Chapter 3 describes how VDI represents Vivado device information. Chapter 4 describes how VDI represents Vivado design information. Chapter 5 describes the necessary updates to RapidSmith2 in order to support importing and exporting Vivado designs through VDI. Chapter 6 presents the results of several experiments using VDI and RapidSmith2. Finally, chapter 7 concludes the thesis and discusses potential future work.

Unless otherwise stated, tests and experiments in this work were performed on a machine running Windows 7 64-bit with a Core i7-860 processor, 8GB of DDR3 RAM, and 1TB 7200RPM SATA hard disk. Also, this work was done with Vivado version 2016.2. Future versions of Vivado may work with VDI, but they have not yet been tested.

# CHAPTER 2. BACKGROUND AND RELATED WORK

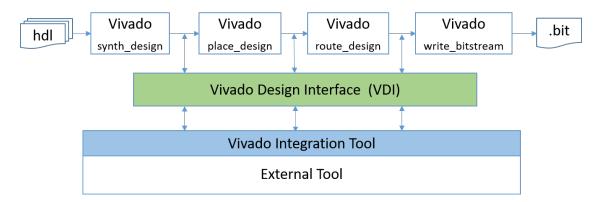

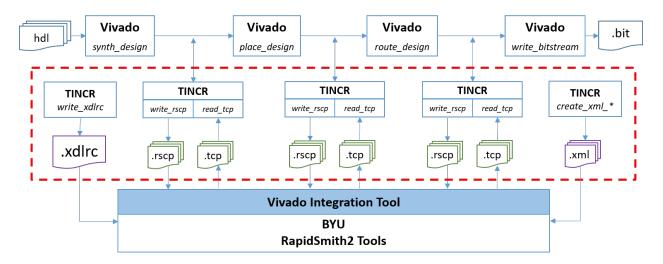

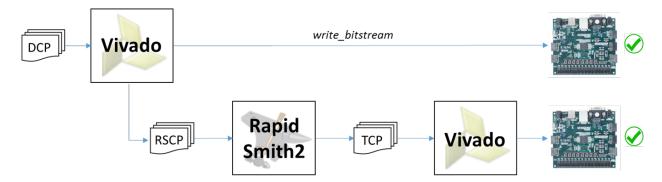

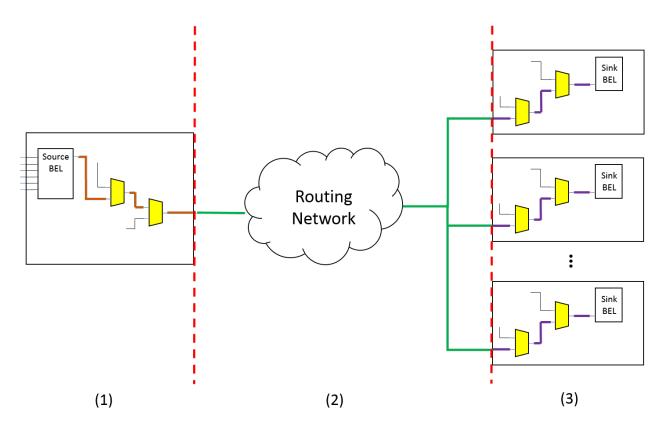

As stated in the introduction, the primary goal of this work is to create an interface into Vivado that can be used with external FPGA CAD tools. Specifically, the goal is to enable the flow depicted in Figure 2.1 while determining an appropriate solution for the black box. This chapter provides insight to previous projects that the work presented in this thesis builds upon. It also introduces important terminology. The following sections give a high-level overview of the relevant background information for the reader.

Figure 2.1: External FPGA CAD Flow (the blue boxes represent interfacing software)

Sections 2.1 and 2.2 introduce Xilinx FPGA terminology that is used throughout the document. Section 2.3 discusses Vivado's Tcl interface and why it is not suitable for the creation of FPGA CAD tools. Section 2.4 describes Tincr, a Vivado Tcl plugin. Tincr was the first research project to explore Vivado design and device extraction. It created a device extraction API and demonstrated a proof-of-concept design extraction which this thesis further explores. Sections 2.5 and 2.6 describe the Xilinx CAD tool flow based on XDL, ISE, and the original RapidSmith CAD framework. Since XDL is no longer supported by Xilinx, this work attempts to create a similar tool flow with Vivado's Tcl interface. It is assumed that the reader has a basic knowledge of FPGAs and the FPGA implementation flow, as those topics are not described here.

# 2.1 Xilinx FPGA Architecture

Xilinx FPGAs can be broken down into series, families, and individual parts. At the highest level, a series defines a unique FPGA architecture. Vivado currently supports three different series: Series7, UltraScale, and UltraScale+. As shown in Table 2.1, each series can be broken down into a list of families. These families all use the same series architecture, but are optimized for cost, power, performance, size, or another metric.

Table 2.1: Vivado Device Families (organized by series)

| Series7 | UltraScale | UltraScale+ |

|---------|------------|-------------|

| Kintex  | Kintex     | Kintex      |

| Virtex  | Virtex     | Virtex      |

| Artix   |            |             |

| Spartan |            |             |

| Zynq    |            |             |

Families can further be broken down into one or more parts (actual FPGA devices). A Xilinx part has a variety of attributes including its number, package type, and speed-grade. Take the part "xcku025-ffva1156-1-c" as an example. This part is within the Kintex UltraScale family, uses a "ffva1156" package type, and has a speed grade of "1-c". Figure 2.2 shows the device hierarchy of a Xilinx part . The following subsections describe each internal component of a Xilinx FPGA as shown in the figure.

Figure 2.2: Xilinx Device Hierarchy [1]

Figure 2.3: Artix7 Tiles

# 2.1.1 Tiles

A Xilinx FPGA is organized into a two-dimensional array of Tiles. Each tile is a rectangular component of a device that performs a specific function such as implementing digital logic or storing BRAM memory. Tiles are stamped across a device and wired together through the general routing fabric. All copies of a tile type are identical or nearly identical (they may have minor routing differences). Figure 2.3 displays three types of tiles in an Artix7 device. The **VBRK** tile on the left is used for wiring signals between other tiles (these connections are not programmable). The **INT\_L** tile on the right is a switchbox tile. These are reconfigurable routing tiles that allow a single wire to be routed to various locations within the FPGA. The **CLBLL** tile in the middle is used to implement combinational and sequential digital logic, and is the fundamental component of Xilinx FPGAs. Other tile types include DSP, BRAM, FIFO, and IOB.

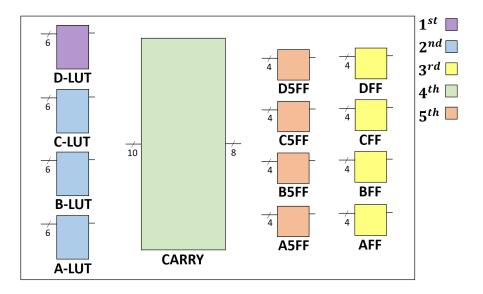

# 2.1.2 Sites

Tiles generally consist of one or more Site objects, which organize the hardware components of the tile into related groups. Specifically, sites are the part of a tile which perform the tile's "useful" function. The remainder of the tile is used to wire signals to and from its corresponding sites. Figure 2.4 shows an example site of type SLICEL within a Series7 CLBLL tile. As the figure shows, a site consists of three main components which are connected through wires:

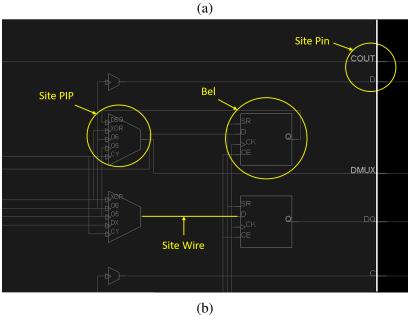

Figure 2.4: Series7 SLICEL Site (a), and Highlighted Site Components (b)

- Site PIPs: Also called routing muxes, these are reconfigurable routing PIPs used to specify the internal routing of a site. In Vivado, site PIPs are usually configured automatically as cells in a design are placed (based on cell properties and placement locations).

- **BEL**s: **B**asic **EL**ements are hardware components within a site for implementing digital logic. For example, look-up-tables (LUT) within a SLICEL are used to implement logic

equations, and flip-flops (FF) are used as storage. In a synthesized netlist, design elements are mapped to BELs during implementation.

• Site Pins: These pins are connected to wires of the parent tile and typically drive/receive signals from the general fabric.

# 2.1.3 Wires and PIPs

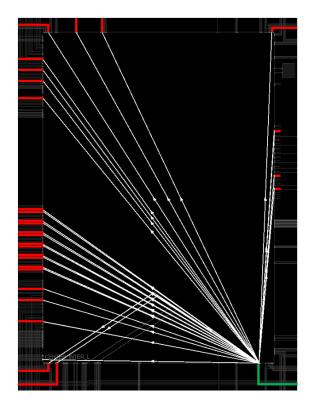

FPGA components are connected together using metal Wires (called Nodes in Vivado). To make the FPGA reconfigurable, wires are connected through programmable interconnect points (PIPs). Individual PIPs can be enabled or disabled as a design is being routed, and a string of enabled PIPs uniquely identify the used wires of a physical route. PIPs are most commonly found in switchbox tiles, and enable a single wire to be routed to several locations on the chip. Figure 2.5

Figure 2.5: An example switchbox tile. The green wire represents a source wire, and the red wires represent all possible sink wires in the switchbox. The highlighed white sections of the figure are PIP connections.

shows an example switchbox with its corresponding PIPs. The red wires represent all downhill nodes that the green wire can connect to through a PIP connection.

## 2.2 Xilinx Netlist Structure

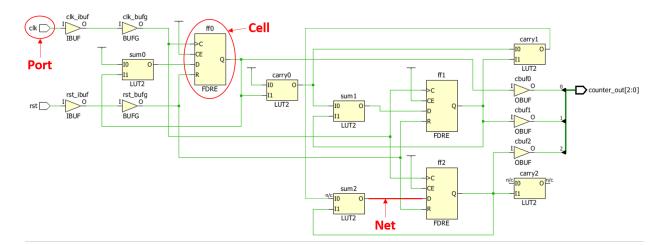

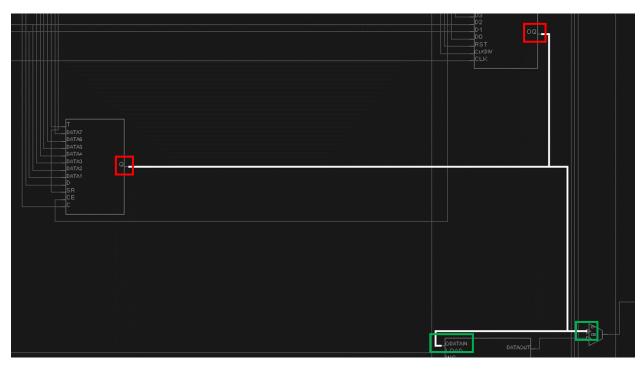

During the synthesis stage of implementation, a digital circuit expressed using RTL (VHDL or Verilog) is translated to a lower level Xilinx netlist. This netlist describes a digital circuit in terms of primitive elements that can directly target hardware on a Xilinx FPGA. In terms of granularity, a Xilinx netlist is more abstract than gates and transistors, but more detailed than RTL. A list of valid primitives that can be used within a Xilinx netlist can be found at [16] for Series7 devices and [17] for Ultrascale devices. The primitives of a Xilinx netlist are wired together to create a digital circuit capable of being implemented on a FPGA. Figure 2.6 shows an example netlist for a 3-bit counter created in Vivado.

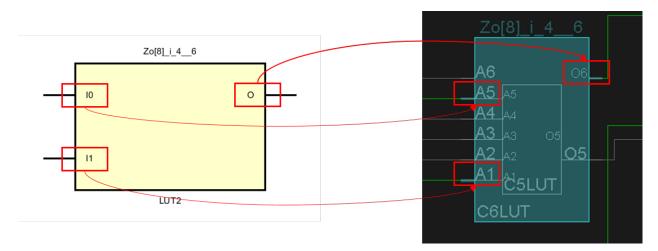

As the figure shows, Vivado netlists are composed of three primary components: Cells, Nets, and Ports. Cells are **instances** of Xilinx primitives. They are the basic building blocks of a Xilinx netlist and implement the actual logic of a digital design. The most commonly used cells include:

• Look Up Tables (LUTs): Implement logic equations such as  $O6 = (A1 + A2) \oplus A3$ .

Figure 2.6: Schematic of a 3-bit counter in Vivado using LUT and FDRE cells. The yellow boxes are cells, the green lines are nets, and and the white figures on the edge of the diagram are ports.

- Flip-Flops (FDxx): Single-bit storage elements. Figure 2.6 uses a FDRE cell which specifies a rising-edge flip-flop with a reset port, but ties the clock enable port high. Other types of FDxx cells can be used to include a clock enable port.

- Block Ram (BRAMs): On-chip FPGA memory.

- Digital Signal Processing Units (DSPs): Perform complex arithmetic functions efficiently.

- Buffers (BUF): IO, clock, and other types of signal buffers.

Several other types of cells can be used, but the ones in the list above are the most common. Nets connect cells together. In other words, the output of one cell is wired to the input of another cell using a net. Ports are simply design input/output (IO). In terms of a FPGA design, ports are mapped to specific peripheral pins of the FPGA for chip IO.

It is important to note that a Xilinx netlist is purely logical. There is no physical information within the netlist (i.e. there is no information about where the cells have been placed, or how the nets have been routed). When exporting a design from Vivado, the Xilinx netlist representation is converted to an electronic design interchange format (EDIF).

#### 2.3 Vivado Tool Suite

In recent years, Xilinx released their new vendor tool for programming FPGAs: Vivado. Vivado supersedes ISE (the previous tool), and is the only tool suite that supports the latest Xilinx families such as UltraScale. The most significant change with Vivado is the introduction of a Tcl interface. Using Tcl commands, users of Vivado can write Tcl code to script design flows, set constraints on a design, and perform low-level design modifications. There are Tcl commands for a variety of useful functions including: finding all tiles in a device, getting all of the used PIPs in a routed design, and grouping related cells into a macro. For example, the Tcl command [get\_sites -filter (SITE\_TYPE==SLICEL && !IS\_USED)] will return a list of all unused SLICEL sites in the current device. This list could potentially be used to add additional logic to a design post-route. The Tcl interface is a powerful addition to the Xilinx tool suite, but suffers some major drawbacks:

• Tcl, being an interpreted language, is slow. Compiled or managed runtime systems are better options for performance.

- Vivado's Tcl interface does not manage memory well. A simple Tcl script can cause the memory usage of Vivado to grow indefinitely.

- Tcl does not natively support higher-level programming constructs, making it more difficult to implement complex algorithms (such as PathFinder).

These drawbacks largely motivate using the Tcl interface as an *extraction* tool, instead of a CAD framework itself. Vivado Tcl scripts are the basis for much of the work found in this thesis.

# 2.4 Tincr

Tincr [14] is a Tcl plugin to Vivado created by Brad White. It introduces two useful packages: TincrCAD and TincrIO. These packages augment Vivado's native Tcl interface with a set of high-level commands that (a) simplify a variety of Vivado tasks and (b) add additional functionality to the Tcl interface in the form of new Tcl commands. TincrCAD focuses on commands for implementing CAD tools directly in Vivado, and TincrIO focuses on commands for extracting device and design data from Vivado. The work in this thesis builds upon the initial work done with TincrIO, which demonstrated the plausibility of manipulating Vivado designs outside of Vivado.

Two aspects of TincrIO were particularly useful. The first is [tincr::write\_xdlrc], a Tcl command capable of creating a complete XDLRC device file (described in the next section) for any Vivado device. Series7 XDLRC files were exhaustively tested against their ISE counterpart to verify that the command generated valid and complete device files. However, UltraScale and UltraScale+ XDLRC files generated from this command were incomplete and not well tested. Chapter 3 describes the required modifications to [tincr::write\_xdlrc] to support UltraScale devices.

The second useful aspect of TincrIO is the proposed Tincr Checkpoint (TCP) format. In the original distribution of Tincr, a directory full of XDC constraint files was used to externally represent a Vivado design. The authors of Tincr demonstrated that by using these checkpoints, a FPGA design could be theoretically exported from Vivado in an open-source format, and then reimported back into Vivado. These checkpoints, however, were simply a *proof-of-concept*. Several important aspects of a design (such as BEL routethroughs and an accurate depiction of routing) can not be represented in the original TCP specification. Chapter 4 describes an improved checkpoint format, which creates an accurate external design representation that encapsulated *all* parts of a design.

#### 2.5 Xilinx Design Language (XDL)

The Xilinx Design Language is a command line interface into Xilinx's ISE tool suite. Using a single command, xdl, both device and design information can be extracted from ISE for external use. Device specific information is exported via XDLRC files, which contain a detailed listing of all the physical components inside of a Xilinx FPGA. This includes the tiles, sites, BELs, and routing resources (without timing information) available in the specified part. XDLRC files are very verbose (with the largest devices being up to 100GB), and so they need to be compressed before they can practically be used with external CAD tools. Listing 2.1 shows the general format for a tile within a XDLRC file. As can be seen, the tile's sites, wires, and PIP connections are all listed. To learn more about XDLRC files (such as the meaning of each specific token), review [18].

Listing 2.1: XDLRC Tile Format

```

(tile 1 14 CLB_X6Y63 CLB 4

// List of sites in the tile and wires that connect to the site pins

(primitive_site SLICEL_X9Y127 SLICEL internal 27

(pinwire BX input BX_PINWIRE3)

...

)

...

// List of wires in the tile and their connections

(wire E2BEG0 5

(conn CLB_X7Y63 CLB_E2BEG0)

(conn INT_X8Y63 E2MID0)

...

)

...

// List of pips in the tile

(pip INT_X7Y63 BEST_LOGIC_OUTS0 -> BYP_INT_B5)

```

```

(tile_summary CLB_X6Y63 CLB 122 403 148))

```

Design data is exported via XDL files. XDL files are a combination of the logical portion of a design (a netlist), as well as placement and routing information for the design. A XDL netlist is organized into **instances**. Each instance represents a site on the corresponding device, with attribute strings describing how the site is internally configured (i.e. what BELs are being used and how they are connected). In a placed design, instances are assigned a corresponding site value. Listing 2.2 gives an example of a XDL instance targeting a SLICEL site.

Listing 2.2: XDL Instance

inst "instanceName" "SLICEL", placed CLB\_X14Y4 SLICE\_X23Y8 , cfg " BXINV::#OFF BYINV::#OFF CEINV::#OFF CLKINV::#OFF COUTUSED::#OFF CYOF::#OFF CYOG::#OFF CYINIT::#OFF DXMUX::#OFF DYMUX::#OFF F::#OFF F5USED::#OFF FFX::#OFF FFX\_INIT\_ATTR::#OFF FFX\_SR\_ATTR::#OFF FFY::#OFF FFY\_INIT\_ATTR::#OFF FFY\_SR\_ATTR::#OFF FXMUX::#OFF FXUSED::#OFF G:DCM\_AUTOCALIBRATION\_DCM\_clock/DCM\_clock/md/RSTOUT1:#LUT:D=A1 \_BEL\_PROP::G:LIT\_NON\_USER\_LOGIC:DCM\_STANDBY GYMUX::#OFF REVUSED::#OFF SRINV::#OFF SYNC\_ATTR::#OFF XBUSED::#OFF XMUXUSED::#OFF XUSED::#OFF YBUSED::#OFF YMUXUSED::#OFF YUSED::0 "

;

Routing is represented using XDL **nets**. XDL nets contain a list of connected instance pins (i.e. site pins), and a list of PIPs used to physically connect the pins together. An example net is shown in Listing 2.3. XDL provided a means for representing fully placed and routed designs from ISE.

```

Listing 2.3: XDL Net

```

```

net "netName" ,

outpin "instanceNameOfSourcePin" Y ,

inpin "instanceNameOfSinkPin" RST ,

pip CLB_X14Y4 Y_PINWIRE1 -> BEST_LOGIC_OUTS5_INT ,

```

```

pip DCM_BOT_X15Y4 SR_BO_INT3 -> DCM_ADV_RST ,

pip INT_X14Y4 BEST_LOGIC_OUTS5 -> OMUX8 ,

pip INT_X15Y5 OMUX_EN8 -> N2BEGO ,

pip INT_X15Y7 N2ENDO -> SR_BO ,

;

```

The combination of XDLRC and XDL files make it possible to perform design manipulations outside the confines of vendor tools. It has been a great resource to the FPGA CAD research community. There are, however, a few problems with XDL. The first is that, as Listing 2.2 shows, XDL instances are largely black boxes. They don't explicitly show the BELs and wires that are being used *inside* of a site. This makes it difficult to write CAD tools that need access to this information (such as a packer). The second, and more challenging, issue is that with Vivado Xilinx discontinued support for XDL. CAD tools and frameworks built on XDL will not be compatible with next-generation devices. As previously stated, the primary objective of this thesis is to create a XDL-alternative for Vivado designs so that CAD development can continue to happen for future Xilinx devices. The interested reader is referred to [18] for a complete guide to XDL.

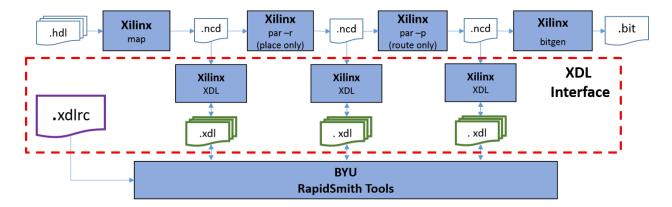

# 2.6 RapidSmith

The original RapidSmith [5] is a FPGA CAD Tool framework for Xilinx FPGAs. Written in Java, it offers a rich set of APIs, data structures, and useful functions to analyze and manipulate XDL netlists. RapidSmith was developed by Chris Lavin, who initially used it to reduce FPGA

Figure 2.7: Original RapidSmith Tool Flow Using XDL

compilation times by creating a hard macro design flow. It has since grown to be the basis of several research projects and applications (many of which are listed in chapter 1). RapidSmith has been especially popular in the area of FPGA security and reliability. Figure 2.7 shows the available design flows using RapidSmith.

Users of RapidSmith can write CAD tools that operate on a Xilinx design post-synthesis, post-place, or post-route. The modified design can then be re-imported back into ISE to complete the remainder of the implementation flow. To handle very large XDLRC files, RapidSmith compresses them into compact device files. Once compressed, the RapidSmith device files are MegaBytes in size as opposed to GigaBytes. RapidSmith only supports designs from Xilinx's ISE tool suite, and can be downloaded at http://rapidsmith.sourceforge.net.

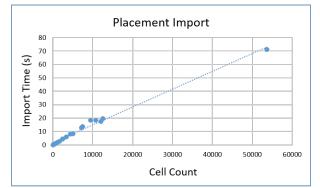

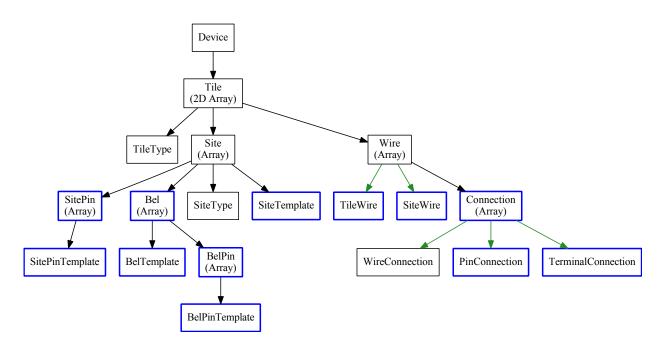

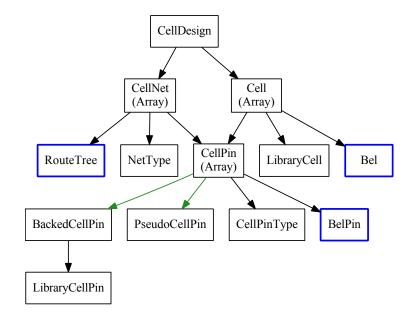

# 2.6.1 RapidSmith2

The RapidSmith framework has helped researchers create several different CAD tools targeting Xilinx devices. Due to the format of XDL however, these CAD tools always operate at site boundaries. This makes it difficult to explore sub-site CAD algorithms that work explicitly

Figure 2.8: RapidSmith2 Device data structure tree. Classes and interfaces bolded in blue are sub-site components new to RapidSmith2.

with sub-site components (i.e. BELs, site PIPs, etc.) such as packers. Travis Haroldsen was interested in exploring packing algorithms for Virtex6 devices [19], and so created RapidSmith2 [15]. RapidSmith2 updated the internal data structures of RapidSmith to the BEL and cell-level, allowing algorithms to have finer grained control over sub-site placement and routing. Because it was originally targeting the Virtex6 architecture, RapidSmith2 took as input a XDL netlist, and **unpacks** the netlist to its corresponding cells, nets, BELs, and wires. On design export, the sub-site data structures are **packed** back into a XDL netlist representation. Figure 2.8 shows the device data structure differences between RapidSmith and RapidSmith2. It is important to note that the initial version of RapidSmith2 still did not support Vivado designs. One of the main contributions of this thesis is to recreate the flow of Figure 2.7 using RapidSmith2 and Vivado. Since the Rapid-Smith2 data structures closely match those of Vivado, the work presented in chapter 5 builds upon the initial RapidSmith2 work.

# 2.7 Vivado Design Interface

Section 2.3 shows that Vivado's Tcl interface is not suitable for complex CAD tool development (and it was never intended for that). External tools, in languages such as C, C++, and Java, are better options for FPGA CAD researchers looking to implement new ideas and algorithms. In the past, these tools were built around Xilinx's XDL (as shown with the RapidSmith CAD framework). Because XDL is no longer supported in Vivado, a different interface to enable similar tools in the future is required.

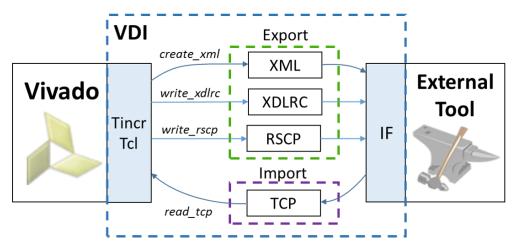

This thesis presents the **Vivado Design Interface** (VDI), the proposed XDL-alternative to support Vivado design import and export. Figure 2.9 shows the individual components of VDI, and how they interact with external CAD tools or frameworks. VDI is included with Tincr, and is available at https://github.com/byuccl/tincr. It is a significant contribution for two reasons in particular:

- 1. VDI defines a set of file formats used to externally represent Vivado devices and designs in a general, open-source way.

- 2. VDI includes Vivado Tcl code to parse and generate design and device files.

Figure 2.9: Components of the Vivado Design Interface (VDI)

VDI is meant to serve as a general-purpose interface into the Vivado design suite which can be used with *any* CAD tool or framework. Devices are represented with a XDLRC file and a set of XML files (described more in chapter 3). Designs are represented with RSCP and TCP checkpoint files (described more in chapter 4). The remaining chapters in this thesis explore specific aspects of VDI, and how they can be used to create Vivado CAD tools.

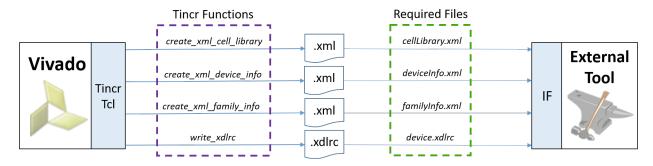

# CHAPTER 3. VDI: DEVICE EXPORT

All CAD tools targeting commercial FPGAs are built upon an external representation of the vendor's device. A placement algorithm, for example, needs to understand all valid placement locations for cells in a netlist. Similarly, a routing algorithm needs to understand all available wires and connections that can be taken when routing a net. The first goal of VDI is to create an open-source fileset capable of fully representing any Xilinx FPGA supported in Vivado. Figure 3.1 shows the proposed set of files for VDI device export, along with the newly implemented Tincr functions to generate each. There are four required VDI files to accurately represent Vivado FPGAs, which are explored throughout the remainder of this chapter.

1. XDLRC

3. Device Info XML

2. Family Info XML

4. Cell Library XML

Figure 3.1: VDI Device Files

# 3.1 XDLRC

XDLRC files are the main components of VDI device export. As described in section 2.5, they contain a detailed listing of all the physical components inside of a Xilinx FPGA. The original Tincr distribution included a command, [tincr::write\_xdlrc], capable of creating XDLRC

files for Series7 devices. This command, however, was only able to create partial device files for UltraScale and later families. **VDI supports creating complete UltraScale and UltraScale+XDLRC files**. The following subsections describe the required updates to Tincr to support Ultra-Scale XDLRC files.

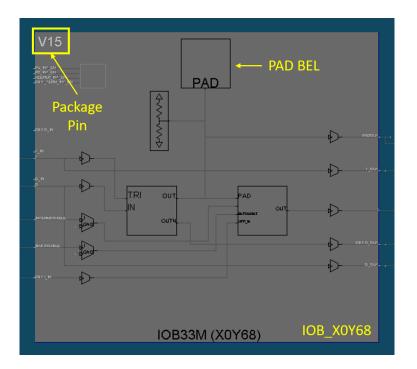

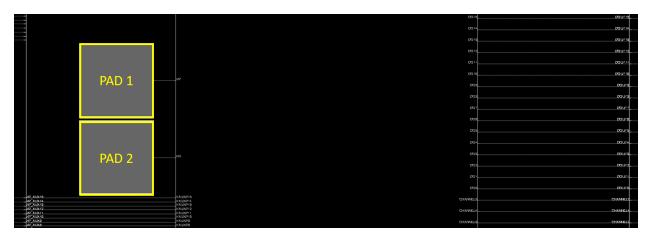

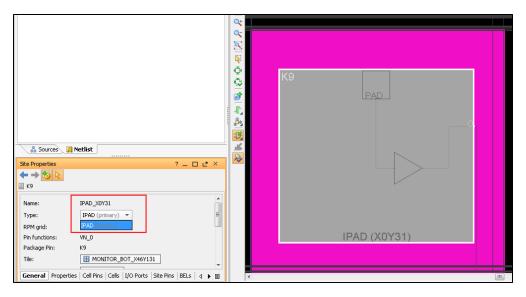

#### 3.1.1 Site PAD Names

In Series7 XDLRC files, PAD sites (that connect to an external pin on the FPGA) are named according to the corresponding package pin of the site. An example is shown in Figure 3.2 for a site of type IOB33M. For the site shown in the figure, the actual site name is "IOB\_X0Y68," but the site name reported in the XDLRC is "V15," the name of the package pin in the upper left corner.

Figure 3.2: IOB Site in Vivado's Device Browser

This naming convention assumes that there is no more than one package pin per site. Ultra-Scale devices, however, break that assumption. There are several sites that contain more than one package pin: SYSMONE1, GTHE3\_CHANNEL, GTHE3\_COMMON, GTYE3\_COMMON, and GTYE3\_CHANNEL. Figure 3.3 shows a SYSMONE1 site with two package pins.

Figure 3.3: UltraScale SYSMONE1 Package Pins

Because UltraScale and later devices have multiple package pins per site, the old naming convention for ISE XDLRC files is no longer valid. Therefore, [tincr::write\_xdlrc] now uses the actual name of PAD sites (instead of the package pin name) for UltraScale devices.

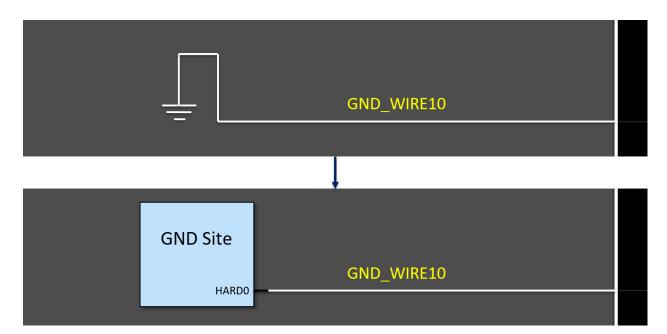

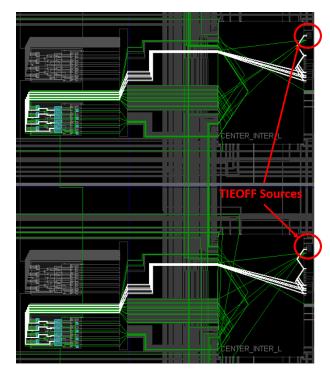

# 3.1.2 Floating VCC/GND Sources

Xilinx's Series7 architecture represents power (VCC) and ground (GND) signal sources with TIEOFF sites (as shown in Figure 3.4). To route a GND or VCC net, external tools need to simply start routing at the pin of a TIEOFF. UltraScale devices change the structure of VCC and GND sources by including "floating" VCC and GND BELs instead of TIEOFFs. The term floating refers to the fact that the VCC or GND source is not within a primitive site, but rather within the tile itself. This breaks the well-defined device hierarchy described in section 2.1 where tiles

Figure 3.4: Series7 TIEOFF

contain one or more sites and sites contain one or more BELs. To preserve the device hierarchy in UltraScale devices, [tincr::write\_xdlrc] transforms each floating BEL into a VCC or GND primitive site as shown in Figure 3.5. VCC and GND BELs can be identified in Vivado by looking for wires in the device whose name starts with either "VCC\_WIRE" or "GND\_WIRE" respectively. Listing 3.1 shows the corresponding primitive definition that is added to the XDLRC file for GND sites. A similar primitive definition is included for VCC.

Figure 3.5: UltraScale floating GND BEL (top), and the GND primitive site replacement for XDLRC files (bottom).

```

(primitive_def GND 1 2

(pin HARDO HARDO output)

(element HARDO 1

(pin HARDO input)

(conn HARDO HARDO <== HARDOGND G)

)

(element HARDOGND 1 # BEL

(pin G output)</pre>

```

```

(conn HARDOGND G ==> HARDO HARDO)

)

```

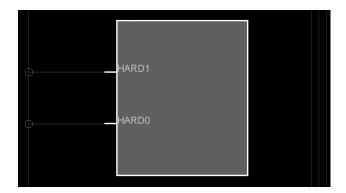

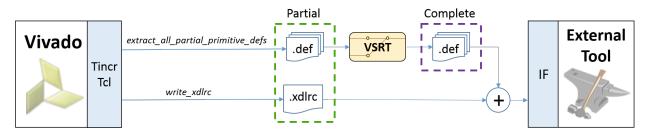

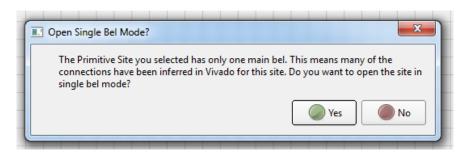

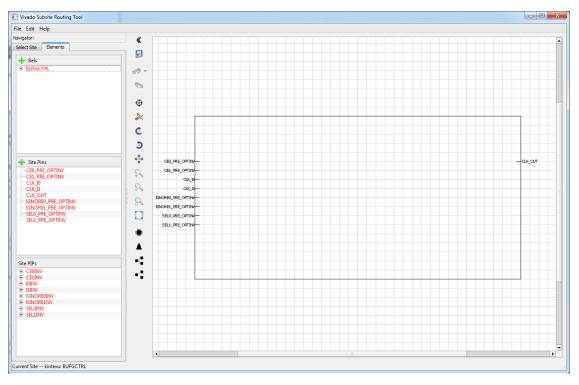

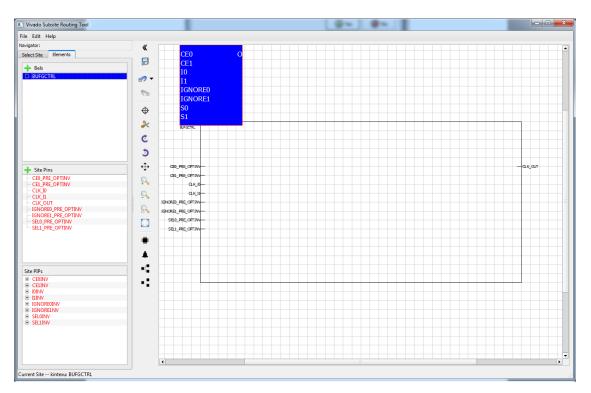

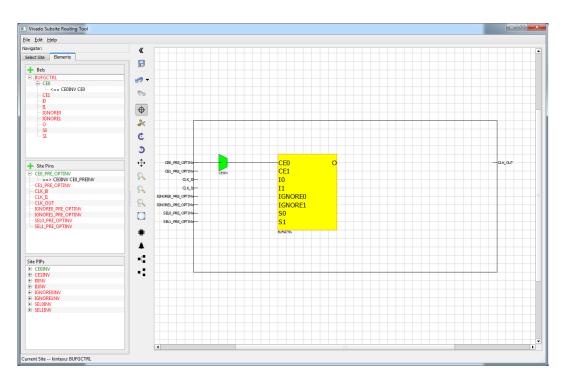

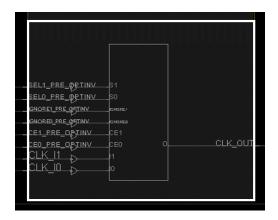

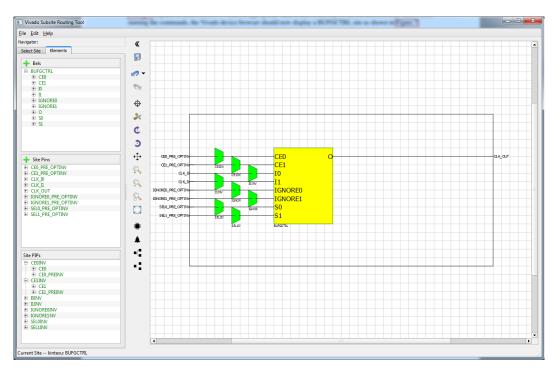

#### 3.1.3 Vivado Subsite Routing Tool

Vivado's Tcl interface provides several [get\_\*] methods which can be used to access a variety of FPGA components. Three examples used to build XDLRC files are [get\_tiles], [get\_sites], and [get\_site\_pips -of \$site]. Vivado device extraction can be largely automated due to these commands. However, there is no such function to obtain the site wires in a device. The Tcl command [get\_site\_wires] is part of the internal Xilinx namespace, meaning it is not visible to regular users. This primarily affects the **primitive definition** section of the XDLRC file, where the internal structure of each site type is defined (primitive definitions are discussed in Appendix B). Without access to site wire information, the internal routing network of sites cannot be determined automatically. The original Tincr distribution used primitive definitions from ISE to create complete Series7 device files, but this is not possible for UltraScale and later devices.

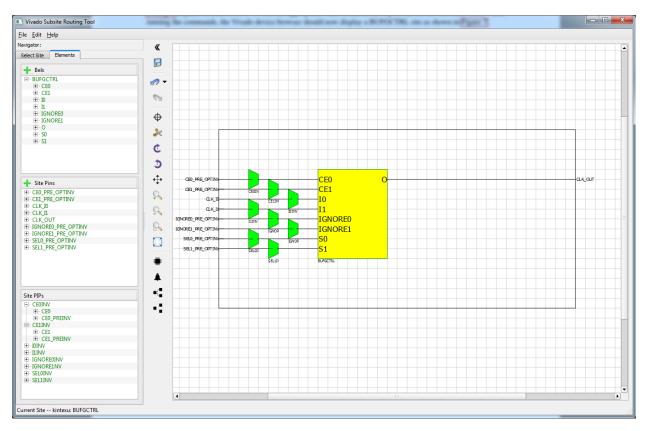

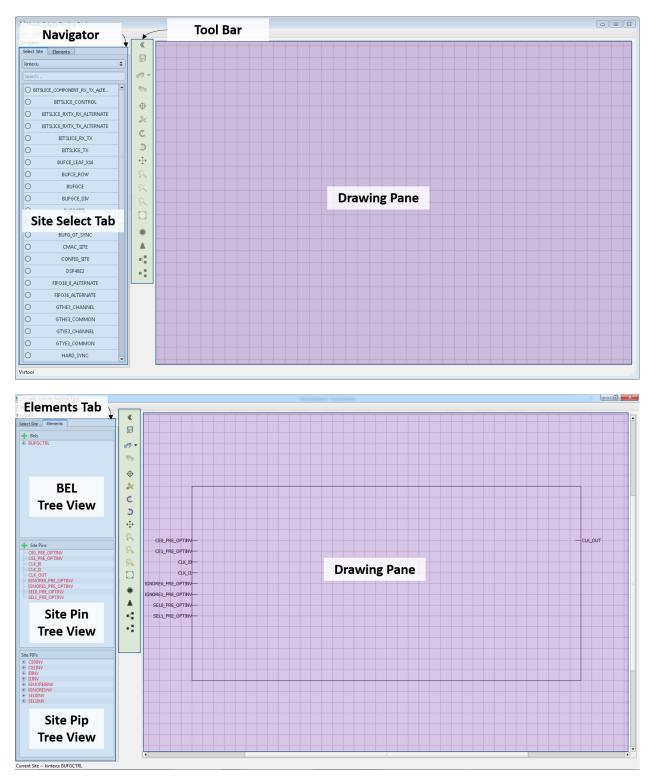

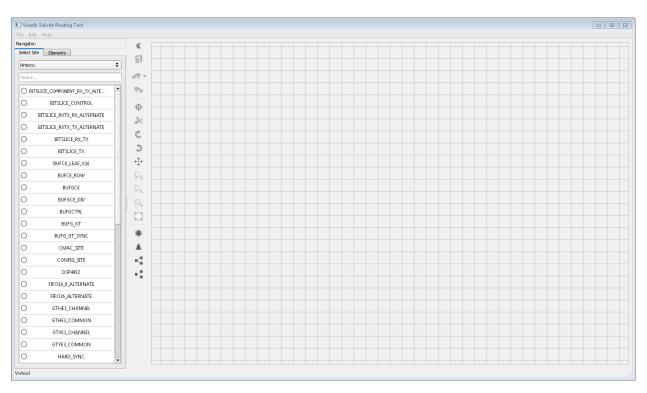

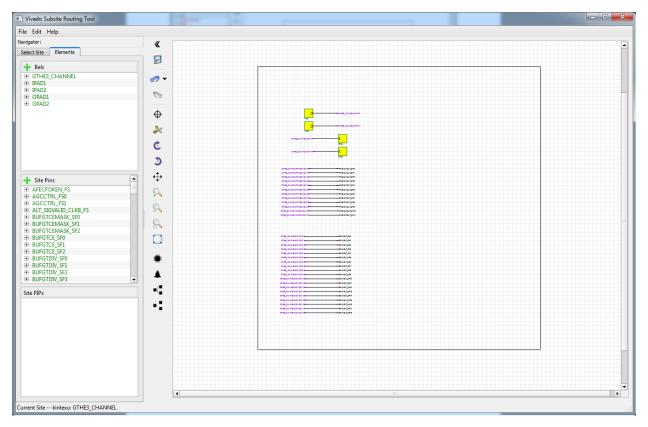

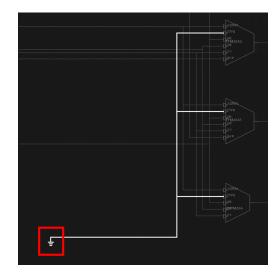

Site wires are visible in the Vivado device browser, making it theoretically possible to create the intrasite connections manually. The Vivado Subsite Routing Tool (VSRT), shown in Figure 3.6, is a GUI application developed as part of this work that helps users accomplish this task. Using VSRT a user can bring up a primitive site in both Vivado's device browser and the VSRT GUI and manually draw the site wires. Once the connections have been drawn, VSRT will generate the required primitive definition file automatically, which can be integrated with the corresponding XDLRC. It is important to note that this time-consuming process only needs to happen once for each device family (usually once per series), and many of the sites can be done automatically with little to no manual intervention.

The most significant contribution involving VSRT is a complete set of primitive definitions for UltraScale and UltraScale+ families. These primitive definitions have been added to Tincr, enabling *complete* XDLRC generation for Ultrascale and UltraScale+ devices using [ tincr::write\_xdlrc]. When future Vivado families are released, VSRT can be used to generate

Figure 3.6: Vivado Subsite Routing Tool GUI.

primitive definitions for those families as well. A very detailed user guide for VSRT is included in Appendix B.

# 3.2 Family Info XML

A *familyInfo.xml* file contains useful information that is not present in the XDLRC files for a given family of devices. Specifically, it includes the following additional information about each site type in a family:

- Alternate Types

Site PIP Corrections

- Compatible Types

- BEL Routethroughs Pin Direction Corrections

As the name suggests, only one *familyInfo.xml* is required for each of the supported Vivado families listed in Table 2.1 (all devices within a family share the same family info). A new Tincr command

has been added to generate family info files: [tincr::create\_xml\_family\_info]. Using this command, with a few required hand edits, a complete set of family info XML files have been created for all Series7 and UltraScale families. The following subsections describe (a) how the Vivado Tcl interface is used to generate a family info file (and the necessary hand edits for Series7 devices), and (b) a description of each of the items in the above list, and why they may be useful for external CAD tools.

# 3.2.1 Algorithm

The pseudocode for the family info generation script in Tincr is given in algorithm 1.

| Alg | orithm 1 Family Info Generation                                           |                                     |

|-----|---------------------------------------------------------------------------|-------------------------------------|

| 1:  | <b>procedure</b> CREATE_XML_FAMILY_INFO( <i>family</i> , <i>fileout</i> ) |                                     |

| 2:  | $unique\_devices \leftarrow get\_unique\_devices(family)$                 | ▷ Ignore device speedgrade          |

| 3:  | processed types $\leftarrow \varnothing$                                  | ▷ Create an empty set of site types |

| 4:  | for each $device \in unique\_devices$ do                                  |                                     |

| 5:  | open_device_in_vivado(device)                                             |                                     |

| 6:  | $unique\_sites \leftarrow get\_unique\_sites(device)$                     |                                     |

| 7:  | for each site $\in$ unique_sites do                                       |                                     |

| 8:  | $site\_type \leftarrow get\_type(site)$                                   |                                     |

| 9:  | <b>if</b> site_type ∉ processed_types <b>then</b>                         |                                     |

| 10: | <pre>print_xml(site, fileout)</pre>                                       |                                     |

| 11: | $processed\_types \leftarrow processed\_types \cup site$ .                | type                                |

| 12: | end if                                                                    |                                     |

| 13: | end for                                                                   |                                     |

| 14: | close_device_in_vivado(device)                                            |                                     |

| 15: | end for                                                                   |                                     |

| 16: | end procedure                                                             |                                     |

As can be seen, the first step of the algorithm is to find a set of unique devices for the specified family. A device is considered unique based on its part number and package type only (i.e. the speed grade is ignored). For example, the two parts xcku025-ffva1156-1-c and xcku025-ffva1156-2-c are **not** considered unique, and only one would be used during the generation process. The Tcl regular expression

is used to remove the speed-grade from a complete part name when filtering for unique devices. Once a set of unique devices is created, each device is loaded into Vivado where a list of site types in the device is determined. Since all parts across a family are identical, every site type in a family is only processed one time. Using Vivado Tcl commands, an instance of each site type is analyzed to determine the relevant information for the family info file, which is formatted into XML. It is important to note that the site type must be manually set for alternate-only types before processing the site.

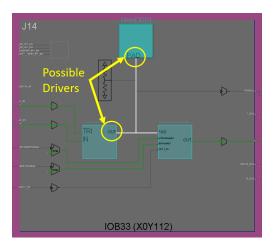

### 3.2.2 Alternate Types

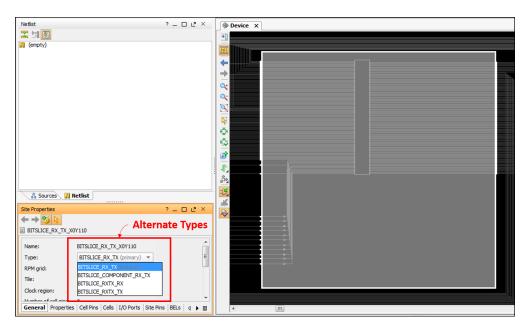

Each physical site in a device has an associated default type. Some sites, however, can be configured to be one of many types (called alternate types in Vivado). Alternate type information is required for external CAD tools because the type of a site can be changed during the placement phase of implementation. To accurately represent a placed design in an external tool, site types need to be changeable. An example of alternate types for an UltraScale BITSLICE\_RX\_TX site is shown in Figure 3.7. As the figure shows, a BITSLICE\_RX\_TX site can also be configured to be of type BITSLICE\_COMPONENT\_RX\_TX, BITSLICE\_RXTX\_RX, or BITSLICE\_RXTX\_TX.

Figure 3.7: BITSLICE\_RX\_TX Alternate Types

Figure 3.8: IPAD Alternate Types (there are none)

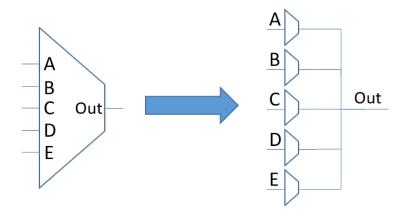

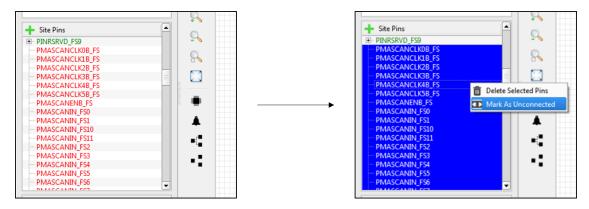

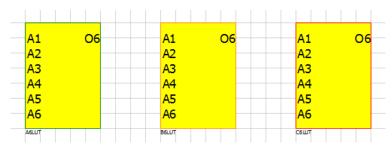

The alternate types of a given site can be determined in Vivado with the Tcl command [get\_property ALTERNATE\_SITE\_TYPES \$site]. The results returned from this command are always correct for UltraScale and UltraScale+ devices, but they can be incorrect for Series7 devices. That is, certain sites can return invalid alternate types through the Tcl interface. For example, a site of type IPAD returns four alternate types: IOB18M, IOB18S, IOB33M, and IOB33S. None of these types are valid alternates, as shown in Figure 3.8. It is difficult to detect invalid alternate types because setting a site to an invalid type and then querying its components can cause Vivado to crash. Therefore, it is the user's responsibility to manually remove the invalid alternate types from the family info file by looking at the correct alternate types in the Vivado GUI as shown in Figure 3.7.

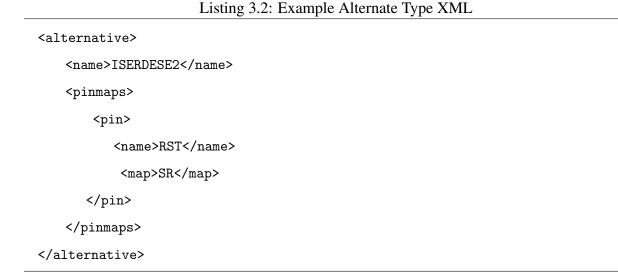

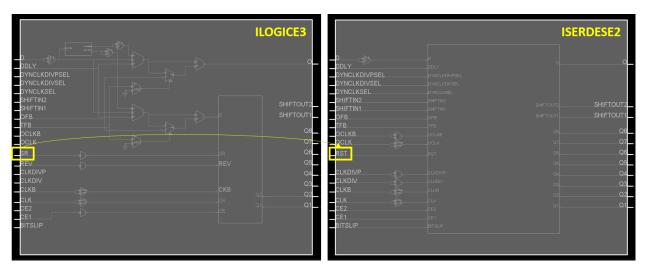

Listing 3.2 shows how alternate types are represented in a family info XML. As can be seen in the XML, a series of "pinmap" tags are included for each alternate type. This is because when a site type is changed to one of its alternates, some site pins can be renamed (again, this is only true for Series7 devices). An example is shown in Figure 3.9. When an ILOGICE3 site is changed to be of type ISERDESE2, the SR pin is renamed to RST. Unfortunately, the renaming cannot be determined automatically because the Tcl command [get\_site\_pins -of \$site] will always return the site pins attached to the **default type** of a site. Due to this Vivado bug, users must manually determine pin mappings using the Vivado GUI.

Figure 3.9: Example Alternate Site Pin Renaming

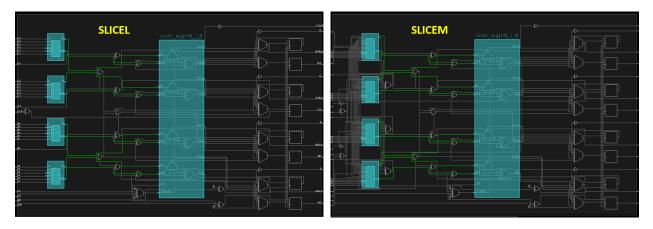

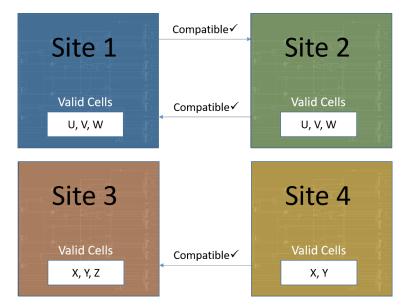

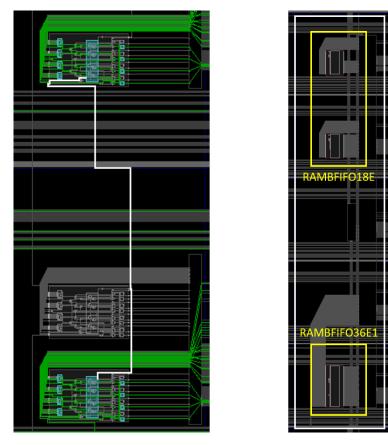

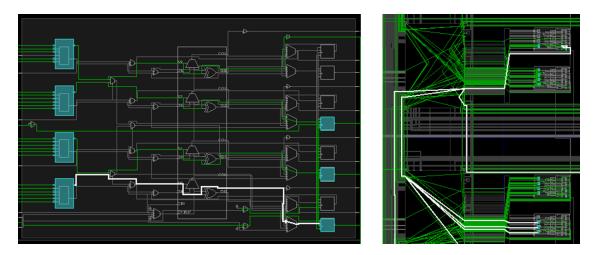

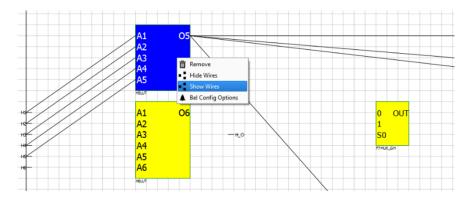

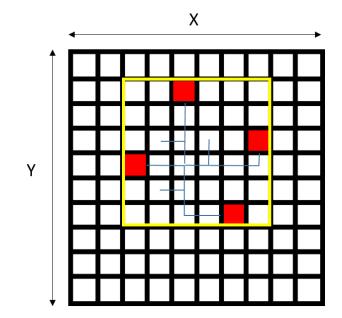

# 3.2.3 Compatible Types

Site A is said to be compatible with site B if the logical cells placed on site A can *always* be placed on site B as well. For example, as shown in Figure 3.10, SLICEL sites are compatible with SLICEM sites. The cells placed on the SLICEL in the figure can be moved to the SLICEM and still function identically. SLICEMs, however, are *not* compatible with SLICELs. This is because SLICEM sites support LUT RAM cells, which cannot be placed on SLICEL sites. In some cases of compatibility, the type of the compatible site must first be changed before placing cells on it.

Figure 3.10: A group of cells placed on a SLICEL site (left) and a SLICEM site (right).

For instance, a RAMB36 site is compatible with a RAMBFIFO36 site, but the site type of the RAMBFIFO36 **must first be changed to RAMB36** before it is truly compatible.