Brigham Young University BYU ScholarsArchive

All Theses and Dissertations

2017-04-01

# Using On-Chip Error Detection to Estimate FPGA Design Sensitivity to Configuration Upsets

Andrew Mark Keller Brigham Young University

Follow this and additional works at: https://scholarsarchive.byu.edu/etd Part of the <u>Electrical and Computer Engineering Commons</u>

BYU ScholarsArchive Citation

Keller, Andrew Mark, "Using On-Chip Error Detection to Estimate FPGA Design Sensitivity to Configuration Upsets" (2017). *All Theses and Dissertations*. 6302. https://scholarsarchive.byu.edu/etd/6302

This Thesis is brought to you for free and open access by BYU ScholarsArchive. It has been accepted for inclusion in All Theses and Dissertations by an authorized administrator of BYU ScholarsArchive. For more information, please contact scholarsarchive@byu.edu, ellen\_amatangelo@byu.edu.

Using On-Chip Error Detection to Estimate FPGA

Design Sensitivity to Configuration Upsets

Andrew Mark Keller

A thesis submitted to the faculty of Brigham Young University in partial fulfillment of the requirements for the degree of

Master of Science

Michael J. Wirthlin, Chair James K. Archibald Brent E. Nelson

Department of Electrical and Computer Engineering

Brigham Young University

Copyright © 2017 Andrew Mark Keller

All Rights Reserved

# ABSTRACT

# Using On-Chip Error Detection to Estimate FPGA Design Sensitivity to Configuration Upsets

Andrew Mark Keller Department of Electrical and Computer Engineering, BYU Master of Science

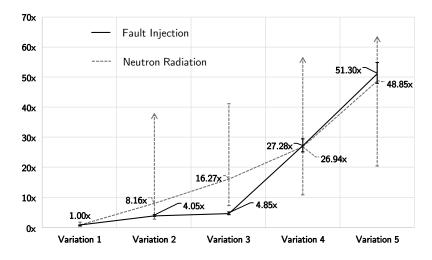

SRAM-based FPGAs provide valuable computation resources and reconfigurability; however, ionizing radiation can cause designs operating on these devices to fail. The sensitivity of an FPGA design to configuration upsets, or its SEU sensitivity, is an indication of a design's failure rate. SEU mitigation techniques can reduce the SEU sensitivity of FPGA designs in harsh radiation environments. The reliability benefits of these techniques must be determined before they can be used in mission-critical applications and can be determined by comparing the SEU sensitivity of an FPGA design with and without these techniques applied to it. Many approaches can be taken to evaluate the SEU sensitivity of an FPGA design. This work describes a low-cost easierto-implement approach for evaluating the SEU sensitivity of an FPGA design. This approach uses additional logic resources on the same FPGA as the design under test to determine when the design has failed, or deviated from its specified behavior. Three SEU mitigation techniques were evaluated using this approach: triple modular redundancy (TMR), configuration scrubbing, and user-memory scrubbing. Significant reduction in SEU sensitivity is demonstrated through fault injection and radiation testing. Two LEON3 processors operating in lockstep are compared against each other using on-chip error detection logic on the same FPGA. The design SEU sensitivity is reduced by  $27 \times$  when TMR and configuration scrubbing are applied, and by approximately  $50 \times$ when TMR, configuration scrubbing, and user-memory scrubbing are applied together. Using this approach, an SEU sensitivity comparison is made of designs implemented on both an Altera Stratix V FPGA and a Xilinx Kintex 7 FPGA. Several instances of a finite state machine are compared against each other and a set of golden output vectors, all on the same FPGA. Instances of an AES cryptography core are chained together and the output of two chains are compared using on-chip error detection. Fault injection and neutron radiation testing reveal several similarities between the two FPGA architectures. SEU mitigation techniques reduce the SEU sensitivity of the two designs between  $4 \times$  and  $728 \times$ . Protecting on-chip functional error detection logic with TMR and duplication with compare (DWC) is compared. Fault injection results suggest that it is more favorable to protect on-chip functional error detection logic with DWC than it is to protect it with TMR for error detection.

Keywords: FPGA, SEU mitigation, SEU sensitivity, reliability, error detection, triple modular redundancy, TMR, duplication with compare, DWC, scrubbing, fault-tolerance, neutron radiation testing, fault-injection

#### ACKNOWLEDGMENTS

I would like to thank all those who have made this thesis possible. I could not have accomplished this work without the support and encouragement of all of the invested professors, organizations, colleagues, family, and friends. Their contributions have been invaluable.

My advisor, Dr. Michael Wirthlin, has been instrumental in guiding me through my research and opening the windows of opportunity to advance this work. I am honored that he would entrust this work to me. His encouragement and enthusiasm inspire me.

I am grateful to the other members of my graduate committee, Dr. Brent Nelson and Dr. James Archibald, for their support and for the knowledge and experience they have helped me gain. I am also thankful for the advice and tutelage of Dr. Brad Hutchings, Dr. Doran Wilde, Dr. D. J. Lee, and the other faculty and staff members who have helped me along the way.

This work could not have been done without collaborating with colleagues outside of the BYU Configurable Computing Lab (CCL). I would like to thank Rick Wong and Shi-Jie Wen from Cisco, David S. Lee from Sandia National Laboratories, Heather Quinn from Los Alamos National Laboratories, Mike Hutton from the Intel Programmable Solutions Group, and Paul J. Vincent and Matthew Noell from Raytheon for all of their support and contributions.

My family has been an unwavering support throughout my journey. I would like to thank my wife, Beth, for her love and patience with "robot soccer close," and my daughter, Hailey Anne, for the joy she is to me. My parents and siblings have also been great supports.

The other students in the BYU CCL have also helped me progress in my education and research. Specifically I would also like to thank Aaron Stoddard, Ammon Gruwell, Parker Ridd, Chase McCloskey, James Swift, Hayden Rowberry, Tim Whiting, and Ken Sawyer.

This work supported by the Los Alamos Neutron Science Center (LANCSE) which provided neutron beam time under proposal NS-2016-7268-F. This work was also supported by the I/UCRC Program of the National Science Foundation under Grant No. 1265957 through the NSF Center for High-Performance Reconfigurable Computing (CHREC) and by Cisco Systems, Inc.

| LIST O  | F TABLES                                                   | ii |

|---------|------------------------------------------------------------|----|

| LIST O  | F FIGURES                                                  | ii |

| Chapter | 1 Introduction                                             | 1  |

| 1.1     | Thesis Contributions                                       | 4  |

| Chapter | <b>FPGA Configuration Upsets and Mitigation Techniques</b> | 5  |

| 2.1     | Radiation Sources                                          | 6  |

| 2.2     | Radiation Effects                                          | 7  |

|         | 2.2.1 Single Event Effects                                 | 8  |

| 2.3     |                                                            | 9  |

| 2.4     | Reliability: Faults, Errors and Failures                   | 2  |

| 2.5     |                                                            | 4  |

|         |                                                            | 4  |

|         |                                                            | 6  |

|         |                                                            | 6  |

|         |                                                            | 7  |

|         |                                                            | 8  |

| 2.6     |                                                            | 9  |

| Chapter | 3 SEU Sensitivity Testing Approaches                       | 1  |

| 3.1     |                                                            | 1  |

| 3.2     |                                                            | 3  |

| 3.3     | SEU Sensitivity Testing Examples                           |    |

| 5.5     | 3.3.1 FT-UNSHADES                                          |    |

|         | 3.3.2 FLIPPER                                              |    |

|         | 3.3.3 SLAAC-1V                                             |    |

|         |                                                            | 0  |

|         |                                                            |    |

| 2.4     |                                                            |    |

| 3.4     | Motivation for an On-Chip Error Detection Approach         | 3  |

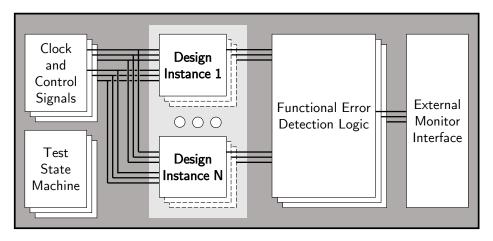

| Chapter | C4 On-Chip Error Detection Approach                        | 5  |

| 4.1     | Clocking and Control Signals                               | 5  |

| 4.2     | Test State Machine                                         | 7  |

| 4.3     | Design Instances                                           | 8  |

| 4.4     | Functional Error Detection                                 | 0  |

|         | 4.4.1 Signal Selection                                     | 0  |

|         | 4.4.2 Comparison Schemes                                   | 1  |

|         | 4.4.3 Functional Error Detection Mechanisms                | 2  |

| 4.5     | External Monitor Interface                                 | 2  |

| 4.6     |                                                            | 3  |

# TABLE OF CONTENTS

| 4.7         | Minimal Influence on Results                                    | 45 |

|-------------|-----------------------------------------------------------------|----|

| 4.8         | On-Chip Error Detection Benchmark Design Testing                | 46 |

|             | 4.8.1 LEON3 Soft Processor                                      |    |

|             | 4.8.2 ITC'99 B13 Benchmark Design                               |    |

|             | 4.8.3 128-bit AES Cryptography Core                             | 49 |

| 4.9         | SEU Estimation Through Fault Injection and Radiation Testing    |    |

|             |                                                                 |    |

| Chapter     | r 5 Fault Injection                                             | 51 |

| 5.1         | Approach                                                        | 51 |

| 5.2         | Metrics                                                         |    |

| 5.3         | LEON3 Xilinx Results                                            | 55 |

| 5.4         | B13 Altera Results                                              | 57 |

|             | 5.4.1 Comparison of a Simple DUT and the B13                    | 58 |

| 5.5         | B13 Xilinx Results                                              |    |

| 5.6         | AES Altera Results                                              |    |

| 5.7         | AES Xilinx Results                                              |    |

| 5.8         | Comparison of Fault Injection Results on Two FPGA Architectures |    |

|             |                                                                 |    |

| Chapter     | r 6 Radiation testing                                           | 68 |

| 6.1         | Approach                                                        | 68 |

| 6.2         | Metrics                                                         |    |

| 6.3         | LEON3 Xilinx Results                                            |    |

| 6.4         | B13 Xilinx Results                                              |    |

|             | 6.4.1 Comparison to Other Mitigation Techniques                 |    |

| 6.5         | B13 and AES on Two Different FPGA Architectures                 |    |

|             | 6.5.1 Comparison of Device Cross Section                        |    |

| 6.6         | Comparison to Fault Injection Results                           |    |

|             | 1 5                                                             |    |

| Chapter     | r7 Conclusion                                                   | 79 |

|             |                                                                 |    |

| REFER       | ENCES                                                           | 82 |

|             |                                                                 |    |

| Append      | lix A Details on the Benchmark Designs Used                     | 87 |

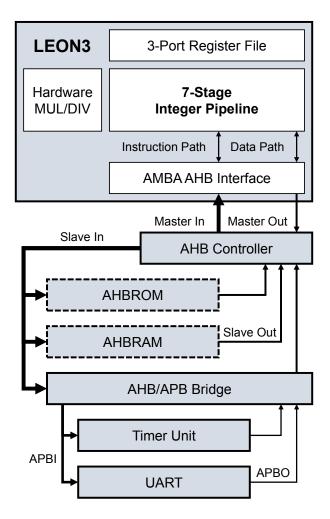

| A.1         | LEON3                                                           | 87 |

| A.2         | Test Fixture                                                    | 88 |

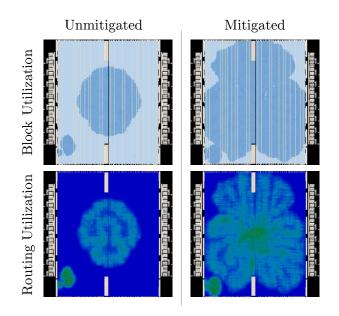

| A.3         | Resource Utilization                                            | 89 |

| A.4         | ITC'99 B13 Benchmark Design                                     | 90 |

|             | A.4.1 Test Fixture                                              | 90 |

| A.5         | Resource Utilization                                            | 91 |

| A.6         | AES 128-bit Cryptography IP Core                                | 93 |

| A.7         | Test Fixture                                                    | 93 |

| A.8         | Resource Utilization                                            | 94 |

|             |                                                                 |    |

| Append      | ix B Fault Injection and Radiation Testing Logs                 | 96 |

| <b>B</b> .1 | Altera Fault Injection                                          | 96 |

| B.2         | Xilinx Fault Injection           | 97  |

|-------------|----------------------------------|-----|

|             | Altera Neutron Radiation Testing |     |

| <b>B</b> .4 | Xilinx Neutron Radiation Testing | 101 |

# LIST OF TABLES

| 5.1 | LEON3 Xilinx Fault Injection Results                              | 56 |

|-----|-------------------------------------------------------------------|----|

| 5.2 | B13 Altera Fault Injection Results                                | 58 |

| 5.3 |                                                                   | 59 |

| 5.4 | Normalized Simple DUT and B13 Comparison Fault Injection Results  | 60 |

| 5.5 | B13 Xilinx Fault Injection Results                                | 61 |

| 5.6 | AES Altera Fault Injection Results                                | 62 |

| 5.7 | AES Xilinx Fault Injection Results                                | 64 |

| 5.8 | Comparison of Fault Injection Data                                | 66 |

| 6.1 | Neutron Radiation Data                                            | 71 |

| 6.2 | Comparison of Fault Injection and Neutron Radiation Testing       | 73 |

| 6.3 | B13 Neutron Radiation Results                                     | 75 |

| 6.4 | Neutron Cross Section Comparison of Mitigation Techniques         | 76 |

| 6.5 | Neutron Radiation Results                                         | 77 |

| 6.6 | Device Neutron Radiation Data                                     | 78 |

| A.1 | LEON3 Design Variation Resource Utilization                       | 89 |

| A.2 | Single B13 Implementation on a Xilinx Kintex-7 FPGA               | 91 |

| A.3 | Implementation of 512 B13 copies on a Xilinx Kintex-7 FPGA        | 92 |

| A.4 | Implementation of 512 B13 copies on an Altera Stratix V FPGA      | 93 |

| A.5 | AES Test Fixture Resource Utilization on an Xilinx Kintex 7 FPGA  | 94 |

| A.6 | AES Test Fixture Resource Utilization on an Altera Stratix V FPGA | 95 |

# LIST OF FIGURES

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> <li>2.9</li> </ol> | Funneling Phenomenon in a N-type MOSFETAn SEU within an SRAM-cellIsland-style FPGA Architecture LayoutBasic FPGA Design FlowSEU Failure ModesSEU Routing Failure ModesTriple Modular Redundancy (TMR).Fine-grain TMR with Voter Synchronization in the Feedback PathInternal BRAM Scrubbing | 8<br>9<br>10<br>11<br>12<br>12<br>15<br>15<br>15<br>18 |

|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                                                          | General Setup for SEU Sensitivity Test.FT-UNSHADES Test Setup.FLIPPER test fixture.SLAAC-1V Setup Diagram.XRTC-V5FI Test Fixture.Multiple Development Board Test Setup.                                                                                                                     | 24<br>26<br>28<br>29<br>31<br>32                       |

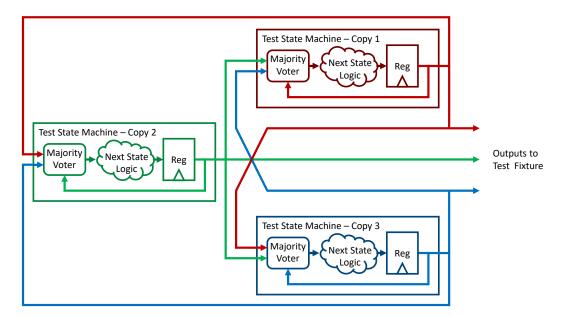

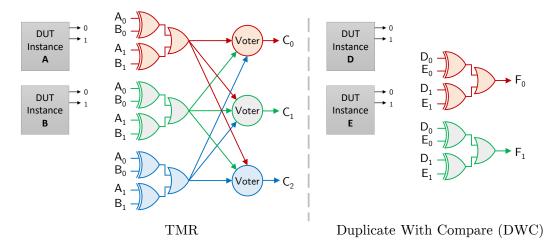

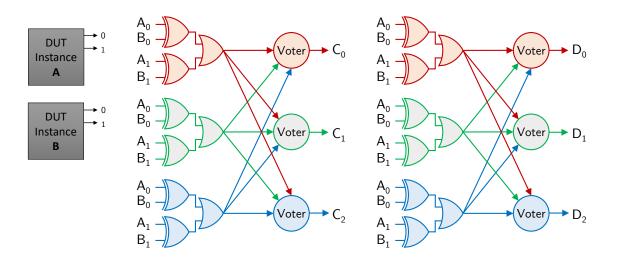

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5                                                                                                 | Components of On-Chip Error DetectionTest State Machine with TMR AppliedTMR Protected and DWC Protected Functional Error Detection MechanismsFalse-Positive BiasMinimum Influence on Results                                                                                                | 36<br>39<br>43<br>44<br>45                             |

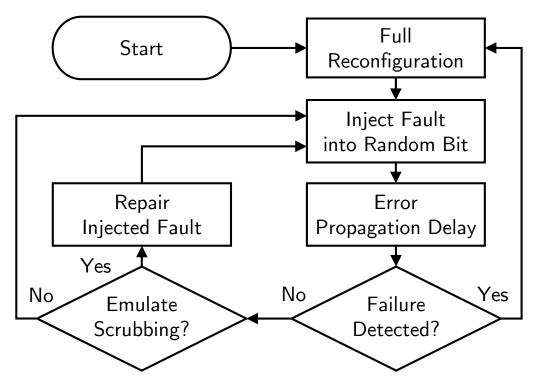

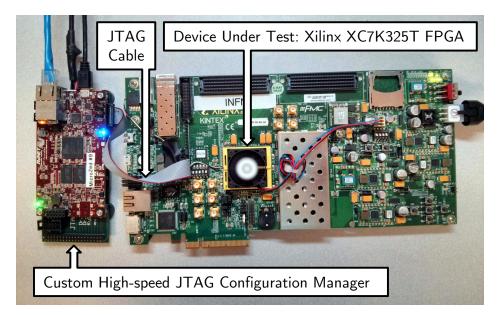

| 5.1<br>5.2<br>5.3                                                                                                               | Fault Injection FlowchartFault Injection Setup for a Xilinx FPGATMR and DWC Protected Function Error Detection MechanismFault Injection                                                                                                                                                     | 53<br>54<br>64                                         |

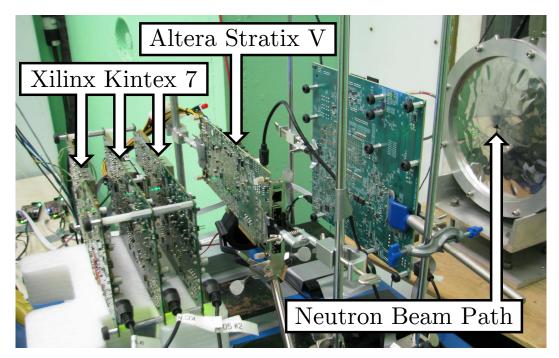

| 6.1<br>6.2                                                                                                                      | Neutron Beam Test SetupSetupSEU Sensitivity Improvement for Each Design Variation                                                                                                                                                                                                           | 69<br>74                                               |

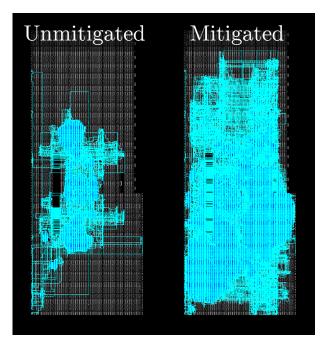

| A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6<br>A.7<br>A.8<br>A.9                                                                     | LEON3 System Architecture Under Test                                                                                                                                                                                                                                                        |                                                        |

# CHAPTER 1. INTRODUCTION

SRAM-based field programmable gate arrays (FPGA) are being used increasingly in terrestrial [1] and space-based applications [2]. Modern FPGAs provide large amounts of programmable logic, computation resources, I/O, memory and special-purpose functionality. As FPGAs are released on new technology, they are able to provide this functionality at lower power and operating frequencies. FPGAs are also increasingly integrating dedicated, hardened IP to provide a mix of fixed function and programmable function solutions. Their reconfigurability and low overhead for design development make them an attractive alternative to application-specific integrated circuits (ASIC).

Because SRAM-based FPGAs use a large set of static configuration memory cells (CRAM) to support programmability, designs operating on SRAM-based FPGAs are susceptible to failure induced by ionizing radiation. The value stored in an SRAM memory cell can be inverted by the passing of a single energetic atomic particle through the device. This is known as a single event upset (SEU) [3–5]. SEUs are troublesome for SRAM-based FPGA designs because an upset in configuration memory could alter the behavior of logic, routing, or other utilized resources. These alterations could cause the design to fail, or deviate from its defined behavior. Ionizing radiation is a great concern for FPGA applications in harsh radiation environments like space and high-energy physics experiments, and it is a growing concern for FPGA applications in terrestrial environments [6,7].

The susceptibility of an FPGA design to failure caused by SEUs in configuration memory is discussed throughout this thesis in terms of SEU sensitivity. SEU sensitivity is defined as how prone to failure a given design is when a random SEU occurs. It is not guaranteed that an SEU will cause a design operating on an SRAM-based to fail [8]. An SEU may occur in an unused portion of the FPGA or be masked in such a way that it does not affect the correct behavior of the design. Or it may alter the design and lead to failure [23, 24]. The likelihood of a random SEU causing a

design to fail determines SEU sensitivity. The more likely a random SEU is to cause failure, the more *sensitive* the design.

Much research has been done to develop SEU mitigation techniques for SRAM-based FP-GAs [9–12], which reduce SEU sensitivity. These techniques include structural redundancy such as: triple modular redundancy (TMR), duplication with compare (DWC), and state machine encoding. While expensive from a resource perspective, these techniques can greatly improve the reliability of a design [13]. Configuration scrubbing is also employed to rapidly repair upsets and prevent the accumulation of upsets in configuration memory [14].

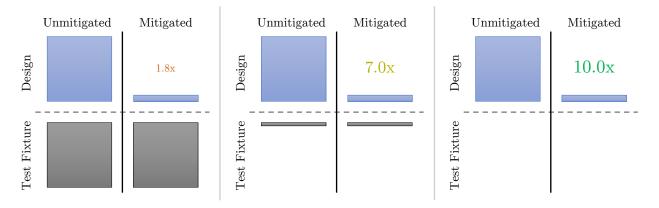

An improvement in reliability or a reduction in SEU sensitivity of an FPGA design is referred to throughout this thesis as a ratio between the SEU sensitivity of the design without SEU mitigation and with SEU mitigation techniques applied. An improvement in reliability and a reduction in sensitivity are synonymous. For example, a  $4 \times$  improvement in reliability or a  $4 \times$  reduction in SEU sensitivity means that there is a 4:1 SEU sensitivity ratio between the unmitigated and mitigated version of an FPGA design respectively.

The SEU sensitivity of an FPGA design plays an important part in advancing the state of the art in FPGA reliability. Knowing the SEU sensitivity of a particular design can help identify what causes FPGA designs to be sensitive to SEUs. The impact of changes in the fabrication process, architecture, and applied SEU mitigation techniques can all be better understood through comparing the SEU sensitivity of various designs. SEU mitigation techniques can be validated and additional vulnerabilities discovered through the SEU sensitivity of an FPGA design.

The SEU sensitivity of an FPGA design is typically evaluated through fault injection and radiation testing. Fault injection is the process of artificially introducing a fault and observing the response. The type of fault injection referred to in this work involves mimicking the behavior of an SEU in an FPGA [15]. Radiation testing is the process of exposing the FPGA design to an accelerated radiation source and observing the response. Several types of radiation used for SEU sensitivity testing include: proton, neutron, and heavy ions [16]. SEU sensitivity is measured in this work by the percentage of injected faults that caused a failure for fault injection and by the design cross section for radiation testing.

Many test setups can be used to evaluate the SEU sensitivity of an FPGA design through fault injection or radiation testing. SEU sensitivity testing is event based, where the event is the

occurrence of a functional failure. Most SEU sensitivity testing approaches depend on the ability to detect when a functional failure has occurred. Typically, input stimulus is provided to the design under test and its outputs are compared against a known *golden* value to detect failures. Most SEU sensitivity testing approaches separate error detection logic from the device being tested. These *off-chip* error detection approaches sometimes involve creating custom test boards that use multiple FPGAs.

An on-chip error detection approach provides a cost effective means for rapidly evaluating the SEU sensitivity of an FPGA design. Implementing *off-chip* error detection can be expensive and time consuming. This thesis presents an *on-chip* error detection evaluation approach that is low-cost and easier to implement. This approach uses additional logic resources on the same FPGA as the design under test to determine when the design has failed, or deviated from its specified behavior. Although the error detection circuitry is also vulnerable to failure, valuable information about the SEU sensitivity of a design can still be obtained using this approach. To improve accuracy, SEU mitigation techniques are always applied to the on-chip error detection circuitry. This thesis describes the benefits and limitations of this approach as compared to those of other SEU sensitivity evaluation approaches.

Using an on-chip error detection approach, the reliability benefits of three SEU mitigation techniques are evaluated: TMR, configuration scrubbing, and user-memory scrubbing. Two LEON3 processors operating in lockstep are compared against each other using on-chip error detection logic on the same FPGA. The design SEU sensitivity is reduced by  $27 \times$  when TMR and configuration scrubbing are applied; and by approximately  $50 \times$  reduction when TMR, configuration scrubbing, and user-memory scrubbing are applied together. Using this approach, an SEU sensitivity comparison is made of designs implemented on both an Altera Stratix V FPGA and a Xilinx Kintex 7 FPGA. Several instances of a finite state machine are compared against each other and a set of golden output vectors, all on the same FPGA. Instances of an AES cryptography core are chained together and the output of two chains are compared using on-chip error detection. Fault injection and neutron radiation testing reveal several similarities between the two FPGA architectures. SEU mitigation techniques reduce the SEU sensitivity of the two designs between  $4 \times$ and  $728 \times$ . Protecting on-chip functional error detection logic with TMR and DWC is compared. Fault injection results suggest that it is more favorable to protect on-chip functional error detection logic with DWC than it is to protect it with TMR for error detection.

#### **1.1 Thesis Contributions**

This thesis presents an approach for evaluating the SEU sensitivity of a design using onchip error detection. The advantages and disadvantages of many evaluation approaches are discussed, including those of on-chip error detection and other evaluation approaches used in related works. A generalized composition of an on-chip error detection test fixture is presented and important aspects of on-chip error detection are covered. The importance of evaluating SEU sensitivity and a comparison of various evaluation approaches is discussed in Chapter 3. On-chip error detection concepts and test fixture composition is covered in Chapter 4.

The work presented in this thesis uses on-chip error detection to evaluate the SEU sensitivity of several FPGA designs through fault injection and radiation testing. Unmitigated and mitigated FPGA designs were evaluated on a Xilinx Kintex 7 FPGA and an Altera Stratix V FPGA. Three SEU mitigation techniques were included in this study: TMR, configuration scrubbing, and user memory scrubbing. Various integrations of theses techniques were evaluated, by only applying TMR to mitigate a design, or applying TMR with user-memory scrubbing and no configuration scrubbing, etc. A LEON3 soft processor, a finite state machine, and a 128-bit AES cryptography core were used as benchmark designs. A variety of on-chip error detection schemes and mechanisms were used to evaluate SEU sensitivity.

From the results, three main comparisons are made. First, the reliability benefits of various mitigation schemes are compared, demonstrating the complementary nature of SEU mitigation techniques. Second, the SEU sensitivity of FPGA designs across two different architectures are compared, that of an Altera Stratix V FPGA and that of a Xilinx Kintex 7 FPGA. Finally, SEU sensitivity results obtained from fault injection are used to compare TMR protected and DWC protected on-chip error detection logic.

# CHAPTER 2. FPGA CONFIGURATION UPSETS AND MITIGATION TECHNIQUES

SRAM-based FPGAs, like application specific integrated circuits (ASICs), are susceptible to radiation induced failures; fortunately, many mitigation techniques have been developed to improve the reliability of these devices in spite of their vulnerabilities [2]. Most radiation induced failures in these devices result from non-permanent, soft errors that can be prevented, masked, or recovered from. Radiation effects observed in an FPGA may or may not cause the design operating on the FPGA to cease functioning correctly. In developing SEU mitigation techniques and preparing designs for use on commercial FPGAs in harsh radiation environments, it is important to understand where radiation comes from, how it effects FPGA designs, and what can done to improve the robustness of a design.

This chapter motivates the need for evaluating the effects of configuration upsets on FPGA designs. Configuration upsets are caused by ionizing radiation, which is present in space and terrestrial environments. Ionizing radiation can come from galactic cosmic rays or impurities in packing materials. This radiation can cause FPGA designs to fail, or deviate from their specified behavior. These failures are difficult to reproduce and are becoming a greater issue as features sizes shrink and more FPGAs are being deployed in data centers and Internet core routers [1, 17]. SEU mitigation techniques can be applied to FPGA designs to make them less sensitive to configuration upsets. This chapter discusses radiation sources, FPGA architecture, and SEU mitigation techniques. It provides the background information necessary to fully appreciate the purpose and challenges behind SEU sensitivity evaluation, and motivates the need for using the proposed on-chip error detection approach to evaluate the SEU sensitivity of an FPGA design.

In this thesis, on-chip error detection is used to evaluate the SEU sensitivity of various FPGA designs. Fault injection and radiation beam testing are used to simulate and cause SEUs in FPGA configuration memory. Specific bits that cause the design to fail are observed and the overall sensitivity of the design to configuration upsets is determined. Unmitigated and SEU mitigated FPGA designs are evaluated on an Altera Stratix V and a Xilinx Kintex 7 FPGA. The SEU mitigation techniques evaluated are: TMR, configuration scrubbing, and user-memory scrubbing. The collected SEU sensitivity data assists in understanding the effects of radiation on FPGA designs and the benefits of SEU mitigation techniques.

## 2.1 Radiation Sources

FPGAs are exposed to radiation present in their operating environments. FPGAs are deployed in a number of applications including terrestrial and space based applications. In terrestrial environments, there are three main sources of fault-inducing radiation: alpha particles, high-energy cosmic rays and thermal neutrons [18]. These radiation sources pose a threat to FPGA reliability in terrestrial [6, 7] and space environments. Other sources of radiation in space environments include: trapped protons, galactic cosmic rays (GCRs), and heavy ions [19]. The primary concern is making sure that FPGA designs are able to withstand the type and amount of radiation present in their operating environments.

A significant source of ionizing radiation are alpha particles emitted from impurities in device materials. Alpha particles directly ionize the device as they pass through it. The dominant sources of alpha particles are uranium and thorium found in the packing materials, which makes shielding difficult. Special considerations can be taken to lessen the influence of alpha particles emitted from packaging materials on FPGA devices [18].

Another significant source of fault-inducing radiation comes from cosmic rays. Cosmic rays are high energy atomic particles that mostly originate from beyond the solar system. Less than 1% of particles directly from cosmic rays ever make it to the earth's surface. Due to their density and stability, neutrons are the most likely candidate from cosmic rays to cause an upset in an FPGA here on earth. Since neutrons are not charged, they indirectly ionize a device by colliding with other atoms in the device, releasing secondaries [18]. The high energy neutrons flux (above 10MeV) in New York City is approximately 13  $n \ cm^{-2}h^{-1}$  and increases as a function of altitude [4].

The third significant source of fault-inducing radiation comes from the interaction of thermal neutrons with boron-10 found in borophosphosilicate glass (BPSG), which has been used to fabricate some FPGAs. Thermal neutrons are relatively slow and have energies of less than .4 eV. After boron-10 absorbs a thermal neutron, it breaks apart into an alpha particle, a gamma ray, and a lithium nucleus. The alpha particle ionizes the device and may cause a configuration upset. To eliminate the threat posed by low-energy thermal neutrons, FPGAs can be manufactured without the use of BPSG [7].

Radiation poses a greater concern in harsh radiation environments like space and highenergy physics experiments [6]. Mission length, environmental radiation, and the number of deployed units are all factors to take into consideration when determining the reliability needs of a design [16]. The presence of radiation is a concern for FPGA designs because ionizing radiation can affect the functionality and state of a design.

## 2.2 Radiation Effects

Radiation effects on SRAM-based FPGAs can be caused by a single energetic particle or result from the accumulation of charge injected by radiation [19]. When a single energetic particle creates an observable effect within the FPGA, it is known as a single event effect (SEE) [3]. Long term effects of radiation exposure include total ionizing dose (TID). There are other radiation effects such as displacement damage and prompt dose. This overview of radiation effects gives attention to SEEs and focuses on SEUs, which alter FPGA configuration memory. This work does not address TID or other radiation effects beyond SEEs. An explanation of various SEEs is given and their influence on FPGAs is described.

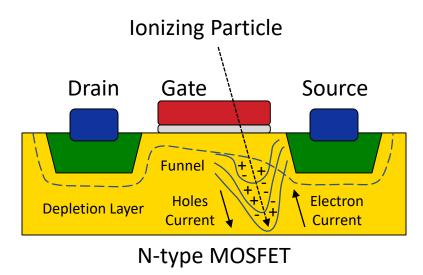

Radiation effects result primarily from the funneling phenomenon. As shown in Figure 2.1, when an ionized particle passes through a sensitive node in a semiconductor, a path of electron-hole pairs is produced from the semiconductor material atoms, resulting in funnel-shaped equipotential surfaces that create a current in the device [19, 20]. This can also occur when secondary particles from a neutron collision pass through the sensitive region of the device. This phenomenon contributes to radiation effects and is the primary mechanism behind SEEs. Because of the complexities of this process, simplified fault models have been created to represent the behavior of these effects at a higher level of abstraction.

Figure 2.1: Funneling phenomenon in a N-type MOSFET. Adapted from a figure in [19].

# 2.2.1 Single Event Effects

SEEs are any observable effects caused by single energetic particle [3, 4]. There are two main types of SEEs: destructive and non-destructive. Destructive SEEs can permanently damage the FPGA, whereas non-destructive SEEs are transient and can be removed by reconfiguring or power cycling the device. Destructive SEEs include: single event latchup (SEL), single event burnout (SEB), and single event gate rupture (SEGR). Non-destructive SEEs include: single event transient (SET), single event upsets (SEUs), and single event functional interrupts (SEFI). Of these SEEs, SETs and SEUs are the primary concern for FPGA vulnerability because they occur more frequently [16, 19, 20].

SELs occur when a particle strike causes an internal short between power and ground within the FPGA. Only power cycling the FPGA can stop the SELs. If the SELs is not removed in time, the FPGA can be permanently damaged because of the high-currents induced by the latchup [19]. A thoughtful FPGA fabrication process and layout can mitigate this effect [21]. FPGAs can be tested for SEL immunity before being used in harsh radiation environments. Devices that are not immune to SELs are often avoided for use in harsh radiation environments like space [16].

SETs occur when a particle strikes the channel region of an inactive n-type MOSFET or the drain region of an inactive p-type MOSFET [19,20]. The induced current pulse appears as a *glitch*

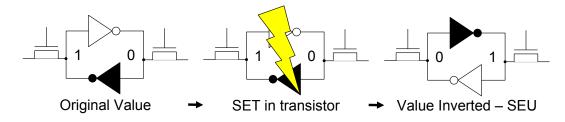

Figure 2.2: An SEU within an SRAM-cell

and is short lived. SETs are assigned a polarity based on the transition of the output of the CMOS device. Positive SET pulses transition from 0 to 1 and back to 0; negative SET pulses transition from 1 to 0 and back to 1. SETs can be latched by memory elements as they propagate through the device, which becomes a greater issue at faster clock speeds.

SEUs occur when ionizing radiation inverts the value stored in a memory element, such as a configuration bit of an FPGA. An illustrative example, depicted in Figure 2.2, shows how a single particle is able to upset the value stored in an SRAM cell. In this example an SET occurs within a transistor of the feedback loop used to maintain the value of the SRAM-cell. With enough amplitude, this SET disrupts the feedback loop of the cell and causes it to take on the inverted value. When this occurs in an SRAM-based FPGA it can have many adverse effects (see Section 2.3).

SEFIs occur when elements of the FPGA that control its functionality as a whole are affected by a single particle strike. SEFIs can cause the entire FPGA to malfunction [19]. SEFIs are temporary but could prevent reprogramming the FPGA until the next power cycle. There is some state within an FPGA that, if upset, could disrupt the global functionality of the FPGA. While SE-FIs are a concern to FPGA reliability, more SRAM-based FPGA design failures are due to SEUs and SETs.

#### 2.3 FPGA Architecture and SEU Failure Modes

Understanding FPGA architecture and design flow helps explain how SEUs, induced by ionizing radiation, can adversely affect an FPGA design. This section describes basic FPGA architecture and how SRAM-based FPGAs support programmability. An overview is given for an FPGA design flow from hardware description to configuration, and then common SEU failure

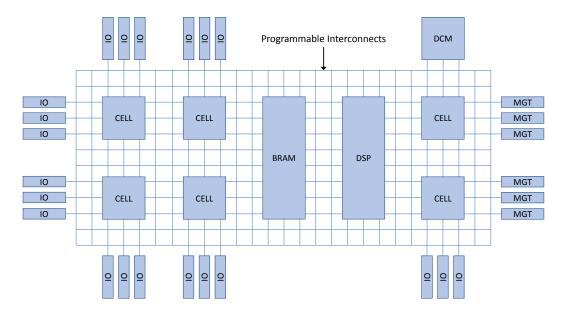

Figure 2.3: Island-style FPGA Architecture Layout. Adapted from a Figure in [16].

modes are discussed. This background information motivates the need for SEU sensitivity evaluation of FPGA designs by explaining how an SEU can cause a design to fail.

An FPGA consists of basic logic building blocks and specialized hard IP blocks organized into a specific architecture. Lookup-tables and flip-flops are grouped into slices or cells with other supporting hardware (e.g., carry-chains, multiplexers, control signals). Some lookuptables are read only, while others can have their values changed by the design (e.g. LUTRAMs, shift-registers). Additional hard IP blocks can include: large user-memories (BRAMs), arithmetic units (DSPs), analog-to-digital converters (ADCs), high-speed serial I/O (MGTs), and clockmanagers (DCM). The available resources and architecture are vendor specific, but many popular FPGA architectures are *island-style* meaning that groups of logic resources are surrounded by programmable routing interconnects in a 2D matrix like formation [22]. This layout is depicted in Figure 2.3.

There are two major types of bits within an FPGA's programming data: configuration (CRAM) bits and internal block memory (BRAM) bits. Data associated with programmable interconnects, lookup tables, control signals, and the contents of smaller user-memories (e.g., flip-flops, LUTRAMs, shift-registers) are stored in CRAM bits. Data associated with the contents of larger blocks of user-memory are stored in BRAM bits. Although the percentage is small, there are other types of bits within the FPGA's programming data (e.g., global status registers, test control logic). The contents of user-memories may be altered by the design during operation. The configuration of specific designs are loaded into the FPGA's programming data.

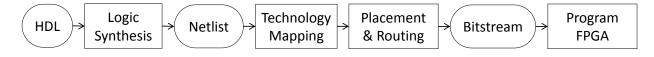

Figure 2.4 shows the generalized FPGA design flow. Digital designs are described in a hardware description language (HDL) and synthesized into a netlist, which describe the cell instances and connections needed to implement a given user-design. Computer aided design tools (CAD) map the cell instances to technology specific primitives (e.g. a six input look-up-table). These primitives are then *placed*, or assigned to a specific location in the FPGA. All of the connections are then *routed* using programmable interconnects. This information is used to generate a bitstream, which is the contents of the CRAM bits and the initial value of the BRAM bits used to program the FPGA. When the bitstream is configured onto the FPGA, all of its information, (the lookup-table contents, interconnects, initial state, and other configuration), is loaded into the respective memory cells. SRAM-based FPGAs use SRAM-cells to store this information. Once the FPGA is loaded, the design begins to operate on the FPGA fabric. Some memory cells maintain their value throughout the operation of the design, others are user-memory resources and change their values according to the design.

Figure 2.4: Basic FPGA Design Flow

Since FPGA programming data stores circuit configuration and state, SEUs in an FPGA's programming data can alter the design operating on the FPGA and lead to failure. The main cause of SEU failure modes in FPGAs are SEUs in routing resources, lookup tables, control signals, and user-memories. SEUs in lookup tables and control signals can corrupt logic and alter the functionality of primitive blocks used by the design. SEUs in user-memories can corrupt the state of a design (see Figure 2.5). SEUs in routing resources may cause nets to disconnect, short to power or ground, or bridge with other nets in the design (see Figure 2.6) [23,24].

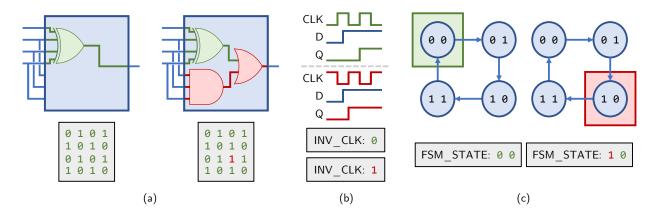

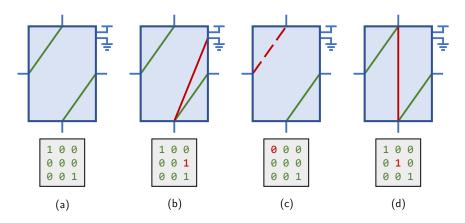

Figure 2.5: SEU failure modes. SEUs can alter correct logic (a), control (b), or state (c).

To support all of the resources and possible interconnect configurations many CRAM cells are needed to store the programming data. The specific role of each bit in the data is proprietary, but a large portion of configuration memory is dedicated to functionality beyond user flip-flops, BRAM content and LUT contents [25]. One study found through fault injection that approximately 80% of FPGA design failures originate from SEUs in routing structures [23].

Figure 2.6: SEU routing failure modes. SEUs can alter correct routing (a) by shorting to ground (b), disconnecting a route (c), or bridging two routes together (d).

# 2.4 Reliability: Faults, Errors and Failures

A reliable FPGA design is one that can withstand environmental factors, such as radiation, without ceasing to provide its defined service. Unreliability stems from faults, errors and failures.

A fault is the lowest level problem that occurs within the FPGA, such as an SEU. An error is the manifestation of a fault, and a failure occurs when the provided service deviates from the intended service [26]. It is important to understand that in any FPGA design, a fault *may* lead to failure but the occurrence of a fault does not guarantee that an FPGA design will fail. A fault-tolerant FPGA design can withstand more faults without failing.

Techniques can be applied to an FPGA design that will reduce its sensitivity to SEUs. These *SEU mitigation* techniques typically mask or detect faults within the system through redundancy, checkpoints, or some type of error correction code. By correctly masking or handling fault within the design, the design becomes more fault-tolerant, meaning that it can tolerate more faults without failing.

Radiation can cause faults within SRAM-based FPGAs. Any SEU in configuration memory is a fault. Not all faults will affect an active design on an FPGA; a fault may or may not manifest as an error. If an SEU occurs in an unused portion of the FPGA or in such a way that its effect on the design is masked, it will not alter the operating design. For example, if an SEU causes the contents of a LUT to change at a lookup address that is unused or otherwise masked, it will have no effect on the operating design. This is significant because FPGA designs only utilize a portion of the FPGA. As covered in Section 2.3, a fault can change the behavior and state of an FPGA design in many different ways such as: changing the logic in a LUT, altering routing within the circuit, and modifying the behavior of components. If an SEU does alter a configuration bit associated with the proper operation of a design, it may cause an error in the design such as: providing incorrect output, halting its operation, or otherwise deviating from its specified behavior.

An error is a deviation from expected behavior. Some errors can be detected and recovered from or simply ignored. It is possible for an error to occur without being considered a failure. An example of this is when the checksum of a communication interface does not check out but after re-transmission, the correct data is received. Here the defined service is still provided even though an error has occurred. Unacceptable errors are considered failures.

A failure occurs when an error causes a service to deviate from its defined specification. A major concern when it comes to failure is that of silent data corruption (SDC). SDC occurs when output or state is incorrect, but the error goes undetected. This can be particularly troublesome for missile guidance systems, file-compression, and encryption algorithms. The on-chip error

detection evaluation approach used in this thesis focuses on detecting SDC of output signals for selected benchmark circuits.

#### **2.5** SEU Mitigation Techniques

Adverse affects of SEUs on FPGA designs can be reduced by applying various SEU mitigation techniques to the design. Many post-manufacturing SEU mitigation techniques have been developed for SRAM-based FPGAs. Generally, concepts of redundancy, repair, error detection and correction (EDAC), or the elimination of single point failures (SPF) are used to design SEU mitigation techniques. The three SEU mitigation covered in this thesis are: TMR, configuration scrubbing and user-memory scrubbing. While other SEU mitigation techniques exist, these SEU mitigation techniques are common examples of ways to improve the reliability of an FPGA design, and they are used in the experiments of this thesis.

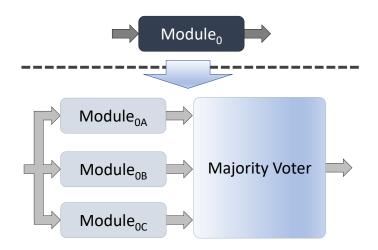

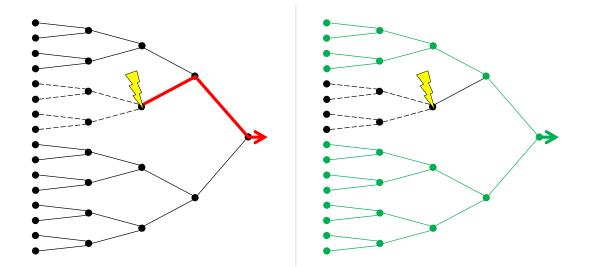

#### 2.5.1 Triple Modular Redundancy

TMR is a well-known SEU mitigation technique that involves triplicating the original circuit and inserting voters (see Figure 2.7). There are many ways TMR can be applied [27]. TMR can be applied spatially or temporally [10]. Majority voters mask SEUs by propagating the dominant output of the triplicated circuit. If at least two of three redundant circuits are operating correctly, the output of the system will be correct as well. To avoid single point failures, voters themselves are often triplicated as well [12]. TMR protects the designs from errors in the routing resources, lookup tables, control signals, and internal state. While TMR overhead is at least  $3 \times$  in area, it has been shown to provide significant improvements in reliability on a number of FPGA circuits [28].

TMR cannot protect against SEU accumulation across more than one redundant copy. The granularity of TMR affects the amount of SEUs a design can tolerate before failing; fine grain TMR (i.e., TMR of the smallest components) is able to withstand more faults at the cost of additional area and delay due to the insertion of more voters [29]. By placing voters throughout the design, the granularity of TMR is made smaller. Figure 2.8 shows a fine grain TMR scheme that places majority voters in feedback paths [12]. By triplicating a design into smaller partitions, SEU are allowed to accumulate in ways that would otherwise cause the design to fail. That being said,

Figure 2.7: Triple Modular Redundancy (TMR).

SEUs can still accumulate within the same partition causing TMR to fail. In order to prevent this kind of failure, an SEU repair mechanism, such as scrubbing, must be combined with TMR [30].

Figure 2.8: Fine-grain TMR with Voter Synchronization in the Feedback Path. So long as no more than one TMR domain per partition is damaged, the output will be correct.

It is possible for a single SEU to cause the entire system to stop functioning correctly. Any aspect of the design that is not protected with redundancy or fault tolerance presents an SPF vulnerability. Within an FPGA's architecture, it is also possible that an SEU breaks redundancy by causing failures in multiple circuit copies [31, 32].

## 2.5.2 Duplication with Compare

Another SEU mitigation technique based on redundancy is duplication with compare (DWC). DWC involves duplicating a module and comparing the outputs of the two copies against each other to detect errors. Similar to voters in TMR, detectors are inserted into the circuit to detect any discrepancies. A major distinction between TMR and DWC is that TMR is able to mask errors by propagating the majority vote of the three redundant circuits whereas DWC is only able to detect that an error has occurred; DWC cannot mask errors. DWC has lower overhead than TMR because only two copies are made rather than three. When DWC is employed, detectors themselves are often duplicated as well to prevent errors in detection logic from being reported as errors in the design under-test (i.e., a false-positive). When duplicate detectors are used, their output is encoded so that an error is only reported with both detectors detect an error. Using DWC for on-line error detection has been shown to be an effective means of detecting errors caused by configuration upsets in FPGA-based designs [33].

#### 2.5.3 Configuration Scrubbing

Configuration scrubbing involves the rapid and continuous repair of upsets in configuration memory as they occur [34]. Configuration scrubbing is performed without interfering with the operation of an active design. In other words the application loaded onto the FPGA does not have to go off line for configuration scrubbing to take place. As such, configuration scrubbing can only repair upsets that affect bits of the programming data that are not changed by the design. User-memories are not protected by configuration scrubbing. Bits that are protected include the contents of look-up tables used to implement logic, interconnect and multiplexer configurations for routing nets between components, and other constant configuration values.

Configuration scrubbing prevents the accumulation of more than one upset in configuration memory that may break TMR. Configuration scrubbing can be performed in many different ways. External readback configuration scrubbing compares the current configuration of the FPGA against a golden copy to detect and repair SEU. External scrubbing has been shown to greatly reduce the sensitive cross section of a design [35]. Internal configuration scrubbing uses frame-based error correction codes (ECC) and global cyclical redundancy check (CRC) calculations to detect SEUs

and correct them when possible [14]. SEUs that affect user-memory bits cannot be repaired by configuration memory scrubbing. To repair SEUs that affect these bits, additional SEU mitigation techniques need to be applied.

#### 2.5.4 User-Memory Protection

Internal memories that contain large amounts of state pose a unique challenge when faced with SEUs. Although a number of memory coding techniques can be used, these techniques do not adequately protect the memory from the accumulation of multiple upsets within a single memory word. This problem is especially prevalent in memories whose contents do not change very often (such as read only memories) as there is greater potential risk of SEU accumulation. In order to prevent the accumulation of upsets that may invalidate memory coding techniques, such as ECC, some form of memory scrubbing may be used in environments where soft error rate (SER) is high (e.g. space environments) [11].

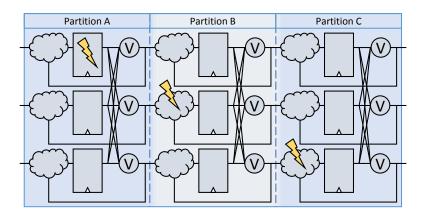

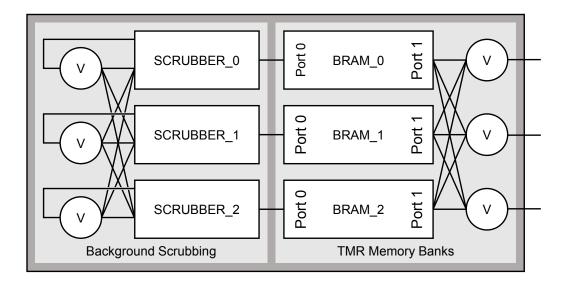

Scrubbing BRAM bits repairs SEUs as they occur and prevents the failure of additional protection mechanisms, such as TMR or ECC, that can result from the accumulation of SEUs. One of the most common memories that may need to be protected with scrubbing are user block memories called BRAM modules. These modules are user configurable and provide a limited number of access ports to the associated BRAM bits. Protecting BRAM modules with scrubbing can be challenging if all available ports are already in use. Figure 2.9 shows the contents of a dual-port BRAM module being scrubbed. One port is dedicated to scrubbing and another port is a dedicated access port for the design. In this case, the memory module is triplicated and the majority vote between the three copies is written back to the memory to scrub away SEUs.

Scrubbing is performed in a three step process. First, a memory word is read out of memory. Second, the word is decoded and corrected through ECC or another form of memory protection. Finally, if an error is detected in the word, the corrected word is written back to memory to overwrite the upsets. Scrubbing can be performed deterministically by iterating through all of the words in memory, or probabilistically by scrubbing a memory word only when it is used by the design [36].

Other memory protection techniques, such as ECC, can also benefit from scrubbing. Encoding is used to mask SEUs in ECC protected memory. Without correcting upsets in memory, by either overwriting them with new values or scrubbing them, eventually enough SEUs will accumulate to cause the ECC method to fail [11]. By providing memory scrubbing, memories affected by SEUs will not accumulate upsets.

Figure 2.9: Internal BRAM Scrubbing

There are some limitations to the benefits that user-memory scrubbing provides. Additional resources are consumed by scrubbing logic. This logic may also be vulnerable to failure if not protected with SEU mitigation techniques. Also, memory that changes value often benefits less from scrubbing because the risk of accumulating SEUs that would invalidate ECC is lower. The benefits of scrubbing memory caches are limited because when an error is detected in a cache, the cache can be easily be flushed and refreshed instead of being scrubbed [37]. Another limitation of user memory scrubbing is that it can only repair errors that occur within a memory; it cannot prevent a error from being written to memory.

# 2.5.5 Complementary SEU Mitigation

Complementary SEU mitigation and repair techniques work together to improve an FPGA design's fault-tolerance and prevent SEU failure modes from occurring. TMR masks SEUs to prevent failure. Scrubbing repairs SEUs to prevent accumulation that would break TMR. The

reliability of a system can be significantly improved when both TMR (fault masking) and configuration scrubbing (repair) are used together [28]. Without configuration scrubbing, the benefits of TMR are limited (especially for long missions).

#### 2.6 SEU Sensitivity Estimation

The likelihood of a design failing when a random upset occurs is the SEU sensitivity of an FPGA design. There are many factors that contribute to the SEU sensitivity of an FPGA design such as the size of the design and whether or not any SEU mitigation techniques were applied to it. The main idea is that there are bits within an FPGA design that will cause the design to fail if upset. These *sensitive* bits exist within the FPGA configuration memory for a particular design and are most likely different for each FPGA design. Upsets in these bits cause a design to fail by introducing the SEU failure modes discussed earlier into the design. The ratio of sensitive CRAM-bits to non-sensitive CRAM-bits reflects the SEU sensitivity of a design. The likelihood of an SEU occurring from radiation exposure also affects a design's SEU sensitivity. This term attempts to provide common ground between fault injection and radiation testing.

Knowing the SEU sensitivity of a design provides great insights to the potential risks of radiation exposure for FPGA designs and the benefits of SEU mitigation techniques. Every design has a different level of SEU sensitivity. SEU mitigation techniques need to be proven and the SEU sensitivity of a mitigated design can provide supporting data or reveal vulnerabilities. As newer FPGAs are released, changes in FPGA design SEU sensitivity can reflect the impact of changes in the fabrication process, and FPGA architecture on reliability. The SEU sensitivity of a design provides insight into every change and each new design.

SEU sensitivity of an FPGA design is often estimated by sampling a portion of CRAM-bits on the FPGA for sensitivity. Because newer FPGAs now have tens of millions or more CRAM bits and each design has numerous possible states, it is nearly impossible to exhaustively test each bit to estimate the SEU sensitivity of a design. Instead, a portion of CRAM cells are sampled for sensitivity through fault injection and radiation testing. Fault injection involves artificially emulating an SEU by altering the contents of CRAM-bits [15]. Radiation testing involves exposing the FPGA design to accelerated radiation that causes SEUs [16]. A key component of most SEU sensitivity testing approaches is being able to detect that a functional failure has occurred in the design. The next chapter discusses aspects of SEU sensitivity testing and the benefits and limitations of various testing approaches.

# CHAPTER 3. SEU SENSITIVITY TESTING APPROACHES

SEU sensitivity estimation plays an important role in radiation hardness assurance (RHA), SEU mitigation technique validation, and in improving the fault-tolerance of FPGA designs. Missioncritical space applications have rigid requirements for system reliability. Radiation hardness assurance seeks to qualify devices for space. So much goes into qualifying an integrated circuit for space [38]. Part of qualification includes SEU testing. Test guidelines and standards have been written for radiation testing [4, 39]. The benefits of SEU mitigation techniques can be proven through SEU sensitivity estimation. Additional unanticipated vulnerabilities can be exposed through SEU sensitivity estimation.

In order to estimate the SEU sensitivity of an FPGA design, there must be a means of observing failure events caused by SEUs, and the factors that lead up to failure must be recorded for analysis [16]. Many approaches have been developed to estimate the SEU sensitivity of an FPGA design through fault injection and radiation testing. Fault injection mimics the behavior of an SEU on the FPGA under test, and radiation testing exposes the FPGA to accelerated radiation sources that cause SEUs within the FPGA. Various test setups have been created to configure fault injection and radiation testing towards SEU sensitivity testing approaches. SEU sensitivity testing approaches used in related works are presented and an on-chip error detection approach is introduced. The limitations and benefits of each approach are discussed.

# 3.1 General Approach for SEU Sensitivity Testing

SEU sensitivity testing is event based, where the event is usually the occurrence of a functional failure within the design. Most SEU sensitivity testing approaches depend on the ability to detect when the design under test is not operating correctly [16]. Testing approaches for SEU sensitivity estimation create an environment where a design can fail, and they measure and record the factors that lead up to failure for analysis. Common elements are found in most SEU sensitivity testing approaches to support SEU sensitivity estimation.

There are five common elements found in most SEU sensitivity testing approaches. First, the design under test must be active. Second, the output of a design under test is usually monitored for errors. Third, the environment is set up to create possible failure conditions through fault injection or radiation testing. Fourth, factors leading up to failure, such as the number of of injected faults or amount of radiation exposure, are recorded for analysis. Finally, a method is provisioned to place the design back into a known good state so that additional failure events can be observed.

In SEU sensitivity testing, the design is kept active so that functional failures can occur and be detected. If a design sits idle, the effects of SEUs on the design may go unnoticed. Keeping as much of the design active during SEU sensitivity testing as possible allows failures caused by SEUs to propagate to the outputs of the design where they may be observed. Designs are typically kept active using a set of input vectors [16]. A clock signal is also usually provided to the design as well.

Two main methods are used to monitor the outputs of a design for errors. First, the outputs of a design may be compared against a set of golden output vectors that match the expected behavior of the design. Second, the outputs of a design may be compared against those of an identical design instance that operates in lockstep with the design under test. If any disagreement is found, a functional failure is detected and reported. Other methods for monitoring outputs could include monitoring checksums produced by the design.

Failure conditions are introduced to the active design through fault injection or radiation testing. Typically, only the design under test is exposed to factors that cause SEUs. Test control unit, functional error detection logic, and the golden output vectors or lockstep design instance are commonly separated from the design under test to make them fault-immune. For example, many SEU sensitivity testing approaches place the design under test on a separate FPGA. This FPGA is then injected with faults or placed in an accelerated radiation beam so that SEUs only occur within the design under test and not in other parts of the test setup.

The factors that lead up to a functional failure are recorded for analysis. For fault injection, the total number of fault injected and the total number of failures observed may be collected. This can be used to estimate the sensitivity of the design. Also the particular bit injected prior to a

functional failure may be recorded for reproducibility and failure characterization. For radiation testing, the total radiation exposure of the design and the total number of observed failures may be collected. Radiation exposure is usually measured in terms of fluence, and the SEU sensitivity of the design is approximated by the cross section of the design, or number of failures divided by total fluence.

Many failure events must be observed for the collected data to be statistically significant and representative of the SEU sensitivity for a particular design [15,16]. To support the observation of multiple failure events, most SEU sensitivity testing approaches provision a method of resetting the design, or resynchronizing it into a known good state so that additional failure events can be observed. Any necessary control signals are provided to the design. The process of resynchronizing the design for the next test run is often automated to assist in rapid data collection.

Most testing approaches organizes these five common elements into a test setup with an accompanying test fixture to support SEU sensitivity testing. The general setup for SEU sensitivity testing is described in the next section.

#### **3.2** General Setup for SEU Sensitivity Testing

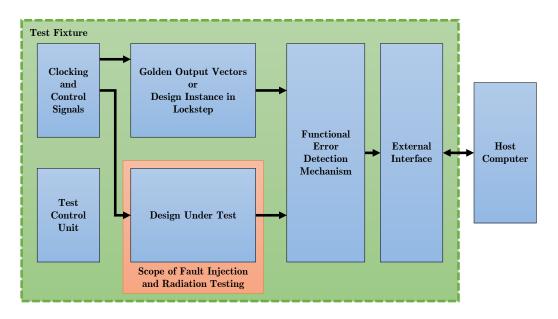

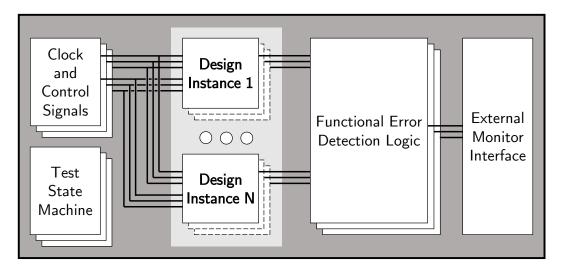

While each approach is different, the test setup for many SEU sensitivity estimation approaches is very similar. Each test setup typically has a host computer that interfaces with a test fixture. The test fixture holds the FPGA design under test and contains additional components to support the experiment. Figure 3.1 depicts the general setup of an SEU sensitivity test and the common components of a test fixture. Clock and control signals drive the design under test and provide a means to reset or resynchronize the design. A test control unit orchestrates the operation of the design under test with the rest of the test fixture. It keeps the design active by managing input vectors or can make sure the design operates in lockstep with a golden design instance if used. Functional error detection mechanism provides the means of detecting functional errors in real time. This mechanism usually compares the output of the design under test against a set of golden output vectors, or a fault-immune instance of the design operating in lockstep outside the scope of fault injection or radiation testing. If a disagreement is found, a failure is reported. This mechanism is especially important because most approaches depend on the ability to detect errors in order to collect good data. The external interface provides a way to communicate with the host computer. Other common aspects incorporated into a test setup may include automated logging on the host computer and using heartbeats or watchdogs, (e.g., provided by the test control unit), to ensure that the design is still operational [16].

Figure 3.1: General Setup for SEU Sensitivity Test

It is important that design instances operate in lockstep so that they can be compared against each other to detect functional failures. When designs operate in lockstep, no instance advances to next computation until all instances have completed the previous computation, and all instances produce outputs in the same order. For many FPGA designs this is not hard to accomplish since computations usually have a predictable data flow path. So long as predictable design instances begin execution on the same clock cycle, they will operate in parallel. When design instances use roll back check pointing or perform out-of-order computation, a more complicated mechanism must be used to keep the design instances in sync [40]. The state machine can be used to ensure the synchronous operation of design instances and tag the appropriate signal samples for comparison in the case of out-of-order computation.

One of the most important SEU evaluation elements is the functional error detection mechanism. When evaluating the SEU sensitivity of a design, failure events are collected and recorded. To evaluate the sensitivity of a design to configuration upsets, there must be some way of knowing when the design has experience a functional failure. Many mechanisms can be used to detect functional failures but their primary goal is the same: to detect when an error has occurred within the design.

Many testing approaches separate the design under test from the other test fixture components so that the scope of fault injection or radiation testing only extends to the design under test and nothing else. This is typically done by placing the design under test on its own FPGA. Approaches that do not place the test control unit, error detection logic, golden output vectors, etcetera on the same FPGA as the design under test will be referred to as off-chip error detection approaches; whereas an on-chip error detection approach places additional test components on the same FPGA as the design under test.

## **3.3** SEU Sensitivity Testing Examples

The approaches discussed in this section specifically focus on estimating SEU sensitivity of SRAM-based FPGAs in harsh radiation environments and estimating the reliability benefits of SEU mitigation techniques. These approaches use an FPGA in fault injection or radiation testing to estimate the reliability of an FPGA design on a specific target FPGA. The reliability benefits of SEU mitigation techniques are estimated by comparing the estimated SEU sensitivity of a mitigated and an unmitigated version of the same design.

Fault injection and radiation testing are common methods for estimating the SEU sensitivity of a design operating on an FPGA. SEU sensitivity is defined as how prone to failure a given design is when an SEU occurs. The design operates on the FPGA while the FPGA undergoes fault injection or radiation testing. The rate of design failure with respect to injected faults or radiation exposure is the primary indicator used to determine SEU sensitivity. For fault injection, SEU sensitivity is typically measured in terms of mean upsets to failure (MUTF) but can also be measured in terms of the percentage of upsets that cause the design to fail. A lower MUTF or a higher percentage of *sensitive* bits means a greater SEU sensitivity. For radiation testing, SEU sensitivity is typically measured in terms of cross-section. The larger the cross section, the greater the SEU sensitivity. Several testing approaches used in related works to estimate SEU sensitivity are presented in this section. Their test setup is describe and some results are included from experiments that use them. Benefits and limitations of each approach are discussed compared against each other.

# 3.3.1 FT-UNSHADES

FT-UNSHADES [41] emulates fault injections in ASIC circuitry using an FPGA as a fault injection emulation platform. This evaluation approach uses a formal verification tool to ensure that the ASIC netlist and its corresponding FPGA netlist maintain and guarantee equivalence, and then uses partial reconfiguration to inject faults into the user flip-flops. This approach places a golden and a *faulty* instance of the design on the same FPGA along with comparison and test control logic. Test vectors are loaded externally and faults are limited to flip-flops within the faulty instance of the design. Figure 3.2 shows the test setup used by FT-UNSHADES. Notice that only a single FPGA is used to implement this fault emulation approach.

Figure 3.2: FT-UNSHADES test setup. Figure taken from [41].

Using this approach a LEON2 soft processor without mitigation was compared against an XTMR version (i.e., Xilinx automated TMR), and a fault tolerant (i.e., LEON3-FT) version. The most sensitive components of the processor were identified and protection provided by the mitigated version was verified [41]. This platform is used in [42] to prepare designs for radiation testing. The fault injection emulation approaches presented in [43] and [44] are similar to that of FT-UNSHADES.

This is an on-chip error detection approach, and is similar to the on-chip error detection approach described in Chapter 4. It is on-chip because the test control logic, lockstep golden design instance and the error detection mechanism are all on the same FPGA. The biggest difference between this approach and the one described in Chapter 4 is that this approach limits faults to the design instance under test and the other approach allows faults anywhere on the FPGA.

Using an FPGA to emulate fault injection in ASIC circuitry accelerates ASIC fault-tolerance testing, but since faults are limited to flip-flips, only a small portion of FPGA architecture is included in an SEU sensitivity estimation obtained through this approach. This approach does not consider the effects of SEUs on logic or routing in an FPGA design. This approach is not designed for use in radiation testing. However, only a single FPGA is needed to implement this approach making it less expensive to implement than a multi-FPGA test setup. The approach could also feasibly be implemented on a ready made FPGA evaluation board.

#### 3.3.2 FLIPPER

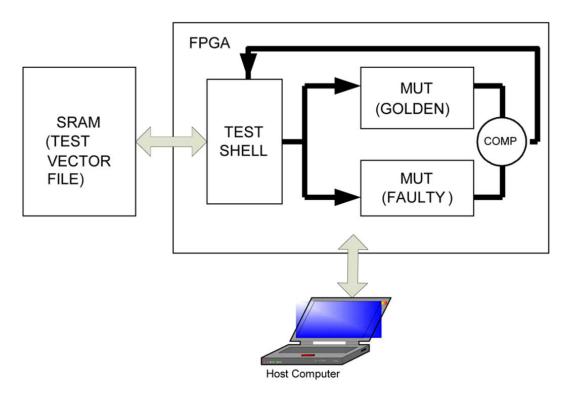

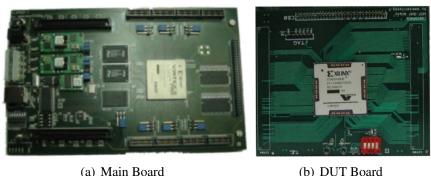

FLIPPER [45] is a fault injection approach that injects a fault using partial reconfiguration and uses stimuli and golden values derived from HDL simulation to determine when the design has failed. If the output of the FPGA does not match the expected golden values for the provided input stimulus, a failure has occurred. FLIPPER consists of two boards: the main board that manages fault injection, and a device under test board that contains the FPGA under test (see Figure 3.3).

In a case study, faults were injected every 18ms and allowed to accumulate until a functional fault was detected. For each injected fault, 26,000 testbench cycles are executed. Using the approach, the MUTF of various mitigation schemes were evaluated for an FPGA design. The plain design, without mitigation, had a MUTF of 337 accumulated faults. The Xilinx TMR version

(b) DUT Board

Figure 3.3: FLIPPER test fixture consisting of two boards. Images taken from [45].

had a MUTF of 1,330 accumulated faults. Based on these results, Xilinx TMR without scrubbing reduced the SEU sensitivity of the evaluated design  $3.9 \times$ .

Having a separate test board provides for extendability of the approach to newer devices and helps reduce reoccurring engineering costs [15]. The main board contains an FPGA which can be reused for new FPGAs, but at some point the main board would need to be updated with a newer FPGA. This approach leverages HDL simulation tools to provide stimulus and compare device outputs against golden output vectors. An advantage of using test vectors is that only a single target FPGA is needed.

#### 3.3.3 **SLAAC-1V**

The SLAAC-1V board [46] is an FPGA fault injection and radiation testing approach that utilizes three FPGAs: one as the FPGA under test, one as a golden FPGA that runs in parallel lockstep with the FPGA under test and is failure-immune, and one for comparison, reconfiguration, and control logic of the other two. This approach allows for off-chip error detection of very complex designs without having to precompute golden test vectors. So long as the inputs are the same, the outputs of the golden and the device under test FPGAs should be the same also, except in the case of failure. This is an off-chip error detection approach because error detection logic is not on the same FPGA as the design under test. The golden lockstep design is also not on the same FPGA as the design under test.

A linear feedback shift register (LFSR) design was evaluated for SEU sensitivity using this approach. A fault was injected in the device under test every 267us. Between faults the circuit is

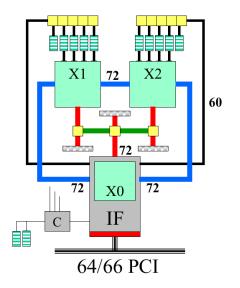

Figure 3.4: SLAAC-1V setup diagram. Figure taken from [46]. X1 and X2 are the golden and device under test FPGAs respectively. X0 is the comparator FPGA.

cycled and tested for discrepancies with the golden. All 5.9 million configuration bits on Xilinx Virtex XCV1000 were exhaustively fault injected. It was found that the tested LFSR design was relatively insensitive to injected faults.

The SLAAC-1V board was used in a later experiment that compared the SEU sensitivity found in fault injection against that found in proton radiation testing [25]. In this experiment, several versions of a multiplier and LFSR were tested. A 36-bit and 72-bit multiplier, and a 72-bit LFSR circuit demonstrated a 4.0%, 14.7%, and a 4.8% sensitivity rate respectively in fault injection, and a 4.9%, 17.2&, and 5.0% sensitivity rate in radiation testing respectively. This experiment helps to validate this approach by showing that fault injection data agrees with the radiation testing data.

In [10] several SEU mitigation techniques were compared using the SLAAC-V1 board approach to gather fault injection data. The fault injection campaign used in this experiment simulated configuration scrubbing by correcting the injected fault after checking for output errors. TMR and scrubbing in this experiment reduced the SEU sensitivity of a 36-bit counter and two finite state machine  $2-3\times$ .

One advantage of this approach is that allows two test designs to operate in lockstep. For complex FPGA designs, comparing the output of two designs operating in lockstep can be easier

than comparing the output of a single instance against a set of golden output vectors. Unlike FT-UNSHADES, this approach places comparison logic on a separate FPGA. Doing so allows faults to be injected anywhere in the FPGA under test without disrupting the operation of the test setup. It also makes it possible to use the test setup in radiation testing. Some drawbacks of this approach are that multiple target FPGAs are needed and that a entire new board would need to be re-engineered to test newer FPGAs.

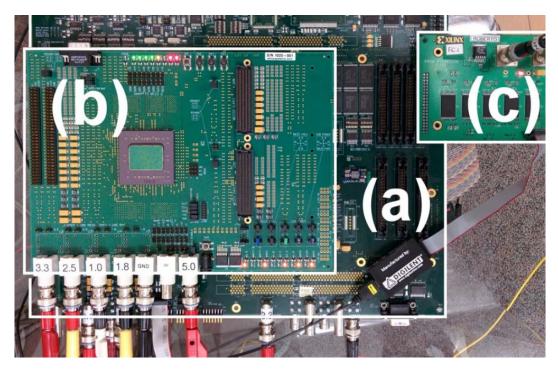

## 3.3.4 XRTC-V5FI

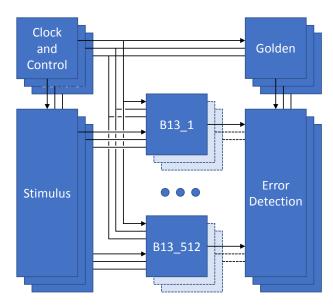

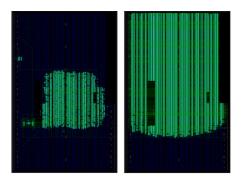

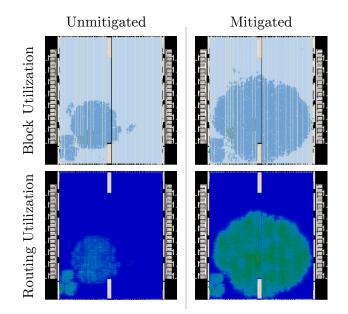

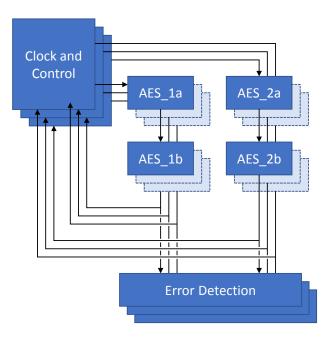

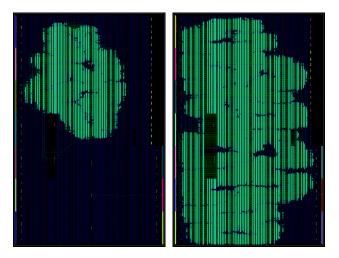

The XRTC-V5FI [47] approach consists of three main boards: the XRTC motherboard, the Xilinx Vertex 5 FPGA under test daughter card, and an external memory card (see Figure 3.5). There are two FPGAs on the mother board: the ConfigMon, and the FuncMon. The ConfigMon FPGA controls all of the reconfiguration and rapid fault injection, and the FuncMon is dedicated to detecting functional failures in the FPGA under test. Rather than compare the outputs of a design against external golden values to detect failures, this approach compares the outputs of two identical designs instances on the FPGA under test against each other. Several signals are compared externally between the two, these signals are sent to the FuncMon FPGA. It is not likely that a single fault will affect both instances in exactly the same way, and since the comparison logic is separated from the FPGA under test, failure of the error-detection logic is unlikely as well.