All Theses and Dissertations

2013-12-01

# Interface Design and Synthesis for Structural Hybrid Microarchitectural Simulators

Zhuo Ruan Brigham Young University - Provo

Follow this and additional works at: http://scholarsarchive.byu.edu/etd

Part of the Electrical and Computer Engineering Commons

# BYU ScholarsArchive Citation

Ruan, Zhuo, "Interface Design and Synthesis for Structural Hybrid Microarchitectural Simulators" (2013). All Theses and Dissertations. Paper 4369.

This Thesis is brought to you for free and open access by BYU ScholarsArchive. It has been accepted for inclusion in All Theses and Dissertations by an authorized administrator of BYU ScholarsArchive. For more information, please contact scholarsarchive@byu.edu.

# Zhuo Ruan

A thesis submitted to the faculty of

Brigham Young University

in partial fulfillment of the requirements for the degree of

Master of Science

David A. Penry, Chair Mike J. Wirthlin Brad L. Hutchings

Department of Electrical and Computer Engineering

Brigham Young University

December 2013

Copyright © 2013 Zhuo Ruan All Rights Reserved

#### **ABSTRACT**

Interface Design and Synthesis for Structural Hybrid Microarchitectural Simulators

Zhuo Ruan

Department of Electrical and Computer Engineering, BYU

Master of Science

Computer architects have discovered the potential of using FPGAs to accelerate software microarchitectural simulators. One type of FPGA-accelerated microarchitectural simulator, named the hybrid structural microarchitectural simulator, is very promising. This is because a hybrid structural microarchitectural simulator combines structural software and hardware, and this particular organization provides both modeling flexibility and fast simulation speed. The performance of a hybrid simulator is significantly affected by how the interface between software and hardware is constructed. The work of this thesis creates an infrastructure, named Simulator Partitioning Research Infrastructure (SPRI), to implement the synthesis of hybrid structural microarchitectural simulators which includes simulator partitioning, simulator-to-hardware synthesis, interface synthesis. With the support of SPRI, this thesis characterizes the design space of interfaces for synthesized hybrid structural microarchitectural simulators and provides the implementations for several such interfaces. The evaluation of this thesis thoroughly studies the important design tradeoffs and performance factors (e.g. hardware capacity, design scalability, and interface latency) involved in choosing an efficient interface. The work of this thesis is essential to the research community of computer architecture. It not only contributes a complete synthesis infrastructure, but also provides guidelines to architects on how to organize software microarchitectural models and choose a proper software/hardware interface so the hybrid microarchitectural simulators synthesized from these software models can achieve desirable speedup.

Keywords: hybrid microarchitectural simulator, software/hardware codesign, SystemC, FPGA

## **ACKNOWLEDGMENTS**

First of all, I would like to thank my advisor, David A. Penry, for his support and mentoring. He founded the BYU Architecture Design, and Description (BARDD) group in 2007 and has provided an exciting environment for me and others to explore research and development of CAD tools to support hybrid microarchitectural simulation.

Thanks also go to Brigham Young University and NSF grant # CCF-1017004.

I'd also like to thank Trevor Meyerowitz, my colleague at Tensilica, for his generous comments on improving the writing of this thesis.

Finally, a special thank-you goes to my wife (Rachel Yu Liu) and my parents (Yongtie Ruan and Chune Jiang). I can't ever make it this far without their care and support. They sacrificed their dreams for mine.

# **Table of Contents**

| Li | st of '         | <b>Fables</b>                 |                                                                     | vii |

|----|-----------------|-------------------------------|---------------------------------------------------------------------|-----|

| Li | List of Figures |                               |                                                                     |     |

| 1  | Intr            | oductio                       | n                                                                   | 1   |

|    | 1.1             | The Sy                        | ynthesis Problem of Hybrid Structural Microarchitectural Simulators | 3   |

|    |                 | 1.1.1                         | Challenge 1: Simulator Partitioning                                 | 4   |

|    |                 | 1.1.2                         | Challenge 2: Hardware Synthesis                                     | 5   |

|    |                 | 1.1.3                         | Challenge 3: Software/Hardware Interface Synthesis                  | 7   |

|    | 1.2             | Resear                        | rch Objectives and Contribution                                     | 8   |

|    | 1.3             | Organi                        | ization of the Dissertation                                         | 9   |

| 2  | Mic             | Microarchitectural Simulation |                                                                     |     |

|    | 2.1             | Microa                        | architectural Simulator Design                                      | 10  |

|    |                 | 2.1.1                         | Design Tools                                                        | 12  |

|    |                 | 2.1.2                         | Design Organization                                                 | 13  |

|    | 2.2             | Micro                         | architectural Simulator Acceleration                                | 15  |

|    |                 | 2.2.1                         | Software Parallelization                                            | 16  |

|    |                 | 2.2.2                         | Hardware Parallelization                                            | 17  |

| 3  | Hyb             | rid Mic                       | eroarchitectural Simulation                                         | 19  |

|   | 3.1 | Host Pl   | latform for Hybrid Simulation                        | • | 19 |

|---|-----|-----------|------------------------------------------------------|---|----|

|   |     | 3.1.1     | FPGA                                                 |   | 20 |

|   |     | 3.1.2     | FPGA-based Host Platform                             |   | 22 |

|   | 3.2 | Previou   | us Hybrid Microarchitectural Simulators              |   | 27 |

|   |     | 3.2.1     | Hybrid Function-Timing Simulator                     |   | 27 |

|   |     | 3.2.2     | Hybrid Transplanting Simulator                       |   | 28 |

|   |     | 3.2.3     | Hybrid Structural Simulator                          |   | 29 |

|   |     | 3.2.4     | Discussion                                           |   | 29 |

| 4 | SPR | I: Simu   | lator Partitioning Research Infrastructure           |   | 31 |

|   | 4.1 | SPRI I    | nput                                                 |   | 32 |

|   |     | 4.1.1     | SystemC                                              |   | 32 |

|   |     | 4.1.2     | Partitioning Specification                           |   | 34 |

|   | 4.2 | SPRI C    | Output                                               |   | 35 |

|   | 4.3 | SPRI H    | Host Platform                                        |   | 37 |

|   | 4.4 | SPRI C    | Organization                                         |   | 37 |

|   |     | 4.4.1     | LLVM Compiler Framework                              |   | 38 |

|   |     | 4.4.2     | SPRI Synthesis Flow                                  |   | 39 |

| 5 | SPR | I Interfa | ace Generation                                       |   | 42 |

|   | 5.1 | Design    | Space                                                |   | 43 |

|   |     | 5.1.1     | Concurrency                                          |   | 43 |

|   |     | 5.1.2     | Composition                                          |   | 44 |

|   |     | 5.1.3     | Combining the Dimensions: the Interface Design Space |   | 45 |

|   | 5.2 | Implen    | nentation                                            |   | 47 |

|   |     | 5.2.1     | Blocking, No Composition (BL-NONE)                   |   | 48 |

| Bibliography |     | 63      |                                                     |    |

|--------------|-----|---------|-----------------------------------------------------|----|

| 6            | Con | clusion | s and Future Directions                             | 62 |

|              | 5.3 | Evalua  | ation                                               | 56 |

|              |     | 5.2.5   | Non-blocking, Multi-FPGA-cycle Composition (NB-MC)  | 54 |

|              |     | 5.2.4   | Non-blocking, Single-FPGA-cycle Composition (NB-SC) | 53 |

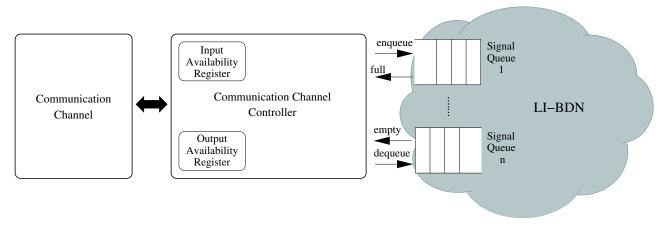

|              |     | 5.2.3   | Non-blocking, No Composition (NB-NONE)              | 51 |

|              |     | 5.2.2   | Blocking, Single-FPGA-cycle Composition (BL-SC)     | 50 |

# **List of Tables**

| 1.1 | Performance of software-only cycle-level simulators [5]                                    | 2  |

|-----|--------------------------------------------------------------------------------------------|----|

| 1.2 | List of high-level language constructs commonly used in software microarchitectural models | 6  |

| 5.1 | The interface design space                                                                 | 45 |

# **List of Figures**

| 2.1 | Trade-offs for microarchitectural simulator design [9]     | 11 |

|-----|------------------------------------------------------------|----|

| 2.2 | Example: model and implementation of 1-bit adder           | 12 |

| 2.3 | Microarchitectural simulator organization [13]             | 14 |

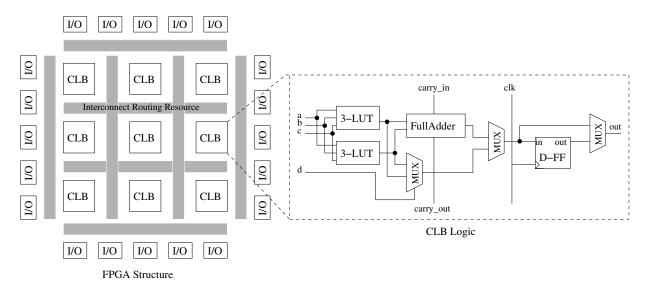

| 3.1 | Simplified FPGA structure and CLB logic                    | 21 |

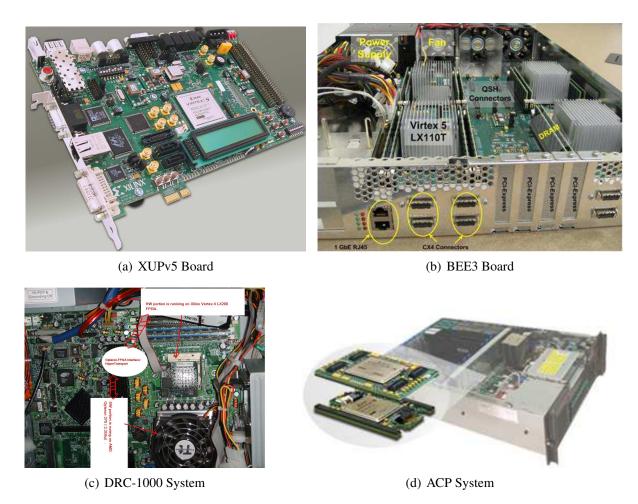

| 3.2 | Several host simulation platforms                          | 22 |

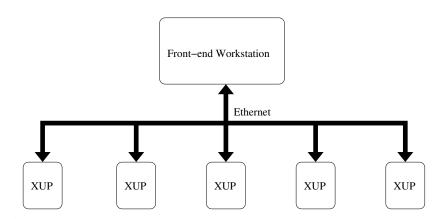

| 3.3 | A high-level view of an XUP-based platform (i.e RAMP Gold) | 24 |

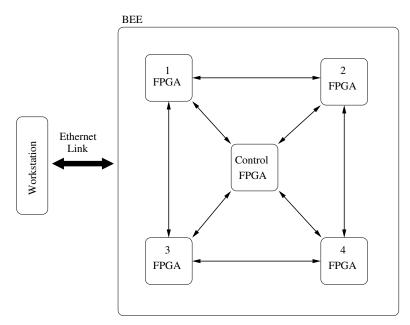

| 3.4 | A high-level view of BEE-based platform                    | 25 |

| 3.5 | A high-level view of DRC                                   | 25 |

| 3.6 | A high-level view of ACP                                   | 26 |

| 4.1 | Pseudo-code of the SystemC main loop                       | 34 |

| 4.2 | Partitioning specification examples                        | 35 |

| 4.3 | SPRI synthesis flow                                        | 39 |

| 4.4 | SPRI simulator partitioning                                | 41 |

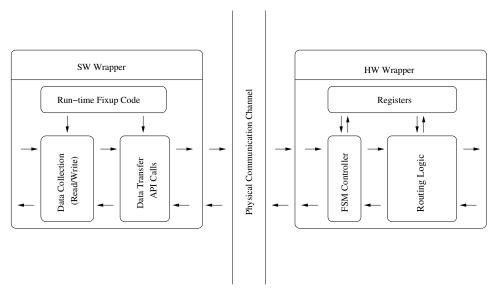

| 5.1 | SPRI-synthesized LI-BDN wrapper [45]                       | 46 |

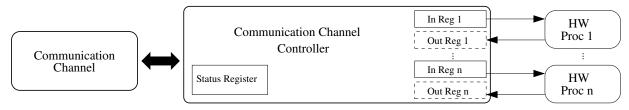

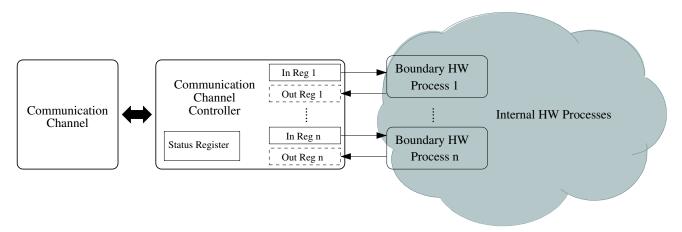

| 5.2 | The abstract form of the SystemC/FPGA interface            | 47 |

| 5.3 | BL-NONE interface: software side                           | 49 |

| 5.4 | BL-NONE interface: hardware side                           | 49 |

| 5 5 | BL-SC interface: software side                             | 50 |

| 5.6  | BL-SC interface: hardware side                  | 51 |

|------|-------------------------------------------------|----|

| 5.7  | NB-NONE interface: software side                | 52 |

| 5.8  | NB-MC interface: software side                  | 54 |

| 5.9  | NB-MC interface: hardware side                  | 55 |

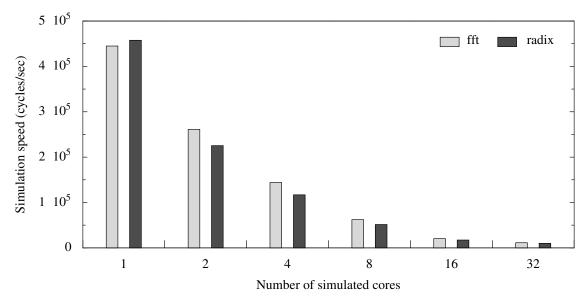

| 5.10 | Software-only simulation speed                  | 57 |

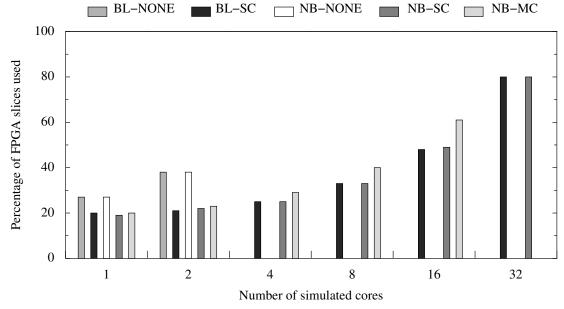

| 5.11 | FPGA slice utilization                          | 57 |

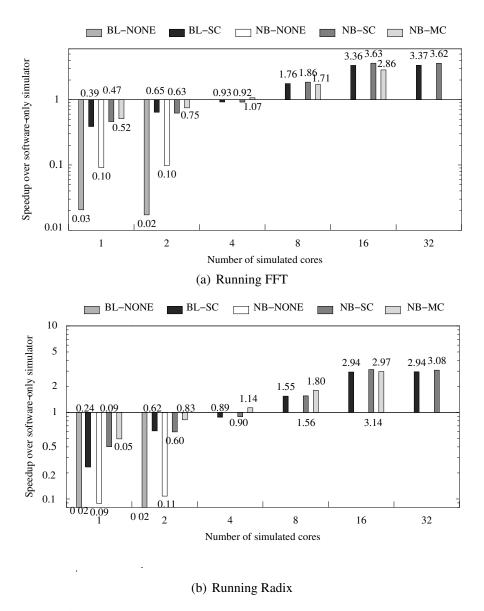

| 5.12 | Speedup of hybrid over software-only simulation | 58 |

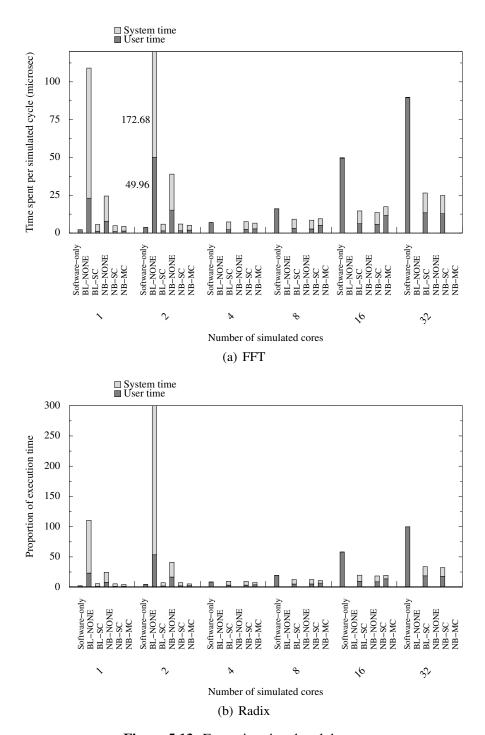

| 5.13 | Execution time breakdowns                       | 59 |

# Chapter 1

# Introduction

Microprocessors are everywhere around us! They are widely used in designing digital electronic products such as desktops, smartphones, TVs, home security systems, and wifi routers. In these products, multiple microprocessor cores can be integrated in a System On Chip (SOC) where typically a central controller offloads tasks (e.g. audio, image, network) to special-purpose processor cores. These cores can be easily programed and reprogrammed with high-level languages (i.e. C, C++) after fabrication which significantly increases design productivity and improves time-to-market when they are compared with application-specific integrated circuits (ASICs).

Multiple microprocessors may be planned for a single product. For each microprocessor, computer architects must consider many design alternatives. An efficient way to evaluate each design candidate is constructing a microarchitectural model (also known as a microarchitectural simulator). The execution result of a microarchitectural model can predict the timing and the functionality of a microprocessor design. Microarchitectural models must be easy to create and flexible to modify so that architectural changes can be quickly added. Traditionally, architects choose to verify microarchitecture designs through software simulation rather than hardware prototyping for two reasons. First, the creation of software models is less time-consuming. Second, these software models are easier to create, modify, and debug.

Microarchitectural models are different from physical microprocessor designs or prototypes; they abstract the implementation of a microprocessor design to a higher level. A microarchitectural simulator doesn't necessarily model every implementation detail as a hardware prototype does, but it must capture how target instructions are processed at each simulated cycle in order to be cycle-accurate. A software microarchitectural simulator is typically running on a host platform which can be either a server or a computer workstation. It loads an executable binary for the simulated system and virtually executes each instruction of this binary through the microarchitectural

**Table 1.1:** Performance of software-only cycle-level simulators [5]

| Simulator    | Instruction-set Architecture | Microarchitecture | Speed      | OS  |

|--------------|------------------------------|-------------------|------------|-----|

| Intel        | x86-64                       | Core 2            | 1 - 10 KHz | Yes |

| AMD          | x86-64                       | Opteron           | 1 - 10 KHz | Yes |

| IBM          | PowerPC                      | Power5            | 200 KIPS   | Yes |

| Freescale    | PowerPC                      | e500              | 80 KIPS    | No  |

| PTLSim       | x86-64                       | Athlon            | 270 KIPS   | Yes |

| Sim-outorder | Alpha                        | 21264             | 740 KIPS   | No  |

| GEMS         | Sparc                        | Generic           | 69 KIPS    | Yes |

model. This dissertation refers to the system being simulated as the target, the platform where the simulation runs on as the host, and the target executable binary as the benchmark.

Software microarchitectural simulators are commonly written in either sequential languages (e.g. C, C++) [1] or structural simulation frameworks (e.g. SystemC [2], Unisim [3], LSE [4]). However, it is more difficult to create timed processor models with sequential languages due to the lack of language constructs that can capture structural and timing features. By contrast, structural simulation frameworks allow the rapid creation of microarchitectural models in a concurrent and structural form that accurately mimics hardware behaviors. Unfortunately, the productivity advantage of structural modeling comes at the cost of simulation performance, because processing structural and timing constructs (e.g. signal, event, process) in software simulation introduces significant execution overhead.

Typically, simulation speed is measured by the number of target instructions executed per second (IPS) or simulated cycles per second (Hz). As target systems become more and more complex, their microarchitectural simulators are increasingly slowing down. Table 1.1 lists the software cycle-accurate or near-cycle-accurate simulators of several modern complex single-core processors. The speed of these simulators are at the level of KIPS or KHz. Simulating a processor of hundreds of cores with similar modeling details would cause a significant speed drop to the level of IPS or Hz. The simulation speed is so much slower than the speed of the physical processor that a relatively complex benchmark that a physical processor can finish in several minutes may take days or weeks to run in software simulation. Architects have become increasingly concerned with this problem, because the slower simulation speed results in a slower evaluation process and fewer design candidates can be evaluated.

Architects have advocated accelerating microarchitectural simulators by moving simulation workloads to hardware, because thousands of host processor cycles spent on fetching, decoding, and executing host instructions can be effectively reduced to a few cycles of hardware work. Hardware-accelerated simulators can be either fully-implemented or partially-implemented in hardware. A microarchitectural simulator that is partially implemented in hardware is named a hybrid microarchitectural simulator. A hybrid microarchitectural simulator is composed of a software portion, a hardware portion, and a software/hardware interface. Hybrid microarchitectural simulators are particularly interesting, because they allow trade-offs to be made between hardware capacity, ease of implementation, and simulator performance. A promising type of hybrid microarchitectural simulator is the hybrid structural simulator. Such a design combines the benefits of structural modeling and hardware acceleration.

Manually designing a hybrid simulator is very costly in that a great amount of time and efforts has to be spent on circuit implementation and interface construction. The inefficient design process extensively restricts the use of hybrid simulators in practice. This thesis starts with discussing the issues and challenges of the synthesis of hybrid structural microarchitectural simulators. This thesis primarily focuses on the interface design and synthesis techniques and explores the interface design space. The evaluation of this work thoroughly studies the important performance factors and design trade-offs (i.e. hardware capacity, interface latency, interface bandwidth, and scalability to simulate multiple processor cores) involved in choosing an efficient software/hardware interface for synthesized hybrid structural microarchitectural simulators.

## 1.1 The Synthesis Problem of Hybrid Structural Microarchitectural Simulators

Hybrid structural microarchitectural simulators combine the benefits of structural modeling and hardware acceleration. However, the time-consuming design process restricts their use in practice. A more efficient way to create hybrid structural microarchitectural simulators would be through an automatic synthesis process.

The synthesis of hybrid structural microarchitectural simulators is challenging. The synthesis techniques for general software/hardware codesign cannot be applied directly for hybrid simulators, although they have been researched for many years. This is because hybrid microarchitectural simulators are written and organized in a different fashion from general software/hard-

ware co-design systems. A wide range of general software/hardware co-design projects target data-intensive systems. These designs are typically partitioned in a certain way that the control logic is kept in software and the computational portion is accelerated in hardware. Unlike those designs, microarchitectural simulators have extensive data and control dependencies between simulator modules, and they commonly use a great amount of high-level language constructs to provide coding efficiency, modeling flexibility, and design productivity. Those features have caused many difficulties in the synthesis of hybrid microarchitectural simulators, because they can not be directly mapped to hardware.

# 1.1.1 Challenge 1: Simulator Partitioning

Simulator partitioning is challenging for two reasons. First, where a hybrid simulator is partitioned significantly affects performance [6]. Second, it should be flexible to change the partitioning boundaries so architects can explore arbitrary partitionings before selecting the best one to proceed. Simulator partitioning splits a microarchitectural simulator into a software portion and a hardware portion. The software portion and the hardware portion communicates with each other through an interface. A poor software/hardware interface boundary may cause extensive overhead on the interface and thereby leads to a hybrid simulator that runs even slower than a software simulator.

1. Where to partition. The software/hardware partitioning impacts three aspects in a hybrid simulator design: the amount of data that needs to be communicated, the amount of parallelism that can be exploited, and the amount of hardware that is used. Microarchitectural simulators have a great amount of data and control dependency between simulator modules. Simulator modules must frequently communicate with each other for synchronization. No matter how a microarchitectural simulator is partitioned, the software portion and the hardware portion must update processor state consistently to guarantee a correct execution sequence of target instructions. A ideal partitioning should place closely-dependent modules on the same side (either software or hardware) to minimize synchronization cost, and it also should place enough modules in hardware to achieve maximum speedup. However, the ideal partitioning may not stay the same for every hybrid simulator design in practice. For example, when accelerating a single-core model, one would prefer moving as much as

possible to hardware in order to reduce the communication overhead. This partitioning may not work effectively for a many-core model; a better partitioning option here would have a smaller portion of each core implemented in hardware with the parallelism between cores exploited to improve performance.

2. **Partitioning flexibility.** To provide the opportunity of exploring different hybrid simulators, a partitioning technique should support simulator partitioning along arbitrary boundaries. The more partitioning options architects have, the better decisions they can make on how to pick the best hybrid design.

Partitioning flexibility allows different trade-offs to be made between the software and the hardware. These trade-offs exist, because simulator partitioning is constrained by both the hardware capacity and the synthesis capability. It is significantly beneficial to provide partitioning flexibility so architects are able to avoid dealing with the simulator portions that are either currently "unsynthesizable" or do not fit in the hardware.

How one partitions a microarchitectural simulator for the "hybrid" transformation depends on what this simulator models, how it is organized, and what host platform it runs on. Because architects are aware of all the details of how target simulators are written and which host platform is chosen, it may be better for architects to explore partitioning alternatives and find the best solution rather than replying on an automatic partitioning-selection process. Thus, our insfrastructure is designed to fit this need. The partitioning process is automatic but the partitioning decision and exploration are left to users.

## 1.1.2 Challenge 2: Hardware Synthesis

The hardware synthesis of hybrid structural microarchitectural simulators is challenging, because some high-level language constructs used in software microarchitectural models can not be directly and properly mapped to hardware descrption languages. To guarantee the functional and timing correctness of microarchitectural simulator after synthesis, novel techniques are required to interpret and translate high-level language features to hardware.

Typically, architects model microarchitectures in a structural simulation framework such as SystemC [2]. SystemC models are written with a great amount of high-level language constructs

to permit code reuse and coding efficiency. Table 1.2 list a set of high-level language features that are commonly used in SystemC microarchitectual models. For example, complex data with nested struct/array types can be used to contain the state information of each pipeline stage or decoded instruction information; a templated SystemC module class can be used for register modeling so the registered data can be different types for different register instances; command-line arguments offer a flexible way to parametrized the number of simulated processor cores, cache size, or register-file depth.

**Table 1.2:** List of high-level language constructs commonly used in software microarchitectural models

| Construct Category    | Construct Example                                                                               | Construct Usage                                                                              |  |

|-----------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|

| Complex Data Types    | Nested struct/Array, Vector, List, etc.                                                         | Signal data type, Register type, Decoded instruction information, Pipeline stage state, etc. |  |

| Command-line Argument | Dynamic-allocated pointer, etc.                                                                 | Cache size, Register-file size, Processor core number, etc.                                  |  |

| Code Reuse            | Template, Virtual methods, Class inheritance, Operator overload/override etc.                   | Register, Buffer, Instruction/data memory, etc.                                              |  |

| Coding Efficiency     | Shared variable, Pointer, Reference, Global variable, Cross-object call, Function pointer, etc. | Module state, Pipeline state, State lookup, etc.                                             |  |

| Complex Operation     | Multiply operator, Shift operator, Division operator, etc.                                      | ALU, Memory address/data manipulation, etc.                                                  |  |

| Complex Control Flow  | Non-bounded loop, Nested loop, Break, Continue, etc.                                            | TLB, Cache lookup, Tag compare, etc.                                                         |  |

These high-level language features are problematic in synthesis for two reasons. First, it is difficult to determine statically what exactly the code and data to synthesize are. Second, there are no equivalent HDL constructs that they can be directly mapped to. We solve these problems by using a run-time synthesis technique to automatically produce VHDL [7] from SystemC. This technique offers accesses to in-memory simulator objects at runtime after elaboration and applies a set of dynamic and static analysis for code identification and optimization. During the synthesis, it interprets high-level language contructs based on the context where they are used and output VHDL code with equivalent functionality and timing.

# 1.1.3 Challenge 3: Software/Hardware Interface Synthesis

The software/hardware interface design is constrained by both partitioning and hardware synthesis capability. The software/hardware interface synthesis of hybrid structural microarchitectural simulators is challenging, because this process must automatiaclly produce both software interface code and hardware interface code for user-specified partitioning boundaries. Most importantly, the synthesized interface must synchronize processor state cross the software/hardware boundary correctly and efficiently. A poor interface would introduce extensive communication overhead or consume too much hardware resource. To develop a technique for the interface synthesis, three important traits regarding the interface design must be properly addressed.

- Correctness. A usable interface for hybrid microarchitectural simulator must be correct.

In another word, simulator states transferred between the software and the hardware must be correct, and the timing of state updates on both sides must be correct. Incorrect data and timing of simulator state synchronization will cause simulation failure or inaccurate performance prediction.

- 2. Concurrency. Interface concurrency is of great importance, because it reduces communication overhead by exploiting parallelsim in simulator execution and leads to the improvement of simulator performance. The coprocessor-style interface, also known as a polling interface, is the most commonly-used interface [8] for software/hardware co-design systems. Through such an interface, the software blocks to wait till the hardware finishes processing and polls the hardware results back. Due to lack of concurrency, a polling interface does not work efficiently for hybrid microarchitectural simulators where an extensive amount of dependencies exists between software modules and hardware modules. The execution of any one of them may require a synchronization request to cross the interface. To overcome these drawbacks, an optimized interface should overlap communication and computation and exploit not only the parallelism that is internal to the hardware but also the parallelism between the software and the hardware.

- 3. **Scalability.** Scalability is a significant concern when we are synthesizing interfaces for hybrid simulators. Interface scalability can be evaluated in two aspects: hardware cost and

bandwidth cost. Both hardware cost and bandwidth cost will rise, when the amount of information shared between the software and the hardware increases. The increased communication traffic leads to a higher interface overhead. Eventually the overhead will reach a point that it cannot be mitigated anymore by the speedup achieved through the hardware acceleration; then the hybrid simulation becomes slower than the software-only simulation. Every interface design has a bottleneck like this. It is necessary to understand the bottlenecks of different interfaces, because the insights can provide guidelines for architects on where to partition a software simulator in order to achieve desirable speedup but within their hardware budget.

As a matter of fact, various interface designs can be used for hybrid structural microarchitectural simulators, as long as they provides correct synchronization. The primary research questions we should answer are:

- 1. what interfaces can be applied for hybrid structural microarchitectural simulators;

- 2. how these interfaces can be automatically generated;

- 3. which one is better and why.

# 1.2 Research Objectives and Contribution

A good partitioning scheme, a complete synthesis strategy, and an efficient interface design combine to produce a high-performance hybrid simulator. The work of this thesis is the first effort to synthesize hybrid structural microarchitectural simulators, but this thesis primarily discusses how we solve the problem of interface design and synthesis for hybrid structural microarchitectural simulators. Our contributions are:

- 1. identifying the design space of interfaces for synthesized hybrid structural microarchitectural simulators.

- 2. providing synthesis techniques for several such interfaces in the design space.

- 3. determining the trade offs between simulator performance and hardware utilization which must be considered when choosing an interface design.

A complete infrastructure, named Simulate Partitioning Research Infrastructure (SPRI), has been also contributed to automatically produce hybrid structural microarchitectural simulators from existing software simulators. We demonstrate these contributions by implementing the synthesis of several such interfaces within the SPRI infrastructure. This capability provides an unique opportunity for this thesis to thoroughly analyze a set of synthesized hybrid structural microarchitectural simulators and evaluate scalability v.s. trade-offs between hardware capacity, interface latency, and interface bandwidth. The insights of this study are essential. They can lead to better decisions on how to organize a simulator, how to partition a simulator, and how to choose an interface, no matter whether architects are planning on applying SPRI to generate equivalent hybrid simulators or manually creating hybrid simulators from scratch.

# 1.3 Organization of the Dissertation

This thesis starts by introducing microarchitectural simulation and discussing the motivation for and issues of hybrid microarchitectural simulators. It then presents the SPRI infrastructure. It primarily focuses on discussing the design space of interfaces for hybrid structural microarchitectural simulators and the interface synthesis techquies. The experimental results demonstrates the interface design trade-offs and the performance scalability for synthesized hybrid structural microarchitectural simulators.

Chapter 2 introduces the concept of microarchitectural modeling and the different modeling methodologies. It also discusses the acceleration methods for software microarchitectural simulators. Chapter 3 presents background information about hybrid microarchitectural simulators. It introduces several host platforms for hybrid simulation and examines the previous works of manually-created hybrid microarchitectural simulators. Chapter 4 displays the developed infrastructure, discusses the synthesis flow, and reveals the primary components of this tool-chain. Chapter 5 explores the interface design space, discusses the synthesis techniques for each interface in the design space, and conducts a thorough analysis and study on the interface evaluation results. Chapter 6 summarizes and concludes this thesis.

# Chapter 2

# **Microarchitectural Simulation**

Microarchitectural simulation allows architects to evaluate novel ideas without implementing a physical microprocessor. Microarchitectural simulators typically model both functional and timing behaviors of a microprocessor, and thereby are capable of predicting the performance. Like a hardware prototype, microarchitectural simulators execute processor instructions in simulation but they abstract target processor designs at microarchitectural level rather than register-transfer level or gate level. As a result, microarchitectural models implement fewer design details and can be created more rapidly than hardware prototypes, which significantly shortens the evaluation phase of target processor designs.

Microarchitectural simulators can be classified in two categories based on the inputs: trace-driven and execution-driven. A trace-driven simulator executes prerecorded streams of instructions with some fixed input and only needs to maintain the microarchitectural state. An execution-driven simulator executes instructions dynamically depending on the inputs and must track architectural state in addition to microarchitectural state. Execution-driven simulation can capture the dynamic properties of target benchmarks. The microarchitectural simulators discussed in this dissertation refer to execution-driven simulators. They run on a host platform and start simulation by loading a binary of target instructions.

## 2.1 Microarchitectural Simulator Design

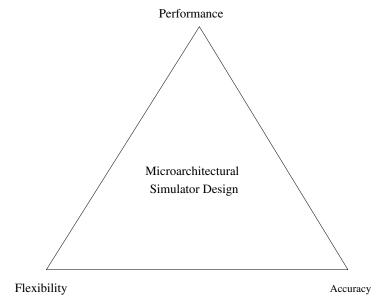

A microarchitectural simulator is evaluated based on three criteria: speed, accuracy, and flexibility [9]. All three criteria are expressed as a triangle in Figure 2.1 and they can't be fully achieved at the same time in a simulator design. A good microarchitectural simulator design must balance the trade-offs between these three criteria. Hardware prototypes are accurate but slow and

not flexible; detailed software models are accurate and flexible but slow; abstract software models are fast and flexible but not accurate.

**Figure 2.1:** Trade-offs for microarchitectural simulator design [9]

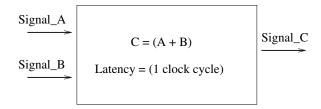

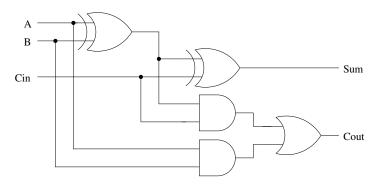

Microarchitectural simulators are different from hardware prototypes. They are modeled at a higher-abstraction level in order to capture important processor behaviors but obtain simulation efficiency at the same time. Higher-level abstraction in a simulator design is desired to improve clarity and speed. Because a microprocessor is a timed logic design, what matters to the correctness of microarchitectural models is the value changes of signals at each clock edge. This fact makes modeling within-clock-cycle behaviors for each wire of a microprocessor unnecessary [10]. Figure 2.2 diagrams a adder example to demonstrate the difference between modeling and hardware implementation. A 1-bit adder model can be simply be created as an addition operation on two integers with a latency rather than a collection of gate-level logic blocks. The microarchitectural model effectively expresses the timing and the functionality of this operation and can be easily created with high-level computer languages.

(a) Microarchitectural Model of One-bit Adder

(b) Gate-level Implementation of One-bit Adder

**Figure 2.2:** Example: model and implementation of 1-bit adder

## 2.1.1 Design Tools

Microarchitectural simulators are commonly written as software models. Software models run on servers or workstations, and can be easily programed or reprogrammed for design adjustment. Software modeling, therefore, offers more flexibility than hardware does. Sequential languages such as C and C++ [1] are widely applied in microarchitectural modeling, because architects are very familiar with them. Sequential languages semantically mismatch the structural and concurrent form of target systems which leads to increased simulator design and validation time as well as inflexibility. It is possible to model concurrent behaviors through a global scheduler which manages a sequential execution order for a logically-concurrent simulator, however, it results in a more complex simulator which increases the difficulty of understanding and debugging the simulator code [11]. The modeling complexity with sequential languages grows extensively when target microarchitectures scale to many cores and increased system integration.

The limitation of sequential languages has led architects to use structural simulation frameworks (e.g. SystemC [2], Unisim [3], LSE [4]) for modeling. These frameworks provide users with structural and concurrent constructs to create models that naturally mimic hardware behav-

iors. Structural microarchitectural simulators can be created in a hierarchical fashion through simulator modules. A simulator module typically consists of one or several concurrent processes. The processes in the same module or different modules can be interconnected through signals and they are invoked to produce outputs when clock edges arrive or input changes are detected. Structural simulation frameworks, unfortunately, have to trade off simulator performance for the modeling productivity [12]. A significant amount of overhead is introduced in the execution of structural simulators, because the simulation kernels must maintain signal updates, invocation sequences, etc. Most structural simulation frameworks also allow the use of object polymorphism and non-structural constructs (e.g. shared/global data structure, cross-object call) to permit code reuse, increase modeling flexibility, and improve simulation speed. As a result, structural microarchitectural models are usually formed from a wide range of high-level language constructs including both structural and non-structural ones.

## 2.1.2 Design Organization

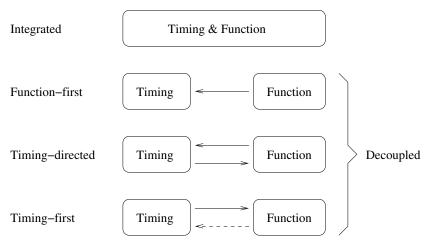

A microarchtectural simulator primarily models two aspects of a target microprocessor: functionality and timing. Functionality refers to the execution correctness of target instructions and timing strives to reproduce the execution latency of target instructions at each processing stage. The organization of a microarchitectural simulator reflects how the simulation of functionality and the simulation of timing interact with each other. Commonly, microarchitectural simulators can be classified in two base organizations as displayed in Figure 2.3: integrated and decoupled. Different simulator organizations emphasize different design goals: accuracy, speed, or flexibility.

A microarchitectural simulator can be written in a integrated fashion as a phyical microprocessor design where functionality and timing are tightly coupled. Microarchitectural simulators designed in this fashion can be very accurate, but at the cost of design flexibility. Integrated simulator allows the modeling of detailed operations for all system components. These system components closely interact with each other and simulation states of each module must be frequently updated. Integrated microarchitectural simulators will become more and more difficult to design and debug with the increasing complexity of target systems.

A microarchitectural simulator can also be organized in a decoupled fashion. The simulator is split into a functional portion and a timing portion and they communicate with each other for

Figure 2.3: Microarchitectural simulator organization [13]

synchronization. Doing so addresses functional accuracy and timing accuracy in separate code and reduces modeling complexity. The functional model simulates each target instruction by executing an equivalent code-routine on the host, the process of which is therefore named instruction-set simulation. The timing portion models timing-related components (e.g. pipeline, memory hierarchy, branch predictor) of the target microprocessor to calculate execution latency for each target instruction through microarchitectual simulation. Based on different synchronization mechanism between the functional model and the timing model, decoupled simulators can be categorized as functionalfirst, timing-directed, or timing-first. In a functional-first simulator, the functional model generates a sequence of committed target instructions and feeds it to the timing model. One-way communication from the functional model to the timing model makes the simulator easy to design and fast to execute; however, this fashion can not capture timing-dependent outcomes like branch misprediction. A type of functional-first simulator — the speculative functional-first simulator is introduced to solve this problem [14]: the functional model speculatively executes instructions and is rolled back to re-execute only if the branch prediction of the functional model does not match that of the timing model. In a timing-directed simulator, the timing model gives explicit orders to the function model at certain timestamps on what behaviors to simulate (e.g. instruction fetch, instruction decode, and instruction commit). This timing-directed fashion increases simulator accuracy at the cost of simulator speed and complexity. A timing-first simulator, on the other hand, allows the timing-model to execute timing-dependent (dynamic) instructions ahead of the function portion.

The timing portion must be modeled with enough microarchitectural detail to support speculative execution and the functional portion will be invoked to check for execution deviations. A timing-first simulator can also be thought of as a near-complete integrated microarchitectural simulator plus a functional checker.

The split of the functional model and the timing model simplifies dependency between simulator modules and reduces modeling complexity. There is no absolute answer to which organization is the best, however, the choice of simulator organization does reflect architects' emphasis on accuracy, speed, and flexibility.

# 2.2 Microarchitectural Simulator Acceleration

Microarchitectural simulation often takes days or weeks to run in software. The faster simulation runs, the more design alternatives can be evaluated. Software microarchitectural modeling permits a fast and flexible evaluation process for new computer designs, however, the simulation speed increasingly slows down when target computer systems scale to many-core or increased system-integration designs. A significant amount of effort has been devoted to improving the performance of microarchitectural simulators. Software microarchitectural simulators can be accelerated typically in two ways, either by reducing simulator workloads or by pursuing execution parallelism.

Two techniques that can effectively reduce simulator workloads are input-stream shortening [15, 15] or sampling simulation [16, 17, 18, 19]. Input stream shortening leads simulators with fewer or smaller input sets instead of complete benchmarks. By contrast, a simulator that uses simulation sampling still executes a full benchmark, but it only cycle-accurately simulates samples of this benchmark and the instructions between those samples are fast-forwarded through functional simulation. The simulation-sampling technique usually requires simulators to have two simulation modes — a functional-simulation mode and a cycle-accurate model to switch during simulation. The simulators that use these workload-reduction techniques may not fully characterize the significance of the chosen benchmarks through the executed instructions, because they can not completely enumerate all the simulation states. Thus, the simulation speedup is achieved by sacrificing simulation accuracy.

Another method to accelerate microarchitectural simulation is to parallelize simulators (simulator parallelism). A microarchitectural simulator can be parallelized because it describes hardware behaviors that are considered naturally and logically concurrent. This concurrency can be internal to simulated modules, between simulated modules or between simulated cores. The research community of computer architecture has proposed two approaches to parallelize microarchitectural simulators: software parallelization and hardware parallelization. Software parallelization decomposes a simulator into multiple tasks that can be run in parallel. Hardware parallelization exploit finer-grain (gate-level) parallelism to speed up simulation by directly implementing simulators in circuits.

#### 2.2.1 Software Parallelization

A software microarchitectural simulator is parallelized by distributing decomposed simulator tasks to execute on different physical processors. The techniques of software paralellization can be categorized based on the granularity of the decomposed tasks.

- Microarchitectural Parallelization: each simulated processor core is mapped to a different physical processor for simulation and a separate processor is used to simulate the memory hierarchy [20, 21].

- Simulation Trace Parallelization: several copies of a simulator are run in parallel; a instruction trace is divided into equal-length chunks and each chunk is fed into one of the parallel simulators [22].

- Structural Parallelization: a structural simulator can be partitioned into a set of structural modules. This simulator is thereby transformed to a parallel program. The parallel program can be compiled and statically scheduled to run on a multiprocessor host platform with a shared memory [10, 23, 24].

Microarchitectural parallelization and simulation trace parallelization partition simulators into "naturally parallel" tasks which are limited in interacting with each other. They either ignore the communication between parallel portions or utilize a simplified scheme to reduce synchronization complexity and overhead. Both methods may cause incorrect simulation results due to the lack of state consistency between parallel portions.

Structural parallelization adopts a different approach. The method decomposes a structural simulator into a set of structural modules and relies on compiler techniques to find a fixed concurrent execution order for them. The discovered execution order must not change with input data. As a matter of fact, the simulator is transformed into a statically-compiled program that can be scheduled based on module dependency to run in parallel on a host multiprocessor. The simulation performance depends on the quality of the discovered schedule, and the performance improvement can be achieved without losing accuracy. Unfortunately, microarchitectural models tend to have an extensive amount of data and control dependency between simulator modules. The difficulty in finding an efficient static schedule grows dramatically with the increasing size and complexity of target computer systems. Finer-grain parallelism must be pursued to permit further performance enhancement.

#### 2.2.2 Hardware Parallelization

Instead of being implemented in software, a microarchitectural simulator can be designed directly with circuits in hardware. The hardware version of the simulator exploits finer-grain (gate-level) parallelism to accelerate simulation speed. A hardware-accelerated simulator can be significantly faster than a software simulator for two reasons:

- 1. Different modules of the software-only simulator can be executed in parallel in hardware. This is particularly true because the software is modeling hardware that is inherently parallel [25].

- 2. Individual modules of a software-only simulator become significantly faster when implemented in hardware. Several hundred software instructions can easily become one or two hardware cycles worth of work. Although hardware (i.e. FPGA) frequency is significantly lower than host CPU frequency, this speedup still occurs because overhead caused by instruction fetching and decoding is no longer necessary, and because fine-grain parallelism within a module can be exploited.

Two approaches have been proposed for hardware parallelization. The first approach [26] is to implement a microarchitectural simulator fully in hardware. The design process of a full-hardware microarchitectural model that can accurately simulate both functional and timing behav-

iors is difficult and time-consuming. It ends up implementing a multithreaded pipeline in hardware to execute target instructions issued from multiple cores, the design complexity of which is similar to a hardware prototype. The second approach [25, 14, 27] is a hybrid microarchitectural model where a portion of the simulator is moved to hardware, the other portion stays in software, and they communicate through a software/hardware interface. Hybrid simulators allow architects to select what to move into hardware based on simulator organization and hardware capacity. A hybrid simulator design scales better and offers more flexibility than a full-hardware design when target computer systems become increasingly complex. In a hybrid simulator, architects can simply keep the hardware-unfriendly portion in software and avoid spending a great amount of effort on hardware implementation. They can also mitigate the constraint of hardware capacity by reducing the size of the hardware partition at the cost of simulation performance. The design details of hybrid microarchitectural simulators are discussed in the next chapter.

# Chapter 3

# **Hybrid Microarchitectural Simulation**

An effective technique to accelerate software microarchitectural simulators is hardware parallelization. Hardware parallelization allows the pursuit of parallelism at a finer-granularity level through circuits and the circuit implementation only takes one or two hardware cycles to accomplish the amount of work that must require several hundred software instructions. The concurrency internal to simulated modules, between simulated modules or between simulated cores can all be explored to speed up simulation.

One group of hardware-accelerated microarchitectural simulators only implement portions of microarchitectural models in hardware, and therefore are named hybrid microarchitectural simulators. Hybrid microarchitectural simulators are very promising, because they allow trade-offs to be made between simulator speed, ease of implementation, and hardware resources. A hybrid microarchitectural simulator is composed of a software portion, a hardware portion, and a software/hardware interface for synchronization. It runs on a host platform that has a hardware accelerator attached to a computer workstation through a physical communication channel. The software portion is compiled and executed on the general-purpose processor of the computer workstation; the hardware portion is implemented as a circuit and ported to the hardware accelerator. The performance of a hybrid simulator is greatly influenced by the host platform in three aspects: hardware capacity, communication latency, and communication bandwidth. Hardware capacity decides the maximum amount of the moved-to-hardware portion; communication latency and bandwidth together set the minimum interface overhead for a hybrid simulator design.

# 3.1 Host Platform for Hybrid Simulation

Hybrid microarchitectural simulators must run on a host platform which consists of a general-purpose processor for the software portion, a hardware accelerator for the hardware por-

tion, and an communication channel for the software/hardware interface. Because the hardware accelerator and the communication channel significantly affect the performance of hybrid simulation, an ideal host platform must fulfill several requirements.

The hardware accelerator must allow the pursuit of fine-grain parallelism (i.e gate-level). Fine-grain parallelism fundamentally improves simulator performance by avoiding the costly execution process of host instructions in software. The hardware accelerators commonly used for data-intensive applications (i.e. GPU) are typically not suitable for hybrid microarchitectural simulators, because frequent synchronization between parallel threads serializes the execution. The hardware accelerator must also be flexible to "program" and "reprogram" similarly to software. This feature is necessary, because the architecture of a microprocessor under consideration may require a lot of adjustments which must be easily added for simulation during the evaluation phase.

The communication channel between the host processor and the accelerator must be efficient enough that the software/hardware interface built on top of it will not introduce an enormous overhead to overshadow the speedup obtained through the hardware accelerator. Both low latency and high bandwidth are desired for the communication channel. Lower latency shortens the round-trip cost for data transmission; higher bandwidth means a faster data-transfer rate so that a larger amount of data can be sent across the interface in a given time period.

Additional attention should be paid to the capacity of the hardware accelerator. A large hardware capacity allows more simulator modules to be implemented in hardware, and leads to a higher speedup. In fact, only one hardware accelerator may not be enough when the target computer system scales to a design with tens or hundreds of cores. The hardware extensibility of a host platform must be considered so that multiple accelerators may be stacked up in a host platform to expand the capacity.

#### 3.1.1 FPGA

Field Programmable Gate Arrays (FPGAs) are commonly-used hardware accelerators for hybrid microarchitectural simulation. An FPGA is a integrated circuit which allows logic configuration and reconfiguration after the chip has been manufactured [28]. FPGAs allow designers to improve simulator speed through circuit-level parallelism and to reconfigure circuit functionality based on microarchitectural changes. Like software, the design flexibility of FPGA offers the po-

tential to simply build and test design candidates repeatedly, thus resulting in a low nonrecurring engineering cost which well suits the design requirement of microarchitectural simulators.

Figure 3.1: Simplified FPGA structure and CLB logic

The basic FPGA architecture consists of configurable logic blocks (CLBs), interconnect routing resources, and I/O ports. A simplified FPGA architecture and CLB logic are shown in Figure 3.1. CLBs can be programmed with different logic functionality because of the built-in programmable units called lookup tables (LUTs). The computed result of each CLB can be registered by a D-type flip-flop and carried through other CLBs by customizing the routing connection with switches. CLBs and routing resource are distributed across the whole FPGA chip, thereby permitting the implementation of millions of operations spatially and simultaneously [29]. FPGAs can be programed using hardware description languages (HDLs) such as Verilog [30] and VHDL [7]. FPGA companies (e.g. Xilinx, Altera) and the third party EDA companies (e.g. Synopsys, Cadence) both provide sophisticated software development environments for FPGA development and simulation. Bitsteam files that describe circuit connection and functionality can be produced by those tools and downloaded to FPGAs for configuration and reconfiguration.

**Figure 3.2:** Several host simulation platforms

# 3.1.2 FPGA-based Host Platform

An FPGA-based host platform typically consists of a computer workstation and one or more FPGA accelerators. FPGA accelerators are connected to the computer workstation through a communication channel. The interconnection mechanism between FPGA and general-purpose processor determines the hardware extensibility (hardware capacity) and the communication performance (latency and bandwidth) which both significantly affect the design and efficiency of hybrid microarchitectural simulators. In this dissertation, FPGA-based host platforms are classified based on the interconnection mechanism: network connection, I/O connection, and CPU socket-level bus connection. Typically, network and I/O connects standalone FPGA boards (i.e.

Figure 3.2(a), Figure 3.2(b)) to the host; CPU socket-level bus connections are used in integrated systems (i.e. Figure 3.2(c), Figure 3.2(d)) to directly interface FPGAs with CPUs.

- 1. **Network Connection** Network connection allows workstations to interconnect in a sparse mesh fashion through network cables. Network connection offers great extendability, however, has relatively low bandwith and high latency. A commonly-used network connection is Ethernet connection. A standalone FPGA board typically provides one or more Ethernet ports for off board communication. In a Ethernet network, hundreds of FPGA boards can communicate with each other or the host. Typically, the Ethernet latency from a FPGA board to the host is in the range of hundreds of micro-seconds per round-trip, and the maximum bandwidth is commonly in the range of 10Mbs 1Gbs depending on the types of Ethernet network and the used Ethernet devices. Ethernet relies on complex protocols to provide reliable connections between workstations, but the complex transmission protocols introduce a large amount of processing overhead. Thus, an efficient interface between FPGAs and workstations for hybrid microarchitectural simulators can be constructed as a local-area network (LAN) running a simplified version of TCP/IP in order to reduce communication latency and overhead.

- 2. I/O Bus Connection Computer I/O buses provide communication channels between the computer host and peripherals. FPGAs can be considered as peripherals and connected to the host computer through computer I/Os. I/O sockets are placed on the motherboard of the host and peripherals can be directly plugged in. When compared with network connection, I/O connection has higher bandwidth and lower latency, but only a limited number of peripherals can be connected depending on available I/O slots. PCIe is one of the fast computer I/Os. The fastest version (v4.0) of PCIe connection permits a bandwidth up to 1969 MBs per lane (one direction). Most standalone FPGA boards provide PCIe ports to connect with host computers. The PCIe communication is typically memory-mapped and the communication protocol is significantly less complicated than TCP/IP. We measured the PCIe performance of a single PCI lane between a XUP board and a workstation. From the stand point of CPU, the bandwidth is 126 MB/s read and 27.9 MB/s write for 4 KByte transfers; the read latency is 1.6 micro-second minimum.

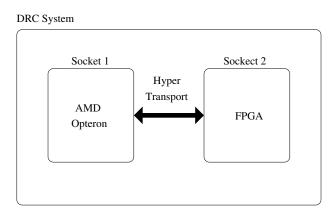

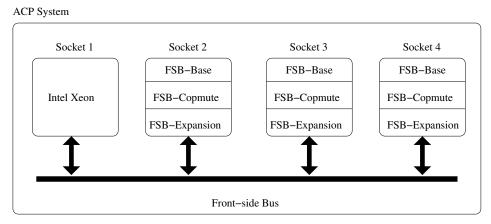

3. CPU Socket-level Bus Connection CPU socket-level buses are the communication channel to provide high-speed data transaction between CPUs and system memories. Different CPU manufacturers have different names for it. Intel names it the front-side bus (FSB); AMD calls it the HyperTransport bus. FPGA-based accelerators can be hooked up as coprocessors on CPU socket-level bus to directly communicate CPUs and access system memories. This bus connection has the shortest latency, but the extendability is very limited. The CPU socket-level bus can run faster than the I/O buses such as PCIe because the clock of the secondary buses is usually derived from the clock of CPU socket-level buses. We measured the HyperTransport performance on a DRC-1000 workstation. From the stand point of CPU, the bandwidth is 224 MB/s read and 354 MB/s write for 4 KByte transfers; the read latency is 1.4 micro-second minimum.

**Figure 3.3:** A high-level view of an XUP-based platform (i.e RAMP Gold)

Figure 3.2 shows several commonly used platforms in hybrid microarchitectural simulation. XUP [31] and BEE [32] are standalone FPGA accelerators. Both of them can be connected to host workstations through either ethernet or PCIe. DRC [33] and ACP [34] are integrated systems where FPGAs are hooked up via the CPU socket-level buses.

XUP is a single FPGA board and priced less than \$1000 for academic purchase. It is an affordable and scalable platform solution for hybrid microarchitectural simulation. The RAMP Gold simulator [26] runs on five XUP boards. These boards are not interconnected with each other but they are attached to the same front-end workstation through ethernet. A high-level view of this

Figure 3.4: A high-level view of BEE-based platform

host system is shown in Figure 3.3. Because the ethernet connection is relatively slow, people who adopts a similar organization for the host platform typically tend to move simulator modules to the hardware as much as possible in order to minimize off-board communication overhead. The RAMP Gold simulator can be ported to BEE. This board consists of five interconnected FPGAs: one FPGA is configured as a controller and the other four are processing units as in Figure 3.4. BEE has much higher hardware capacity than XUP, but at a much higher price (over \$10,000).

**Figure 3.5:** A high-level view of DRC

**Figure 3.6:** A high-level view of ACP

DRC and ACP provide a complete platform solution for hybrid microarchitectural simulation. DRC and ACP have FPGA accelerator modules directly plugged to additional CPU sockets as coprocessors. Most FPGA-integrated systems come with device APIs and pre-synthesized FPGA IPs to set up the communication between the host processor and FPGAs. FPGA-integrated systems have limited extendability, because only a small number of FPGA-accelerator modules can be added on board. DRC is a AMD-chip-based system. This system, as shown in Figure 3.5, has a two-socket Opteron server with one Opteron core replaced by an FPGA. The Opteron core and the FPGA are connected through the HyperTransport bus and no FPGA extension is allowed. ACP, by contrast, is a four-socket Intel server. ACP allows FPGAs to directly access system memory, but DRC does not. Users can populate all 4 sockets with different combinations of FPGA accelerators and Intel Xeon processors. Up to five FPGAs can be stacked up within a single socket and up to 3 sockets can be customized with FPGA accelerators. Nallatech [34] has been licensed to manufacture three modules for the ACP platform: FSB-base, FSB-compute, FSB-expansion. FSB-base is the interface board between the Intel front-side bus and FPGAs. FSB-compute is the FPGA accelerator board with two FPGAs and FSB-expansion is the accelerator extension board with only one FPGA. A high-level view of this platform is diagrammed in Figure 3.6. The UT-FAST hybrid simulator [14] was implemented first on a DRC-1000 system. The software portion of the simulator runs on the Opteron core and the hardware portion is implemented on the FPGA. The researchers of this project attempted to transplant the hybrid design to a ACP system, but reliability issues in

the ACP hardware caused data corruption during transfer and prevented them from running and measuring the performance of the entire system [35].

### 3.2 Previous Hybrid Microarchitectural Simulators

Three types of hybrid microarchitectural simulators have been advocated. In a hybrid function-timing simulator, the functional behavior of instructions is performed in software while the time it takes to execute an instruction is calculated in hardware. In a hybrid transplanting simulator, most behaviors of the simulator are implemented in hardware, but when a difficult-to-implement operation such as simulated I/O device behavior must be performed, the hardware calls upon the software to complete the operation. In a hybrid structural simulator, a collection of processes from a structural simulation model are implemented in hardware. The three hybrid microarchitectural simulators are partitioned differently which leads to different interface strategies.

### 3.2.1 Hybrid Function-Timing Simulator

Function-timing simulators are split into a functional portion and a timing portion. Simulation of instruction behavior and timing behavior are decoupled in this process and they must synchronize in some way to keep simulation states consistent on both sides. Several software-only simulators such as FastSim [36], Asim [37], and M5 [38] are partitioned in this fashion.

The UT-FAST project [14] has created a hybrid function-timing simulator with the function model in software and the timing model in hardware. The UT-Fast simulator is implemented on the DRC-1000 System. The functional portion runs on the Opteron core of the DRC box and simulates the instruction-set architecture and system calls. The timing portion is implemented on FPGA and models detailed actions of different pipeline stages to calculate execution latency. This strategy allows the software to run first and speculatively execute instructions; it feeds the hardware with instructions that has been executed; the hardware can roll back the software to reexecute instructions, if the software branch predictor and the hardware branch predictor mismatch each other. Thus, the cross-boundary interface is constructed in a asynchronous fashion using a commercial FPGA message passing interface (MPI) library; the software and the hardware communicate through asynchronous queues to provide execution concurrency. The average number

of round-trip communications is reduced to less than one per simulated clock cycle. The simulation speed is around 1.2 MIPS. UT-FAST didn't implement a baseline software simulator to compare against with so that it is impossible to evaluate the performance increase caused by using the hardware accelerator.

HAsim [39] is a hybrid version of Asim which is internally used in Intel. Asim is a function-timing split simulator where the timing portion is build in a structural fashion. The functional and timing models of HAsim are closely coupled. The timing model explicitly requests that the functional model executes an instruction at the corresponding simulated time stamp. This organization results in a high degree of communication between these two partitions. In order to loose the timing constraints on the interface, HAsim applies a method named A-Port in the simulator design [40]. The A-Port scheme is similar to FIFO. Modules can be connected through A-Port, and the global synchronization is localized to enqueue and dequeue operations of FIFOs. This project has demonstrated its scaling capability of constructing many-core simulators on a single FPGA (up to 19 target cores). The overall simulation performance peaks at 3.2 MHz, but no performance comparison against an equivalent software-only simulator has been reported.

### 3.2.2 Hybrid Transplanting Simulator

The ProtoFlex system [27] adopts an alternative approach that combines software simulation with FPGA-accelerated instrumentation. This simulator currently only supports functional simulation, but uses a different partitioning strategy. This system implements a processor in hardware to simulate an instruction-set architecture. This instruction emulation engine is implemented on a FPGA, but it is not complete and some complex and rare operations and conditions (e.g. system I/O, FP operations, and certain traps) are handled in software by invoking either a host processor or FPGA PowerPC core with necessary state transfer upon request. Multiple processor contexts are supported to allow multiprocessor functional simulation. This simulator can achieve a simulation throughput as high as 62 MIPS, but only simulating instructions. ProtoFlex didn't provide a equivalent software simulator for comparison either.

## 3.2.3 Hybrid Structural Simulator

The Liberty project at Princeton has demonstrated the feasibility of a hybrid simulation approach based upon a structural partitioning strategy in [25]. This project uses the LSE framework to create a software-only simulator in a concurrent and structural form [41]. Later on, the processor core in the created chip multiprocessor simulator are replaced with the physical PowerPC cores on FPGAs. Both functionality and timing of the processor cores are simulated in hardware and the memory architecture is simulated in software. The FPGA PowerPC cores are wrapped with a communication interface; the interface transfers data with the software portion through a adapter module that calls the device drivers. The interface implements a polling scheme and makes no attempt to optimize the communication between software and hardware: the software requests the hardware to execute and polls for hardware completion. This simulator is parallelized at a coarse-granularity level through four physical PowerPC cores on the same FPGA. This hybrid design is constrained by the number and performance of available FPGA PowerPC cores. This hybrid simulator achieves up to 5.82 speedup, compared with the corresponding software-only simulator. The performance comparison between the hybrid simulator and the software simulator is not accurate. The hybrid simulator uses physical PowerPC cores, however, the baseline simulator is a simplified microprocessor model so that the achieved simulation speedup is much less than it would be with a detailed baseline simulator.

#### 3.2.4 Discussion

Several hybrid microarchitectural simulators have been introduced in different categories. It is impossible to compare their simulation speed with each other, because those simulators models different processors at different abstraction levels and they are organized and partitioned differently. Most of the hybrid simulator designs didn't provide a baseline software-only simulator to compare with so that we are not able to investigate the impact of the hardware acceleration and the interface overhead on the simulation performance. In addition, all the previous hybrid simulators are created manually, so it is very time-consuming to design and debug the hardware portion and the interface. The inefficient design process prohibits a widespread use of hybrid microarchitectural simulators for evaluating microprocessor candidates in both academia and industry.

The third category, hybrid structural microarchitectural simulator, is particularly interesting. It combines the benefits of structural modeling and hardware acceleration. The design flow starts with a software model created under a structural simulation framework, and portions of the software structural model are replaced with equivalent hardware components for acceleration. The performance loss of structural simulation can be recovered with the use of FPGAs. When the transformation from software structural models to hybrid simulators is automated, this category of hybrid simulators does have the potential to be easily created and efficiently executed.

# **Chapter 4**

# **SPRI: Simulator Partitioning Research Infrastructure**

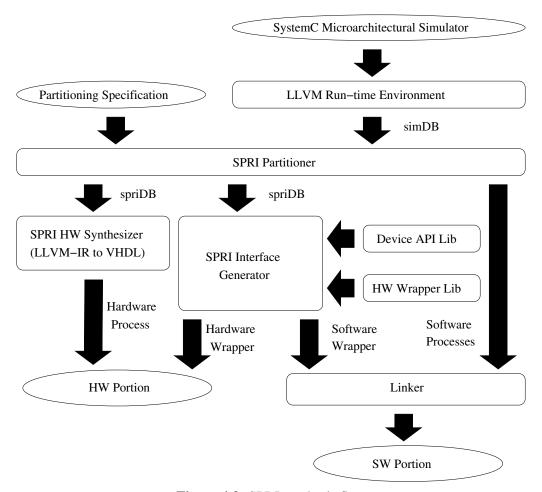

Hybrid structural microarchitectural simulators combine the benefits of structural modeling and hardware acceleration in a flexible fashion that architects are able to make trade-offs between hardware capacity, ease of implementation, and simulator performance. Unfortunately, it is very time-consuming to create a hybrid structural microarchitectural simulator by hand. Architects have to plan a software/hardware partitioning, design both the software and the hardware, and create a software/hardware interface. The manual design process become increasingly prohibitive, when target systems scale to many cores and higher system integration. To promote a widespread use of hybrid structural microarchitectural simulators, we have proposed to automate the design process through synthesis. This chapter introduces the synthesis flow for hybrid structural microarchitectural simulators by describing the SPRI infrastructure in which the contributed techniques have been implemented and integrated.

SPRI automatically synthesizes hybrid structural microarchitectural simulators from software structural microarchitectural models. The input models must have been developed under a structural simulation framework before being passed to SPRI. The output simulator consists of a software portion, a hardware portion, and a software/hardware interface. The executable binary of the software portion runs on the host processor; the hardware portion is downloaded to the FPGA after being synthesized to gates. The design efforts of architects are only dedicated to implementing the input structural microarchitectural models; no extra effort is needed to transform them to the equivalent hybrid simulators. SPRI allows users to guide the partitioning and the interface selection depending on how they organize their simulators. Given a software simulator as input to SPRI, a set of equivalent hybrid simulators can be rapidly generated with different selection of partitionings and interfaces.

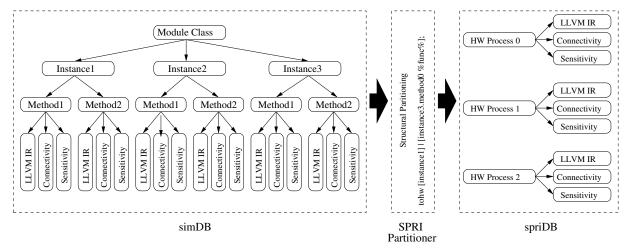

### 4.1 SPRI Input

SPRI has two inputs: SystemC microarchitectural models and partitioning specifications. The partitioning specifications guide SPRI to move portions of the input software simulators into hardware. The input simulator must have been developed and debugged; the users of SPRI must be responsible for its correctness and accuracy.

Where to partition a SystemC microarchitectural simulator is of great importance in constructing a hybrid structural simulator. The simulator partitioning determines what to synthesize and how to interface in later processing. Thus, the hardware cost and the hybrid-simulation speed may vary depending on the chosen partitioning boundary. SPRI takes partitioning instructions from the users and finishes the partitioning of the input SystemC microarchitectural models automatically. This feature offers the users the flexibility to choose the partitioning boundary based on the hardware capacity and the input simulator's organization. Because there is no one partitioning that works effectively for every simulator, the users are in charge of exploring partitioning options and selecting the one that leads to the best hybrid simulator.

### 4.1.1 SystemC

There are several structural simulation frameworks (e.g. Liberty, Unisim, and SystemC) that can be used to develop microarchitectural models in software. SystemC microarchitectural models are chosen as input to SPRI particularly, because SystemC has several important features.

- SystemC is an additional library attached to C++, including a set of C++ classes and macros. This feature enables architects to simulate concurrent hardware processes using plain C++ syntax which they are familiar and comfortable to work with.

- SystemC not only offers a rich amount of structural and concurrent constructs (e.g. process, signal, event) to express model hierarchy and timing, but also has non-structural features (e.g shared/global variable, cross-object call) and object polymorphism inherited from C++ to enhance modeling productivity and permit high-level code reuse.

- SystemC allows modeling at different abstraction levels (e.g. behavior level, RTL) or with a mix of several. This is important for microarchitectural modeling because detailed models

may be needed for a portion of a microarchtectural model that architects want to thoroughly evaluate and less details may be described for the other portion in order to reduce modeling complexity.

• Sophisticated SystemC simulation environments and debugging tools (e.g. CoCentric from Synopsys, ModelSim from Mentor Graphics, OSCI SystemC Simulator) have been developed for years to facilitate software modeling.