Brigham Young University BYU ScholarsArchive

Theses and Dissertations

2010-11-17

# An Onboard Vision System for Unmanned Aerial Vehicle Guidance

Barrett Bruce Edwards Brigham Young University - Provo

Follow this and additional works at: https://scholarsarchive.byu.edu/etd

Part of the Electrical and Computer Engineering Commons

## **BYU ScholarsArchive Citation**

Edwards, Barrett Bruce, "An Onboard Vision System for Unmanned Aerial Vehicle Guidance" (2010). *Theses and Dissertations*. 2381. https://scholarsarchive.byu.edu/etd/2381

This Thesis is brought to you for free and open access by BYU ScholarsArchive. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of BYU ScholarsArchive. For more information, please contact scholarsarchive@byu.edu, ellen\_amatangelo@byu.edu.

An Onboard Vision System for Unmanned Aerial Vehicle Guidance

Barrett B. Edwards

A thesis submitted to the faculty of Brigham Young University in partial fulfillment of the requirements for the degree of

Master of Science

James K. Archibald, Chair Dah-Jye Lee Doran K. Wilde

Department of Electrical and Computer Engineering Brigham Young University December 2010

> Copyright © 2010 Barrett B. Edwards All Rights Reserved

#### ABSTRACT

#### An Onboard Vision System for Unmanned Aerial Vehicle Guidance

#### Barrett B. Edwards

#### Department of Electrical and Computer Engineering

#### Master of Science

The viability of small Unmanned Aerial Vehicles (UAVs) as a stable platform for specific application use has been significantly advanced in recent years. Initial focus of lightweight UAV development was to create a craft capable of stable and controllable flight. This is largely a solved problem. Currently, the field has progressed to the point that unmanned aircraft can be carried in a backpack, launched by hand, weigh only a few pounds and be capable of navigating through unrestricted airspace.

The most basic use of a UAV is to visually observe the environment and use that information to influence decision making. Previous attempts at using visual information to control a small UAV used an off-board approach where the video stream from an onboard camera was transmitted down to a ground station for processing and decision making. These attempts achieved limited results as the two-way transmission time introduced unacceptable amounts of latency into time-sensitive control algorithms. Onboard image processing offers a low-latency solution that will avoid the negative effects of two-way communication to a ground station.

The first part of this thesis will show that onboard visual processing is capable of meeting the real-time control demands of an autonomous vehicle, which will also include the evaluation of potential onboard computing platforms. FPGA-based image processing will be shown to be the ideal technology for lightweight unmanned aircraft. The second part of this thesis will focus on the exact onboard vision system implementation for two proof-of-concept applications. The first application describes the use of machine vision algorithms to locate and track a target landing site for a UAV. GPS guidance was insufficient for this task. A vision system was utilized to localize the target site during approach and provide course correction updates to the UAV. The second application describes a feature detection and tracking sub-system that can be used in higher level application algorithms.

Keywords: thesis, BYU, UAV, Robotic Vision Lab, MAGICC Lab, Helios, FPGA, image processing, vision guided landing, feature tracking

#### ACKNOWLEDGMENTS

I first would like to express sincere appreciation to Wade Fife. Wade was an infinite source of knowledge to my endless stream of questions. He also created the Helios Board, which turned out to be the focus of my graduate education. Much appreciation also goes to Blake Barber, who was my teammate on the UAV vision-guided landing project. Nate Knoebel deserves recognition for acting as a pilot for numerous flight tests. I also must give great appreciation to James Archibald. He always ensured that there was funding for my projects, which meant a lot to me. And for being so patient in waiting for this thesis. Last, but certainly not the least, I must express appreciation to my wife Ashley, for never allowing me to give up.

# Table of Contents

| Li | List of Tables |                       |                                |  |      |  |

|----|----------------|-----------------------|--------------------------------|--|------|--|

| Li | st of          | Figure                | es                             |  | xiii |  |

| 1  | Intr           | roduction             |                                |  |      |  |

|    | 1.1            | Motiva                | ation                          |  | 1    |  |

|    |                | 1.1.1                 | Smart Sensor                   |  | 2    |  |

|    |                | 1.1.2                 | Delivery Vehicle               |  | 2    |  |

|    | 1.2            | Proble                | em Description                 |  | 3    |  |

|    |                | 1.2.1                 | Off-Loading                    |  | 4    |  |

|    |                | 1.2.2                 | Latency                        |  | 4    |  |

|    | 1.3            | Objec                 | tives and Applications         |  | 5    |  |

|    | 1.4            | Outlin                | 1e                             |  | 7    |  |

| 2  | Bac            | kgroui                | nd                             |  | 9    |  |

| 3  | Plat           | form                  | Selection                      |  | 13   |  |

|    | 3.1            | System                | n Requirements                 |  | 13   |  |

|    | 3.2            | 2 Platform Evaluation |                                |  | 15   |  |

|    |                | 3.2.1                 | Micro-controller               |  | 15   |  |

|    |                | 3.2.2                 | Digital Signal Processor (DSP) |  | 16   |  |

|    |                | 3.2.3                 | Graphics Processing Unit (GPU) |  | 16   |  |

|          |     | 3.2.4    | Field Programmable Gate Array (FPGA)           | 17 |

|----------|-----|----------|------------------------------------------------|----|

|          |     | 3.2.5    | Application Specific Integrated Circuit (ASIC) | 18 |

|          | 3.3 | Chose    | n Solution                                     | 19 |

| 4        | Arc | hitectı  | ıre                                            | 23 |

|          | 4.1 | Proces   | ss Flow                                        | 23 |

|          | 4.2 | Camer    | ra Basics                                      | 24 |

|          |     | 4.2.1    | Progressive Scan Shutter                       | 25 |

|          |     | 4.2.2    | Interlaced Shutter                             | 26 |

|          |     | 4.2.3    | Global Shutter                                 | 27 |

|          |     | 4.2.4    | Image Sensor Design                            | 27 |

|          |     | 4.2.5    | Data Formats                                   | 29 |

|          | 4.3 | Techn    | iques                                          | 31 |

|          | 4.4 | Inline   |                                                | 31 |

|          |     | 4.4.1    | Example: Threshold Counter                     | 32 |

|          | 4.5 | Offline  | 9                                              | 34 |

|          |     | 4.5.1    | Example: Image Normalization                   | 35 |

|          | 4.6 | Cache    | d Inline                                       | 37 |

|          |     | 4.6.1    | Example: Bayer Pattern Demosaicing             | 39 |

| <b>5</b> | App | olicatio | on: Vision-Guided Landing                      | 45 |

|          | 5.1 | Introd   | uction                                         | 45 |

|          | 5.2 | System   | n Design                                       | 46 |

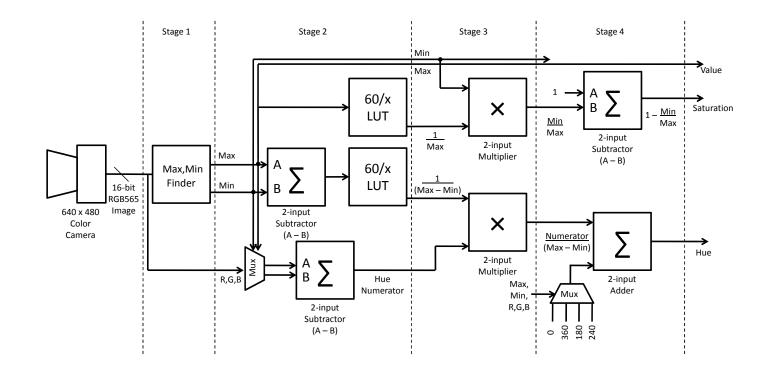

|          |     | 5.2.1    | Color Space Conversion                         | 48 |

|          |     | 5.2.2    | Color Segmentation                             | 50 |

|          |     | 5.2.3    | Connected Components                           | 51 |

|    |       | 5.2.4 Tracking and Filtering       | 52 |

|----|-------|------------------------------------|----|

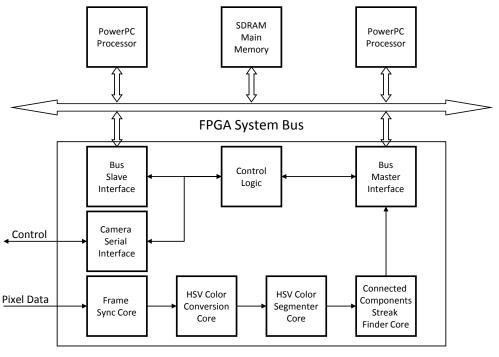

|    | 5.3   | FPGA System Architecture           | 53 |

|    | 5.4   | Results                            | 54 |

|    |       | 5.4.1 Static Landing Site          | 55 |

|    |       | 5.4.2 Moving Landing Site          | 58 |

| 6  | App   | olication: Feature Tracking        | 63 |

|    | 6.1   | Introduction                       | 63 |

|    | 6.2   | System Design                      | 64 |

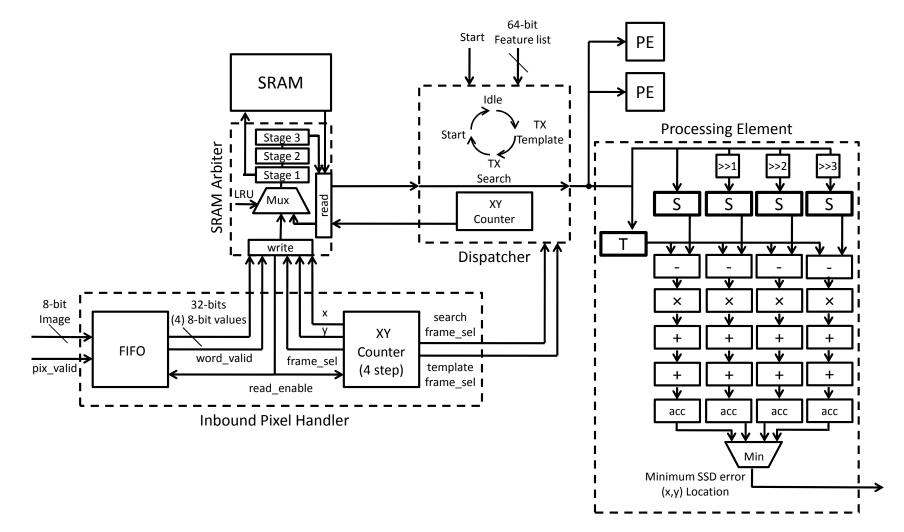

|    | 6.3   | System Architecture                | 66 |

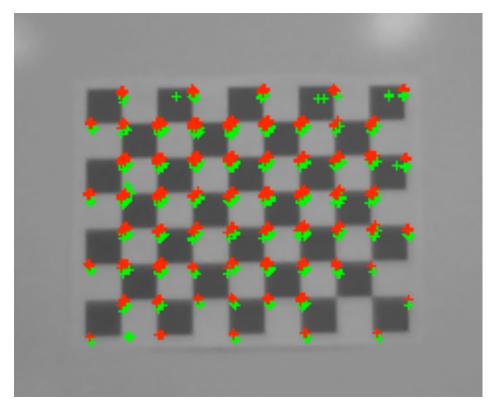

|    |       | 6.3.1 Harris Feature Detector Core | 67 |

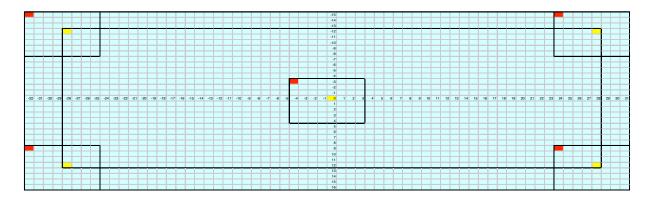

|    |       | 6.3.2 Feature Correlation Core     | 70 |

|    | 6.4   | Results                            | 78 |

| 7  | Con   | clusion                            | 83 |

|    | 7.1   | Summary                            | 83 |

|    | 7.2   | Contributions                      | 84 |

|    |       | 7.2.1 Hardware                     | 84 |

|    |       | 7.2.2 Embedded Software Framework  | 87 |

|    |       | 7.2.3 Software Algorithms          | 88 |

|    | 7.3   | Future Work                        | 89 |

| Bi | bliog | graphy                             | 91 |

# List of Tables

| 6.1 | Four possible search area configurations              | 76 |

|-----|-------------------------------------------------------|----|

| 6.2 | FPGA resource consumption of major system components  | 79 |

| 6.3 | Performance of implemented components                 | 80 |

| 6.4 | Maximum number of correlated features per time period | 80 |

# List of Figures

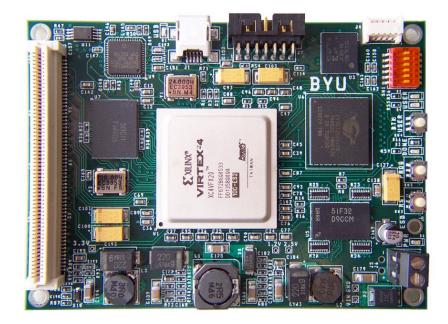

| 3.1  | Helios robotic vision platform                                                                 | 20 |

|------|------------------------------------------------------------------------------------------------|----|

| 3.2  | Micro air vehicle test platform                                                                | 21 |

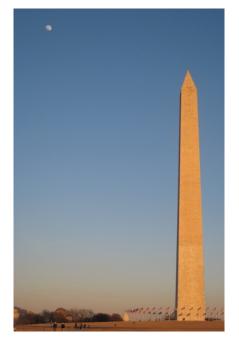

| 4.1  | Washington monument with no frame skew. Camera was stationary during capture                   | 26 |

| 4.2  | Washington monument with frame skew. Camera panned to the right during capture.                | 26 |

| 4.3  | Bayer pattern                                                                                  | 28 |

| 4.4  | Bayer pattern profile                                                                          | 28 |

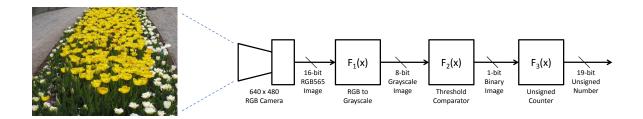

| 4.5  | Inline thresholded counter                                                                     | 32 |

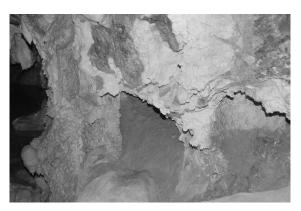

| 4.6  | Original cave image. Left portion is too dark to perceive content                              | 35 |

| 4.7  | Normalized cave image. Left portion is now plainly visible                                     | 35 |

| 4.8  | Histogram of original image. Pixel brightness is skewed and not evenly spread across spectrum. | 36 |

| 4.9  | Histogram of normalized image. Pixel brightness is evenly spread across the spectrum.          | 36 |

| 4.10 | Normalization circuit                                                                          | 38 |

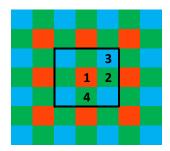

| 4.11 | Bayer grid                                                                                     | 40 |

| 4.12 | Bayer demosaicing logic circuit                                                                | 42 |

| 5.1  | VGL 4 step process                                                                             | 46 |

| 5.2  | RGB to HSV color conversion core                                                               | 49 |

| 5.3  | FPGA image processing core                                                                                                    | 53 |

|------|-------------------------------------------------------------------------------------------------------------------------------|----|

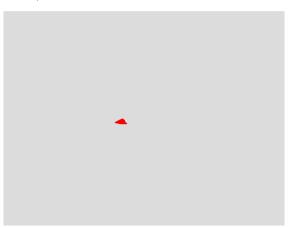

| 5.4  | Unprocessed RGB image captured during flight ( $\approx 100 \text{ m to target}$ )                                            | 56 |

| 5.5  | Color segmented image captured during flight ( $\approx 100 \text{ m to target}$ )                                            | 56 |

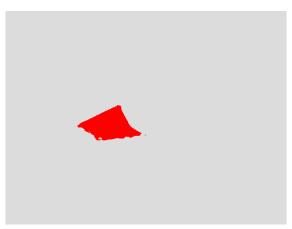

| 5.6  | Unprocessed RGB image captured during flight ( $\approx 50$ m to target)                                                      | 56 |

| 5.7  | Color segmented image captured during flight ( $\approx 50$ m to target)                                                      | 56 |

| 5.8  | Unprocessed RGB image captured during flight ( $\approx 15$ m to target)                                                      | 56 |

| 5.9  | Color segmented image captured during flight ( $\approx$ 15 m to target)                                                      | 56 |

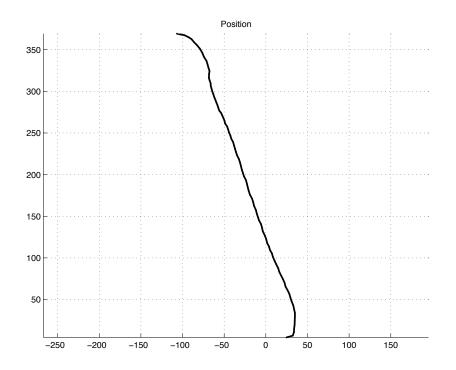

| 5.10 | Flight data plot of MAV flight path GPS location for static landing site scenario. Target landing site is at location (25,0). | 57 |

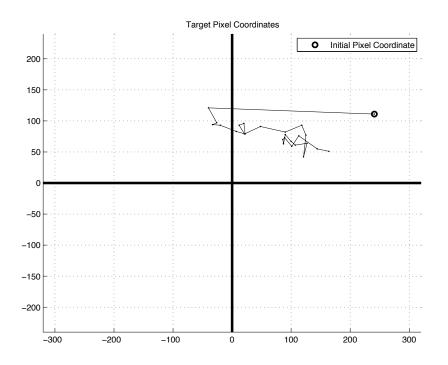

| 5.11 | Flight data plot of identified target landing site in incoming video images                                                   | 58 |

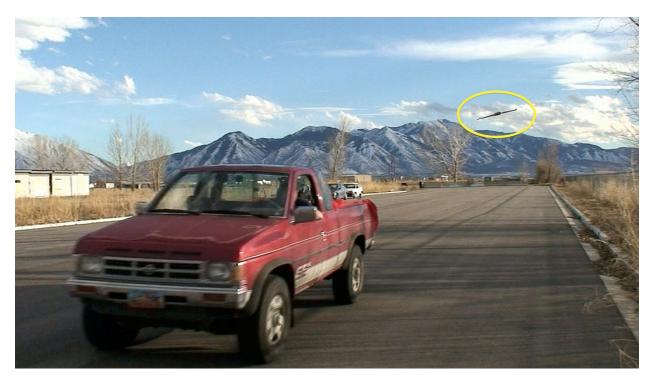

| 5.12 | MAV approaching target landing site                                                                                           | 59 |

| 5.13 | MAV landing at target landing site                                                                                            | 59 |

| 5.14 | MAV approaching moving vehicle landing site                                                                                   | 61 |

| 5.15 | MAV landing on moving vehicle                                                                                                 | 61 |

| 6.1  | Example of x and y image gradients                                                                                            | 65 |

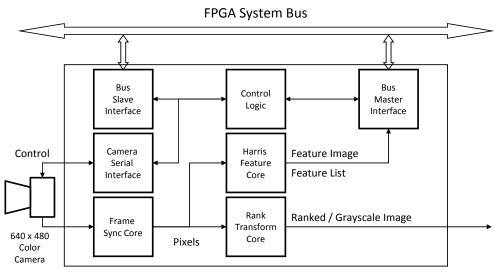

| 6.2  | FPGA camera core                                                                                                              | 67 |

| 6.3  | Harris feature detector core                                                                                                  | 68 |

| 6.4  | Harris source image                                                                                                           | 69 |

| 6.5  | Harris feature image                                                                                                          | 69 |

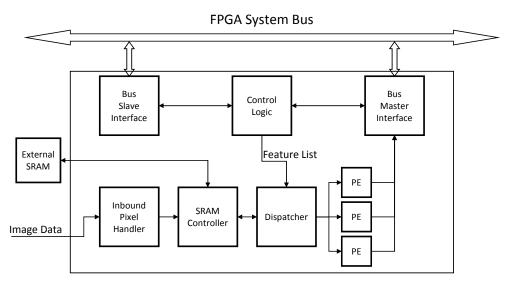

| 6.6  | FPGA correlation core                                                                                                         | 70 |

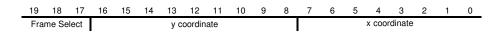

| 6.7  | Partitioned SRAM address space                                                                                                | 72 |

| 6.8  | Correlator core detail                                                                                                        | 73 |

| 6.9  | Template matching search area                                                                                                 | 74 |

## Chapter 1

## Introduction

The dawn of Unmanned Aerial Vehicles (UAV) has come and gone. It is no longer a field with limited application or attention. Without the hampering effects of insufficient technology, mobile vehicles have evolved into advanced sensory platforms. As expendable devices they can be deployed in circumstances unsafe for human life or to unreachable locations. As continual rapid development continues to increase the services that they provide, UAVs will further solidify their permanent place as specialized tools.

However, the technology is still not yet mature. Mobile computing, due to its inherent restrictions, necessitates custom embedded systems with niche strengths and broad weaknesses. Development on such platforms is slow and cumbersome. Each and every new application requires focused tailoring to meet specific system requirements. This specialization comes at a cost. Due to the limited nature of the mobile vehicle computing environment, any tuning of system features or capabilities toward a certain application will limit applicability in others. There will always be more to develop as new applications arise requiring additional functionality. Therefore each new contribution to the field must attempt to not just enable a single use application but to be applicable to the field in general.

#### 1.1 Motivation

The most basic UAV is one that can autonomously navigate unrestricted airspace. This requirement may sound simple, but it has only been achieved through a number of significant developments. It requires a capable airframe, a source of thrust, a global positioning system, accelerometers to determine aircraft attitude, pressure sensors to determine airspeed and altitude, and most of all it requires a tuned autopilot control system. With this component set, this basic UAV can takeoff and fly user controllable waypoints. The limitation of this basic UAV is that it does not do anything of value. A UAV is a tool that is utilized to accomplish some specific objective, and flying predefined or dynamic waypoints does not provide value. Above and beyond basic aerial navigation ability, a UAV is meant to fulfill two primary functions. First, a UAV can be used to extend the sensory perception of the user by observing the environment and then relaying back specific information. Second, a UAV is a mobile platform that can act in place of the user over a great distance.

#### 1.1.1 Smart Sensor

The primary benefit that a UAV can provide to the user in terms of sensory perception is sight. As remotely controlled aircraft, UAVs can provide a valuable high-altitude vantage point to the user. This may be utilized to provide an eye-in-the-sky view over an area too dangerous or out of reach for human access. Examples of such use would include forest fire perimeter tracking or search and rescue operations. Regardless of the application, sight extension is clearly a valuable service that a UAV can provide.

The quality of such a service can range depending on the technological capabilities of the craft. A simple video camera and radio transmitter can be added to the UAV, which would provide a video feed to the user who could use what was conveyed in the video in decision making. While this may be sufficient for some simple applications, it diminishes the role of the UAV from an autonomous craft to that of simply a remote control flying camera as it cannot act independently from the user. A greater value could be provided if the UAV was utilized as a Smart Sensor, which would require the UAV to have the ability to capture, process, and make decisive judgements with the visual information a camera could provide. Only once a UAV can utilize visual information for decision making without the need for user interaction will it be able to be used to autonomously accomplish any high-level objective.

### 1.1.2 Delivery Vehicle

In addition to use as a mobile sensory device, a UAV can be used to extend the reach of the user as a delivery vehicle. The size of deliverable payload would depend on the size and load bearing capabilities of the aircraft. Similar to the reasoning behind the value of a remote sensor, a UAV can deliver a payload to areas unsafe or physically remote from the user. Also as a mechanical vehicle, the UAV can be considered an expendable unit, which may be required in certain payload delivery events.

A remote sensor can only respond to obtained information by controlling the flight path of the aircraft and relaying that information back to the user. A higher ability is for the UAV to act upon information it collects and externally influence the environment around it. An example of such ability would be to deliver food or a radio to a lost or stranded person in a search and rescue operation. This goes over and above just locating the person by extending the reach of the user to the remote location faster than the user could otherwise travel there.

In summary the core service that a UAV must provide to be of any value is to simply sense the surrounding environment. However, to be of greater value it must also be capable of acting upon that perception. What is perceived, and what actions are taken based on observations, will be dependent upon the application. Regardless of what that application is, a UAV will need either one or both of these two capabilities to perform it.

#### 1.2 **Problem Description**

There is a major obstacle to the general adoption of UAVs. As defined, a smart sensor is one that can perceive and act independently from the user to achieve some highlevel objective. This classification requires the UAV to possess sufficient computing power to fulfill its intended purpose. But smart sensors also have to be of physically limited dimensions and comprised of inexpensive components to be considered cost effective.

A large UAV can support powerful but bulky processing equipment, fly farther without refueling, and in general provide greater services to the user. But a large UAV is limited in applicability as it may be physically too large for a person to carry or launch by hand. A small UAV, or Micro Aerial Vehicle (MAV), can provide a light, easily transportable platform. But smaller aircraft have limited payload capacity for sensory processing equipment, which reduces their application scope. This is the tradeoff that constrains UAV development: physical size versus processing ability. The challenge in UAV development is not to build the larger, flying supercomputer. Achievements in this area are limited only by the amount of fiscal resources that can be thrown at the problem. Rather, the greater challenge is to develop a tool that performs the desired function in the smallest form factor possible. Only with this goal in mind will UAVs be used to their capabilities as smart sensors.

#### 1.2.1 Off-Loading

One major obstacle with small UAV development is the limited amount of computing power that can be contained onboard the aircraft. One solution to this obstacle is to avoid it altogether by off-loading sensory processing to a ground-based computing station. An example implementation of this would be to equip a UAV with a video camera and transmitter and pair that with a laptop and video receiver on the ground. For some applications, this approach would be sufficient as the user may be indifferent to where the sensor data is processed. This approach limits the required onboard devices to sensory and transmission equipment, which may reduce the total physical size of the aircraft.

However, there are limitations imposed by off-loading that may render the aircraft to be insufficient in its ability to achieve the intended behavior. Ground-based processing requires constant radio contact to and from the remote vehicle, possibly requiring a near line of sight transmission path, which may not be realistic for every application. Transmission of raw sensor data would also by definition require a higher bandwidth communication link, which may increase onboard transmission equipment or power consumption more than would be required if the raw data was processed onboard the aircraft. High volumes of raw data transferred over a radio link will be subject to transmission noise, which may complicate ground-based processing that must account for transmission-induced noise in the data. But one of the most significant impacts of off-loading the raw sensor data processing to a groundbased computing station is the introduction of latency.

#### 1.2.2 Latency

The basic system process flow for an autonomous vehicle is to gather sensor data, whether it be GPS location, airspeed, or visual imagery, process that data into a decisive action, and then implement that action. This cycle is not casually periodic but rather must be completed multiple if not dozens of times every second for the aircraft to maintain vehicle control. In fact, the frequency of this process loop directly influences aircraft stability. This cycle is known as a control loop, which can be extremely sensitive to the affects of latency.

When excessive latency is introduced into a control loop, the physical system may become unstable, progress into violent oscillations, and crash. If latency in the control loop is unavoidable, the vehicle cannot compensate by simply reacting slower to new sensory inputs. A muted response to new information will reduce the agility of the UAV as it cannot rapidly adjust to a changing environment. Therefore, physical systems such as autonomous aircraft that rely on sensory input for vehicle guidance and control must avoid significant sources of latency in their control loops.

The approach of off-loading sensory processing from the UAV is flawed in the fact that it introduces latency. Raw sensor data must be transmitted down to a ground station, processed, a course of action determined, and commands returned to the UAV over another wireless link. With the introduction of this transmission delay, the UAV may not be able to react quickly enough to newly obtained information, which may cause the UAV to fail to achieve its objective. If there is a question whether the UAV would be able to complete its intended objective, it would likely not be deployed in the first place. Consequently the field of vision-guided, autonomous aircraft is lacking in application breadth due to excessive reaction time to newly acquired information.

#### **1.3** Objectives and Applications

It is the objective of this thesis to present a vision system capable of being mounted onboard a small UAV that will enable it to acquire, process, and react to visual sensory data without the need of a ground-based computing station. Central to the completion of this objective is to review current approaches to onboard image processing and to select an ideal computing platform suited for small UAV applications. To demonstrate the effectiveness of the chosen approach, the design methodology, implementation, and successful results of using the chosen approach will be shown in an example UAV application that requires quick visual processing and reaction time. Two applications were chosen for this demonstration. The primary application is the automated landing of a UAV at a stationary or non-stationary target site. This application was successfully completed and results are included. The secondary application is an investigation into a feature tracking system that is intended to be used as a sub-component for an obstacle avoidance system. Since there are major components of an obstacle avoidance system, such as collision detection algorithms and aerial avoidance maneuvers, which are outside the scope of low-power, embedded image processing, only the image feature tracking sub-component required to support an obstacle avoidance system is presented.

Targeted landing was selected as an example application primarily due to its absolute intolerance of latency and the inadequacy of existing localization technology in succeeding at the task. The basic premise of targeting landing is that a UAV in flight will eventually need to return to earth to refuel or to reach some intended location, which will require the UAV to land at a desired point. While the UAV is in a controlled descent toward the landing location, it must make increasingly rapid course corrections to its flight path to successfully arrive at the intended location. In the case of a moving target landing site, the UAV must continuously detect any change in the landing location and then adapt its flight path accordingly.

Existing efforts in this application area that utilize GPS tracking or off-loaded image processing have proved insufficient. The measured GPS location of the traveling aircraft or the landing site may not be known with sufficient accuracy due to limited sensor technology, which may prevent the aircraft from successfully arriving at the target site. If an onboard image sensor is used to acquire images and transmit them to a ground-based processing station that can analyze the environment and provide course corrections, the latency of the transmission time to and from the ground station may be too excessive to meet the realtime control needs of the increasingly quick adjustments that must be made as the aircraft approaches its target. This application requires a quick vision-based course correction system to enable successful landing.

This thesis will present a vision system that is capable of overcoming the limitations of GPS-based guidance and off-loaded image processing. The approach presented is to use an onboard camera and perform the image processing onboard the aircraft. This approach enables additional sensory perception beyond the limitations of noisy GPS positioners without the added transmission latency of off-board processing.

The feature tracking system application was additionally selected primarily due to its vast applicability as there are a wide number of uses of such a tracking system based on passive video input. Therefore it was included in pursuit of presenting a more complete list of fundamental image processing algorithms that can be used in a variety of applications.

## 1.4 Outline

This thesis is organized as follows. Chapter 2 describes prior work in the area of targeted landing and image feature tracking. Chapter 3 will provide an evaluation of computing platforms based on their ability to meet the requirements of the application. The system requirements to achieve the chosen applications will be defined and a platform will be selected that meets these requirements. Chapter 4 will discuss image processing methods and architecture implementation techniques on the chosen platform. Chapters 5 and 6 will discuss the exact implementation details of the computing platform that was used to achieve successful results. The results of each application will be included in their respective chapters. Chapter 7 provides a summary of the work, contributions the author has made, and suggestions for future work.

# Chapter 2

## Background

The technical literature includes several examples of vision-based implementations of autonomous landing. For example, several authors discuss the use of image processing to guide the aerial descent of unmanned hovercraft (e.g., helicopters, quadrotors) onto a landing pad as in [1, 2, 3, 4, 5]. In these applications, vision algorithms are used to estimate the pose of the hovercraft in relation to the landing pad during descent. Adding vision algorithms to the control loop enables precision adjustments to the descent path to be made that provide compensation for GPS position estimation inaccuracies. The results demonstrate that visionassisted control algorithms are effective in providing the desired course error correction.

Results in [2] show that this approach can be made to work without a predefined and structured landing site marker. However, easily discernible visual target features allow image processing algorithms to be simplified and reduce required computations.

In [5] a landing site marker was used with black and white colored boxes of a fixed size. The onboard vision system found the corners of the boxes, from which the pose of the hovercraft was estimated. Black and white markings were chosen to minimize the effects of varying outdoor lighting conditions. For the vision-guided landing application of this work, a solid color target was used that can be distinguished using color segmentation.

Unlike a hovercraft, a fixed-wing MAV must approach the intended landing site on an angled glideslope with enough forward velocity to maintain flight. Thus, limited time is available for image processing algorithms, which establishes the need for real-time vision computations in this application.

During autonomous landing, neither the direction of approach nor the heading angle at impact are constrained, which implies the markings on the target landing site need not express any orientation information. Ideally, the landing area can be recognized regardless of approach angle. For this work, a single color cloth target was selected. The important visual information about the target can consequently be summarized by the center of mass (x, y) (in image pixel coordinates) and the size (in number of pixels) of the landmark in each image acquired from the onboard camera. Therefore, the objective of the onboard vision system is to determine the target center of mass (x, y) in each image captured by the onboard camera.

Vision systems for small, autonomous vehicles can be divided into two groups depending on whether computation takes place locally or remotely. Tradeoffs of onboard and off-board computation are discussed in [6]. Crucial to the success of this approach is the choice of onboard computation. While other vehicles have employed local vision processing (e.g., [7, 3, 5]), these were substantially larger rotorcraft. In [7] a PC-104 stack was used and in [5] a 233MHz Pentium embedded system running Linux was used. These embedded platforms were either too large or not powerful enough to serve as the onboard computation platform.

Both [8] and [5] emphasize that they use *off-the-shelf* hardware to perform onboard image processing. They emphasize this design decision to stress the ease of development at the cost of performance and platform size. This work departs from this design goal, seeking instead the most computationally powerful platform for vision-assisted flight control on a small UAV.

Since the early days of reconfigurable computing, Field Programmable Gate Arrays (FPGAs) have been an attractive technology for image processing [9]. The inherent parallelism in typical image processing algorithms and the capability of FPGAs to harness that parallelism through custom hardware make FPGAs an excellent computational match. A tremendous amount of research has explored the use of FPGAs for various vision systems, ranging from simple filtering, to stereo vision systems, to multi-target tracking (see for example [10, 11]).

Unfortunately, much of the vision research on FPGAs has relied on multiple FPGAs placed in large systems as in [12] that cannot fit in small vehicles. However, largely due to Moore's law, FPGA technology has made significant advances since its inception. In recent years FPGA technology has progressed to the point where sophisticated imaging systems can be implemented on a single FPGA (compare, for example, the 14 FPGAs used in [12] with the single FPGA used in [13] for stereo vision).

Although the performance benefit of FPGAs has been well established for some time, less well known is the relative size and power requirements of modern FPGA-based image processors compared to high-performance, general-purpose CPUs [14]. These characteristics make FPGAs ideal for this work with small autonomous vehicles (see [14, 15, 6, 16]).

Much of the literature has focused on implementing complete imaging systems on FPGAs. The purpose of this work is different in that it aims to deliver a sophisticated, general-purpose, image processing solution in a small, low-power package.

## Chapter 3

# **Platform Selection**

Established in Chapter 1 is the premise that UAVs require the comprehension of visual information to fulfill their intended purpose as mobile sensory or delivery devices. The practice of off-loading or remotely processing that visual data was explained to be insufficient at meeting the low-latency requirements of a sensor in the control loop of an autonomous vehicle. If the image data cannot be externally processed in a timely manner then it must be processed onboard the vehicle itself. For this to happen, a mobile computing platform capable of low-latency image processing must be incorporated into the control system of the aircraft.

The purpose of this chapter is to identify a computing platform suitable for onboard image processing. To accomplish this, the evaluation criteria for a mobile image processing platform will first be established in Section 3.1. Possible solutions will then be evaluated according to that criteria, exposing strengths and weaknesses of each particular architecture in Section 3.2. Finally a platform best suited for deployment onboard a small UAV will be selected in Section 3.3.

### 3.1 System Requirements

The system requirements of a mobile vehicle computing system can be broken down into four areas:

- 1. Physical size

- 2. Power consumption

- 3. Computational ability

- 4. Development environment

The physical constraints of the image processing platform are driven by the size of the aircraft. The target aircraft for this work is a small UAV that weighs about 5 pounds with a wingspan of about 5 feet. The computational device chosen for the image system must not add an undue burden to the aircraft that would hinder aerial maneuverability. Therefore the vision system must weigh around 1 pound or less. The exact weight down to the ounce is not important to specify as this is only to provide evaluation criteria for potential computing platforms.

The power constraints are also driven by the physical size of the aircraft. As indicated in Chapter 1, the motivation behind this work is to produce a mobile device that can reasonably fly for a few hours at a stretch. Battery power supplies will be limited in this application to what can be carried onboard the aircraft, which implies that the power consumption of the computing system will have an inverse affect on flight time. The more power required by the computing system the shorter the possible flight duration. As a craft that is capable of longer flight durations will be valued more than one that is only capable of shorter durations, a low power computing system should be utilized.

To empirically determine the maximum acceptable power consumption of an onboard computing system, a typical commercially available hobby aircraft battery will be considered. A common battery at the time of this writing is a 12 volt, lithium polymer battery that has a capacity rating of 4 amp-hours, which holds a maximum of about 48 watt-hours. To last a minimum of 3 hours, the image computing platform would therefore be required to consume less than 16 watts. If the specific application requires a longer flight duration, then the platform power consumption threshold would have to be reduced or the battery capacity increased.

The exact computational requirements for the image processing system will vary based on the application. But regardless of the application, image processing is generally computationally intensive. To provide an example, the requirements for the vision guided landing application will be considered. In Sections 5.2.1 to 5.2.3, the following estimates are provided as to the number of raw mathematical computations that are required for a  $640 \times 480$  image size. The HSV color space conversion would require an estimated 110 million calculations to convert every pixel from the RGB color space to HSV. The color space segmentation step would require about 65 million calculations to threshold every pixel. While these two steps are performed on every pixel and their exact number of calculations determined a priori, the connected components step cannot be accurately estimated as it depends on the content of the image.

In addition to the first three constraints that center on the runtime environment requirements, the chosen platform must also be well suited as a development platform. As indicated in Chapter 1, the field of vision-based guidance in aircraft is still a developing art. As such, any platform chosen must support a relatively quick development cycle for system designers to design, test, evaluate, and then improve their designs.

While these evaluation criteria will be the primary benchmark to compare possible platforms, some other criteria will also be weighed. For example, the architectures ability to perform computations in parallel, or how easily adaptable is it to new applications will also be considered.

#### 3.2 Platform Evaluation

At the time of this writing there are in general five possible classes of computational devices that could be utilized in an aerial vehicle. Each of these will be individually considered according to the criteria set forth in Section 3.1.

#### 3.2.1 Micro-controller

A micro-controller is commonly implemented as a complete self-contained embedded system. With RAM, PROM, watchdogs, and I/O all built into a single package, it can perform a variety of tasks without extra external equipment, which may reduce the physical size needed for an image processing system. This class of device is often used in small and simple applications, such as toys, automobile sub-systems, and microwave ovens to name only a few. Micro-controllers outsell computer CPUs by roughly a 10 : 1 ratio, so availability is abundant and cost is usually low. Power consumption is also low as predictable execution time is emphasized over raw performance.

The most significant drawback to micro-controllers is limited raw performance. An image processing application requires a significant number of mathematical computations and the current state of micro-controllers cannot provide that level of performance. There is also limited parallelism available as micro-controllers are primarily a single core architecture. Since a micro-controller is computationally limited, it must be ruled out as a potential computing platform for the target applications of this work.

#### 3.2.2 Digital Signal Processor (DSP)

A digital signal processor is basically a micro-controller with specialized computation engines that are optimized for Single Instruction Multiple Data (SIMD) instructions. Since image processing tasks often require the same computation to be performed on every pixel, SIMD instructions can provide a significant performance speed up over single-threaded CPU implementations. These arithmetic units typically excel at multiply-accumulate operations (MAC), which are useful for Fast Fourier Transforms (FFT), matrix operations, and convolutions. Some also utilize a Very Large Instruction Word (VLIW) approach to try and keep multiple arithmetic units busy at the same time.

While DSP architectures are excellent at data level parallelism, they fail to utilize task level parallelism. Each processing step must wait for a turn on the arithmetic units and then use them exclusively until completed. What this implies in image processing is that each mathematical step of the algorithm must be executed sequentially, and there is no ability to have an 'application' pipeline where data flows from one step of the algorithm to the next. Integration with other components required in a mobile image processing system also accentuates this issue. For example, incoming pixel data from a common digital image sensor runs at 54 MHz, which implies that a new pixel would arrive from the camera about every 20 ns, interrupt the DSP, which would then store the pixel in memory since there would be no direct DMA from the camera to main memory. While a DSP would likely have the computational ability for individual image processing tasks, the limited task-level parallelism would make a mobile image processing platform based on a DSP challenging.

## 3.2.3 Graphics Processing Unit (GPU)

Recently, GPU design has changed from a single direction pipeline to a more modular architecture that can be programmed for General Purpose GPU computing (GPGPU) through C programming extensions such as the Compute Unified Device Architecture (CUDA) from nVidia. These extensions allow non-graphics applications to utilize the processing power of GPUs for other uses. As a computation device, a GPU is simply a massive array of floating point arithmetic units fed by a wide memory bus. Since GPUs were originally designed to perform image processing algorithms, total device performance is equal to or better than all of the other available architectures. The programming model is also well defined and interfaced in C style commands. This only requires the user to alter single-threaded algorithms to match the parallel architecture of the GPU, which is likely easier than translating it into a completely new language such as VHDL.

The performance of a GPU implementation comes at a high cost, and that is power consumption. The massive number of floating point units draw staggering amounts of power that in some graphics cards reaches into the hundreds of watts. Power consumption this high also requires mechanical cooling devices to dissipate heat. The required power consumption alone limits a GPU-based image processing platform from practical deployment onboard a small UAV. One additional limitation of a GPU-based system is that a GPU cannot operate alone as it needs a regular CPU to issue commands. So any mobile implementation would require not only a power hungry GPU but an additional power consuming CPU just to issue and monitor commands.

#### 3.2.4 Field Programmable Gate Array (FPGA)

The primary strength of FPGAs is that they can be reconfigured to perform various tasks, which enables them to serve well in development environments. The main computational strength of an FPGA is parallel processing that is inherent to the architecture. Commonly, an embedded CPU core within the FPGA is used to run software algorithms, while the reconfigurable fabric is used for accelerator cores that perform specific functions. In image processing applications, individual process steps may not be completed on an FPGA as fast as a GPU or DSP could complete them, but multiple algorithm steps can be overlapped in time through task-level parallelism. Power consumption on FPGAs is not the lowest of the possible architectures, but it can be controlled by the complexity of the design and can fit within the 16 watt limit estimated in Section 3.1. An FPGA will not be as small as an ASIC implementation due to raw die size; however, similar to an ASIC an FPGA can implement internally some functionality that would otherwise require discrete external components, which helps limit the total physical size of the entire computing system (e.g., internal FPGA Block RAM (BRAM) could be used in place of an external SRAM).

The downside of FPGA development over pure software development is time. FPGA hardware has a different programming model and is generally viewed as more difficult to program, verify, and debug. The reconfigurable fabric in FPGAs is also generally clocked at a slower frequency than other architectures, which reduces the potential performance of any given single atomic computation such as a multiply or addition operation. Even though an FPGA-based computing platform is not the best at any individual selection criteria as stated in Section 3.1, it provides an acceptable level of performance in each area. Most importantly, there is no critical flaw that excludes FPGAs from use on a small UAV.

#### 3.2.5 Application Specific Integrated Circuit (ASIC)

An ASIC offers the best performance in the first three selection criteria. A custommade piece of silicon can, within reason, be designed to include almost any computational ability from fully functional embedded CPUs, to specialized computational units, to I/O modules, and customized interconnect. Performance of any implemented image processing algorithm can be precisely tailored to match exactly the real-time needs of the application. Power consumption will also be as low as any other solution here considered since the hardware included is custom tailored for the intended application. An ASIC will also be the smallest physical system as the entire system may be integrated onto a single component package.

The critical limitation with an ASIC design is cost. ASIC development requires extensive design and verification techniques to be performed that will add to development time. Once laid out, the hardware of the ASIC is also not adaptable beyond changing software code on any embedded CPUs. Even though it would rank the highest on the first three selection criteria, these limitations essentially eliminate the use of an ASIC as a development platform in the applications targeted in this work.

#### 3.3 Chosen Solution

Based on the selection criteria stated in Section 3.1 and the individual platform evaluations in Section 3.2, an FPGA-based platform was chosen as the platform for the target applications of this work. As stated in the platform evaluation, FPGA-based platforms are not the highest performing, lowest power, or smallest physically of the available options. However, FPGAs do not have a critical flaw that eliminates their use in light-weight aircraft and instead are a sufficient mix of the selection criteria.

The onboard vision system utilized in this work was the Helios robotic vision platform developed at Brigham Young University [14] which is shown in Figure 3.1. Even though all the use cases described in this work are for image processing applications, Helios is in fact a general purpose FPGA-based development platform. The main component of the Helios platform is a Xilinx Virtex-4 FX FPGA, which contains up to two 400MHz embedded PowerPC processors. This specific FPGA is ideal for embedded image processing as it provides both a CPU for standard C code execution and reconfigurable FPGA fabric for hardware-accelerated algorithm implementation.

Other additional peripheral components include a 32 MB SDRAM that serves as the main memory for the system, while a 4 MB SRAM is available to be used as a local memory cache for custom image processing tasks. A 16 MB flash memory is also included. A USB 2.0 port provides high-speed data transfer, including live video to a desktop computer during system development and debugging. A RS-232 serial port provides low-speed connectivity, which realistically is too slow for image transfers, but is perfectly satisfactory for debugging or for a command interface.

The Helios platform was designed with the intention to be as flexible as possible. Therefore the system design was constructed of a main board with all the primary high-speed devices, and interchangeable daughter cards that can be customized for any given application. A 120-pin expansion header is used to connect the Helios main board to specialized daughter boards. Daughter boards are essentially I/O boards with device-specific connectors for cameras, servos, communication devices, etc. As a computing platform, it serves as a rich development environment with a small physical footprint (2.5" x 3.5" at 37 grams) that is well suited for mobile image processing applications.

Figure 3.1: Helios robotic vision platform

This work was a joint effort between the Robotic Vision Lab and the Multiple Agent Intelligent Coordination and Control Lab (MAGICC Lab) at Brigham Young University. The author was responsible for the implementation of the vision system and Blake Barber from the MAGICC lab was responsible for adapting the flight control algorithms of the existing Kestrel autopilot. Those control algorithms will not be discussed here, but the aircraft that was used in these applications is shown in Figure 3.2. 'Ray' as this aircraft was called is an all electric mono-wing design constructed out of a styrofoam core that is wrapped in kevlar. The leading edge of the body was modified to provide a viewport that could house the Helios board and a fixed mounted camera.

With the computing architecture chosen as an FPGA-based platform, the next step in the process is to evaluate the given techniques that can be used for real time image processing.

Figure 3.2: Micro air vehicle test platform

# Chapter 4

# Architecture

All architectures have constraints. This is true no matter the computing platform being considered. Limitations of the system play a major role in the design and implementation of an application. They set the bounds of what the system designer can utilize to fulfill desired functionality. The constraints of the system also limit the methods and techniques available for the system implementation.

All architectures also have strengths. The unique abilities of different architectures are what distinguish one from the next. Some are highly parallel. Others are functionally specialized with high performance. Regardless of the platform, it will have distinct abilities that must be utilized in the methods and techniques used in the system implementation.

The purpose of this chapter is to identify and illustrate the methods and techniques available for real-time image processing on an FPGA-based computing platform. The outline of this chapter is as follows. Section 4.1 describes the basic refinement principle that image processing must accomplish. Section 4.2 reviews foundation level information that must be understood when designing a system that processes digital images such as shutter modes, sensor design, and image data formats. Section 4.3 provides an example-based description of the three techniques used to implement image processing algorithms on FPGAs, which are inline, offline, and cached inline.

## 4.1 Process Flow

Video images contain a near infinite amount of information available for interpretation, which also means that in raw form, video images are essentially useless. To be of any value, a system that processes video images must capture raw images, analyze them, and produce useful, actionable information. The vision system must be thought of as a process that refines large quantities of raw data and extracts specific information. The summarized data must therefore be physically less data, possibly even a single value, to be useful in decision making.

To demonstrate this process, a sample application will be considered. A common need in image processing is to find the location of an object in an image. The theoretical number of potential images can be determined by computing the *variant space* of the incoming image. An 8-bit color scale for each of the R, G and B channels would produce a 24-bit color space for each pixel in the image. A standard definition size image of  $640 \times 480$  contains 307,200 pixels, which results in a variant space of

$$(2^{24})^{(307,200)}$$

The result of the image processing required for this work is a single numeric pair (x, y) of 10-bit values, which has a variant space of

$$2^{(10\times2)}$$

.

The resulting reduction in data is effectively infinite.

However, a vision system cannot summarize all information. With a near infinite input vector space the potential number of output vectors are also infinite. The system must focus on specific things to look for and specific results to summarize. And to be applicable to a real-time environment, the process flow must be continually run on a never-ending stream of images.

## 4.2 Camera Basics

Before discussing the details of image processing techniques, the characteristics of the data input need to be understood. Regardless of the silicon or optical technology used, all cameras function essentially the same. They expose a 2D silicon array of transistors to light, measure the amount of light received in a given period of time, convert that measurement into a numerical value for each pixel, and transmit the pixel values out over a data bus. Due to practical considerations, there is not a data port for each pixel off of the image sensor.

Therefore, pixel data does not come out all at once, but rather it comes out slowly over a serial bus.

Image sensors come with a few different shutter modes. The most common are: progressive, interlaced, and global. Progressive cameras expose one row of pixels of the image sensor at a time. Interlaced sensors expose all the odd or even rows at the same time, and global shutter cameras expose the entire frame at once. The primary difference in the construction of these sensors is the amount of RAM built into the sensor.

## 4.2.1 Progressive Scan Shutter

Progressive scan image sensors are the most basic of the three types. They have only a single row buffer built in, which implies that only a single row of pixels can be 'captured' at a given time. Progressive scan sensors expose each row in the array for the same amount of time, but begin the exposure of each row at different times, with the separation in the exposure about equal to the amount of time required to clock out the prior row.

The most significant aspect of progressive scan image sensors to machine vision applications is the impact of frame skew. Since the image sensor captures each row at separate times, there is a time delta between the capture of the first row and the last row of the image. If the scene is near static, implying there is little horizontal, vertical, or rotational motion in the scene, then the impact of frame skew will be negligible. If there is motion in the scene, any subject items in the image will be 'skewed.'

An example of frame skew can be found in Figures 4.1 and 4.2. Figure 4.1 shows a picture of the Washington monument without any frame skew, which implies that it was captured while the camera was stationary. Figure 4.2 depicts what would be recorded if the camera panned to the right during capture. It can be seen that the monument 'leans' to the right, because the monument moved to the left in the camera's field of view as the camera panned to the right. The upper rows of the image represent what was in the field of view of the camera when the frame capture began, and the bottom rows represent what was in the field of view when the frame capture ended. While the skew in these figures is exaggerated for demonstration purposes, the impact of frame skew on image processing algorithms must be considered when evaluating a progressive scan camera for any mobile vehicle application.

Figure 4.1: Washington monument with no frame skew. Camera was stationary during capture.

Figure 4.2: Washington monument with frame skew. Camera panned to the right during capture.

## 4.2.2 Interlaced Shutter

Interlaced cameras were developed with the intent to convey motion more fluidly to the human eye. This was achieved by doubling the frame rate but only capturing and transmitting half of the total image each cycle. The single image is split into fields of the odd and even rows of the image. During a single field exposure, all of the odd or even rows in the image are exposed and captured at the same time. The two separate fields are then assembled into a single image. And due to the fact that the single composite image is comprised of two exposures at separate times, the motion is blurred and is perceived by the human eye as more fluid.

While an interlaced image conveys motion more fluidly to the human eye, it, however, is problematic for machine vision applications. For example, if there is a moving object in an image, it will be centered at one location in the odd rows of the image, and a different location in the even rows of the image. The odd and even fields are essentially two separate images, each of which has a vertical resolution of 1/2 of the total composite image with a 1 pixel vertical shift between the two. Therefore, when running some image processing algorithms, the two would have to be processed separately, or one of the two fields would have to be ignored. In either case, the result is a source image that has a 50% reduction in vertical resolution, which skews the pixel aspect ratio from square to rectangular.

## 4.2.3 Global Shutter

Global shutter cameras expose all pixels in the image at the same time. Every cycle, the camera resets all of the photon sensing transistors and starts capturing light. After the exposure time has elapsed, the level of each pixel is captured and converted to a digital value. Then the image is 'read out' pixel-by-pixel, and row-by-row, just like progressive and interlaced cameras.

These are less common in consumer applications as the video is perceived to be 'jerky' when compared to a progressive or an interlaced camera. But in machine vision applications, a global shutter camera is the ideal camera type. With the entire image exposed at the same moment there is no frame skew, as demonstrated in Figures 4.1 and 4.2. There is also no reduction of vertical resolution found with interlaced images. Each image is a representative sample 'snapshot' of the scene, which can be considered to be exactly what was seen at a single moment in time.

But a global shutter does not eliminate all the affects of motion. Since the entire image is exposed simultaneously, any motion in the scene will be 'blurred' in the captured image. This blurring effect is accentuated by faster movement of objects in the scene, or by longer exposure times. Therefore, to minimize the blurring effect of a moving scene, the global camera should be operated at the highest possible frame rate (i.e., shortest exposure time) that the processing system can sustain.

#### 4.2.4 Image Sensor Design

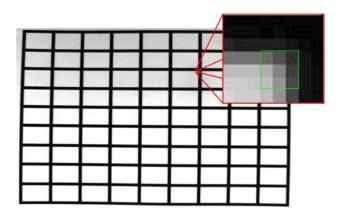

Color values in images are typically represented as the combination of the brightness of the red, green, and blue channels at that point in the image. Therefore a color pixel is defined by the data set (R, G, B). However, image sensors do not capture all three of the R, G, and B channels at each pixel. In fact image sensors are capable of capturing only one color channel at each pixel location. An image sensor is an array of color filers placed on top of transistors similar to the graphic shown in Figure 4.3. Each block in Figure 4.3 represents a single transistor, which will only measure the amount of light received through the color filter as shown in Figure 4.4. There exist several variants of this pattern, which utilize filters of different colors or arrangements of the filters on the transistor array, but the 'RGBG' Bayer pattern shown in Figure 4.3 is the most basic and will suffice for this discussion. Regardless of the array pattern used, the consequences are still the same: the image sensor will not produce all three color channels for each pixel. Bayer pattern images do not have distinct (R, G, B) values for each pixel and must be converted into an image that has an (R, G, B) value set for each pixel. This process is called 'demosaicing' and will be discussed in an example later in this chapter.

Figure 4.3: Bayer pattern

Figure 4.4: Bayer pattern profile

## 4.2.5 Data Formats

There exist many data formats that can be used to represent an image. However, in the field of mobile image processing applications only a few of the possible image data formats are produced by mobile image sensors. Each has advantages for specific applications and these will briefly be discussed here. The image formats that are commonly produced by small image sensors are:

- 1. Grayscale

- 2. Bayer

- 3. RGB 888

- 4. RGB 565

- 5. YUV

## Grayscale

Grayscale images, which are often mistakenly called 'Black and White' images, are the simplest image format. The pixel values in the image represent the brightness or the total amount of light received at that point. Common value ranges for grayscale images are 8-bit and 10-bit, which allow a maximum of 256 and 1,024 different brightness levels respectively. Grayscale is often useful for algorithms that compare two images together or search for image features such as the Harris feature detector algorithm which will be discussed in Chapter 6.

## Bayer

Bayer pattern color images as discussed previously are essentially useless in their original form. They only exist as an intermediate format. Even though most cameras can output the captured image in this format, it must be converted into another format before any image processing can be performed.

#### **RGB 888**

The RGB 888 format implies that each pixel in the image is defined by the value set (R, G, B), and each of those channels are 8-bit values. This is a very common image

representation. For example, Bitmap images (with a .BMP extension), use this format. Since the RGB 888 format is comprised of three 8-bit channels the total color space that is representable by each pixel is  $2^{24}$ , which is commonly called a 24-bit image. This format provides the most accuracy in image processing as it is the highest quality that can be obtained from an 8-bit color image sensor.

## **RGB 565**

The RGB 565 format is a reduction from the RGB 888 format. The purpose of this reduction is to reduce memory requirements from 3 bytes per pixel down to 2 bytes per pixel. The 565 definition specifies that 5-bit values are used to store the R and B channels, and 6-bits are used to store the G channel. The green channel gets the extra bit because the human eye is more sensitive to green light than red or blue. Conversion from RGB 888 to RGB 565 can be achieved simply by dropping or rounding the last 2 or 3 bits of the 8-bit values.

## YUV

The YUV color format was invented as a way to add color information to the grayscale format without breaking backward compatibility with devices that could only receive grayscale images. The Y or luma channel represents the brightness of the pixel, while the U and V channels represent blue and red chrominance values. The Y component is comparable to the simple grayscale format, while the chrominance values are difference values that represent how much brighter or darker the blue and red channels are from the total pixel brightness. Many cameras are capable of delivering this format as it is used in NTSC video transmissions for standard definition televisions. Unless the image processing application requires the transmission of video in an NTSC format, this format is not useful in image processing algorithms. This is primarily due to the fact that many image processing algorithms are based on (R, G, B) values.

## 4.3 Techniques

An FPGA-based computing environment provides unique abilities that enable multiple image processing techniques to be utilized. The computational structure of an FPGA is one massive fabric of individual computational elements that can be connected and configured in essentially limitless ways. The elements can be connected in series to form an arithmetic pipeline, grouped together into processing units, or function as memory buffers. However, the most significant advantage of the fabric, as it pertains to image processing, is not just the configurability, but the ability to have system components operate in parallel.

Real-time image processing is essentially performing the same algorithmic operations again-and-again on a continuous series of images. Processing video image data can therefore be classified as 'stream processing.' Regardless of the data format, the techniques for embedded image processing operations can be grouped into the following categories:

- 1. Inline

- 2. Offline

- 3. Cached Inline

These classifications were not found in the existing literature at the time this work was performed. The author defined these classifications while reflecting on the general design structure of the multiple FPGA logic components that were developed as part of this work. The intent of listing them here is to provide the reader with a framework to guide future FPGA logic development. It is important to note that the image processing techniques listed here only apply to the algorithms used to reduce the information contained in raw images to specific, actionable information, and not the tracking or decision making processes that would use that specific information in a mobile autonomous vehicle.

#### 4.4 Inline

Inline processing is the most basic of the image processing techniques. It is also the fastest. All data processing operations are organized into a single pipeline. Image data is pushed through the pipeline one pixel after another. A diagram of the computational architecture is shown in Figure 4.5.

Figure 4.5: Inline thresholded counter

As shown in the diagram, pixel data is clocked out of the camera 1 pixel at a time as a continuous stream. Each pixel is then clocked through the computational pipeline at a rate of 1 pixel per clock cycle. This can be viewed as pre-processing since the image data is passed through a processing engine prior to being stored in memory. The output of the inline processing unit can be a pixel stream of the same dimensions as the input, or it could be as simple as a single value. Example applications that can be implemented using the inline technique are those with independent pixel operations where each pixel can be processed without looking at adjacent pixels, such as color space conversion, thresholding, and segmentation.

#### 4.4.1 Example: Threshold Counter

To demonstrate an inline processing unit, consider a simple application that counts the number of pixels in an image that are brighter than a threshold value. This application requires the conversion of the input image stream from the RGB color space into grayscale, the detection of whether the pixel is brighter than a threshold value, and the counting of the number of pixels above that value. This can all be accomplished using the inline processing approach.

Figure 4.5 includes a source camera which outputs a  $640 \times 480$  image in 16-bit RGB 565 format. The image captured from the camera is clocked out one pixel per clock cycle over the camera's data bus. The speed of that bus is not relevant for this example, as it only

focuses on the flow of data. Following the camera are three computational pipeline stages labeled:  $f_1(x)$ ,  $f_2(x)$ , and  $f_3(x)$ .

The first computational stage,  $f_1(x)$ , converts the incoming 16-bit color RGB 565 stream into grayscale. This is required to determine the overall brightness value of a single pixel. This is accomplished using

$$Y = 0.3 \times R + 0.59 \times G + 0.11 \times B \tag{4.1}$$

where Y is the grayscale value and R, G, and B are the individual red, green and blue values

This algorithm does not depend on any future or prior values and only requires the data of each pixel to compute the grayscale brightness at each pixel and therefore meets the definition of an inline processing unit.

The second stage,  $f_2(x)$ , performs the thresholding. If the 8-bit grayscale value coming out of the first stage is above the threshold value then the  $f_2(x)$  stage outputs a binary 1, otherwise it outputs a 0 according to

$$Result = \begin{cases} 1, & \text{if } Y > Value \\ 0, & \text{if } Y <= Value \end{cases}$$

$$(4.2)$$

As this equation only requires the comparison of the incoming pixel value with a static value, it meets the criteria of an inline processing unit.

The third stage,  $f_3(x)$ , counts the number of pixels that are above the threshold. Since the input image dimensions are  $640 \times 480$ , the total pixel count in the image is 307,200. Theoretically, every pixel in the image could have a grayscale brightness value above the threshold, and therefore the counter would need to be able to count up to at least 307,200. For an unsigned binary counter, this implies a minimum of 19 bits. The counter in  $f_3(x)$  is incremented each time the output of  $f_2(x)$  is a binary 1 and is reset to zero at the start of each image.

In this example, a hypothetical scenario was used to demonstrate the inline processing design technique. The advantage of this technique is speed. Each stage only adds the latency required to implement its arithmetic function. And each of the three stages in this example design can be implemented in FPGA logic that only requires one or two clock cycles to complete. Therefore, these pipeline stages would implement the thresholded counter with the addition of only a few clock cycles of latency.

The disadvantage to the inline approach is that it can only be used to implement a limited set of algorithms. Each processing unit can only look at a single pixel at a time in the order that they were received. There can be no re-ordered or random access to the stream. Therefore, the applications that it can implement must be simple operations that can be considered 'pre-processing.'

### 4.5 Offline

The offline technique requires that the whole image be captured and stored in memory before processing begins. The 'offline' designation is meant to imply that the processing is not directly connected with the image data pipeline that streams pixel data out of the camera. Since the entire image is captured into memory before processing begins, the algorithms utilized can access any part of the image at random as there is no constrained sequential access pattern. Therefore the typical process flow is to capture the complete image to some form of memory and then turn that memory space over to a processing unit that accesses pixel data as needed.

Offline processing is the method used by CPU-based image processing systems. In these systems, an image is first captured from a camera device through some type of 'frame grabber.' This device interfaces with the camera, captures a full image streaming out of the camera, and transfers it to main memory. The image is then handed over to the program running on the CPU, which can access the entire image at random.

The major advantage of the offline method is the ability to access at random any data in the image. This allows for selective analysis of a limited portion of the image that would take too much time if attempted on every pixel location in the image or iterative access to pixel locations that are not known until runtime. The most significant drawback of offline processing is the requirement to wait until the full image is captured before processing can begin. This imposes additional latency equal to the full capture time of the image, which may impact real-time decision making in a vision-guided vehicle.

#### 4.5.1 Example: Image Normalization

To demonstrate the offline processing technique, an image normalization implementation will be considered. Normalization is a technique to more evenly distribute the pixel values in the image across the possible range of pixel values. This is sometimes referred to as contrast stretching or dynamic range expansion. The main goal of this algorithm is to correct the affects of bad lighting in images.

In visual imagery, this is used to 'brighten' under-exposed images or 'darken' overexposed images, which allows the human eye to perceive more of the image content. This prevents areas that would be 'too dark' or 'too bright' to be meaningful. In machine vision algorithms such as those used on a mobile vehicle, the justification is slightly different. Normalization of images in a video stream helps minimize lighting variation between images. Maintaining consistency in the relative spectral distribution in video stream images aids image analysis algorithms by reducing the amount of variation that needs to be tracked and compensated. For example, image processing algorithms that utilize static thresholding, such as the example described in Section 4.4.1, would require an input image stream that is not adversely affected by lighting changes.

**Figure 4.6:** Original cave image. Left portion is too dark to perceive content

**Figure 4.7:** Normalized cave image. Left portion is now plainly visible

Shown in Figure 4.6 is an unmodified image taken inside a cave. As can clearly be seen, the image is dark and some of the content, particularly the left side of the image, is not

discernible. The histogram of this image is shown in Figure 4.8, which also shows that the image is skewed toward the darker side of the spectrum. This dark-shift of the image was caused by the use of insufficient lighting equipment when the image was taken. While there is no method to reconstruct image data that was not captured, the image can be normalized to shift the content that is too dark to discern into a more visible spectrum.

Figure 4.8: Histogram of original image. Pixel brightness is skewed and not evenly spread across spectrum.

Figure 4.9: Histogram of normalized image. Pixel brightness is evenly spread across the spectrum.

Figure 4.7 shows the cave image with image normalization applied. As can been seen in the image, the once 'dark' areas of the image, which contained imperceptible content, are now plainly visible. Also, the histogram shown in Figure 4.9 shows that the image content has been spread more evenly across the total grayscale spectrum. The histogram does show gaps which are a result of the linear spreading algorithm. If desired, these can be eliminated through the use of a slight blur filter.

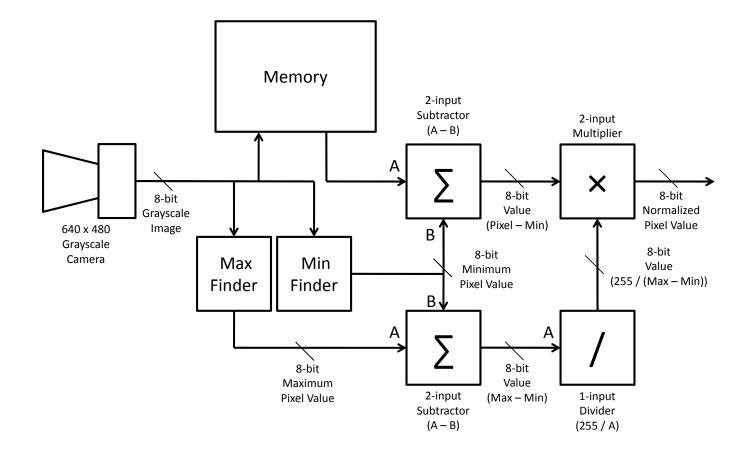

The algorithm to implement image normalization can vary in complexity from simple linear scaling to complex histogram distribution functions. In this example implementation, a simple linear scaling algorithm will be considered. Prior to computation, the maximum and minimum grayscale pixel values in the image need to be computed. These are utilized in

$$N(x,y) = (I(x,y) - MIN) \times \left(\frac{255}{Max - Min}\right)$$

(4.3)

where N(x, y) refers to a pixel at location (x, y) in the normalized image, and I(x, y) refers to a pixel at location (x, y) in the original image. In this algorithm, all the pixel values are shifted down by the minimum value and are then scaled up to fill the entire 255 value range in typical 8-bit grayscale images. For example if the image only contains pixel values in the range [30-200], then every pixel value is first shifted down by 30, which results in a range of [0-170]. Then the image is scaled to fill the available range by multiplying each pixel value by  $\frac{255}{170}$ , which results in a full range of [0-255].

The FPGA circuit implementation of the image normalization algorithm is shown in Figure 4.10. In this implementation the image data that is streamed out of the camera is stored in some form of memory. In addition to being streamed to memory, the image pixel data is fed through inline pre-processing blocks to determine the maximum and minimum values.