Brigham Young University BYU ScholarsArchive

Theses and Dissertations

2007-06-19

# Performance of MIMO Space-Time Coding Algorithms on a Parallel DSP Test Platform

Beau C. Neal Brigham Young University - Provo

Follow this and additional works at: https://scholarsarchive.byu.edu/etd

Part of the Electrical and Computer Engineering Commons

## **BYU ScholarsArchive Citation**

Neal, Beau C., "Performance of MIMO Space-Time Coding Algorithms on a Parallel DSP Test Platform" (2007). *Theses and Dissertations*. 928. https://scholarsarchive.byu.edu/etd/928

This Thesis is brought to you for free and open access by BYU ScholarsArchive. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of BYU ScholarsArchive. For more information, please contact scholarsarchive@byu.edu, ellen\_amatangelo@byu.edu.

# PERFORMANCE OF MIMO SPACE-TIME CODING ALGORITHMS ON A PARALLEL DSP TEST PLATFORM

by

Beau C. Neal

A thesis submitted to the faculty of

Brigham Young University

in partial fulfillment of the requirements for the degree of

Master of Science

Department of Electrical and Computer Engineering

Brigham Young University

August 2007

Copyright © 2007 Beau C. Neal

All Rights Reserved

## BRIGHAM YOUNG UNIVERSITY

## GRADUATE COMMITTEE APPROVAL

of a thesis submitted by

Beau C. Neal

This thesis has been read by each member of the following graduate committee and by majority vote has been found to be satisfactory.

Date

James K. Archibald, Chair

Date

Brian D. Jeffs

Date

Doran K. Wilde

## BRIGHAM YOUNG UNIVERSITY

As chair of the candidate's graduate committee, I have read the thesis of Beau C. Neal in its final form and have found that (1) its format, citations, and bibliographical style are consistent and acceptable and fulfill university and department style requirements; (2) its illustrative materials including figures, tables, and charts are in place; and (3) the final manuscript is satisfactory to the graduate committee and is ready for submission to the university library.

Date

James K. Archibald Chair, Graduate Committee

Accepted for the Department

Michael A. Jensen Chair

Accepted for the College

Alan R. Parkinson Dean, Ira A. Fulton College of Engineering and Technology

## ABSTRACT

# PERFORMANCE OF MIMO SPACE-TIME CODING ALGORITHMS ON A PARALLEL DSP TEST PLATFORM

Beau C. Neal

Department of Electrical and Computer Engineering

Master of Science

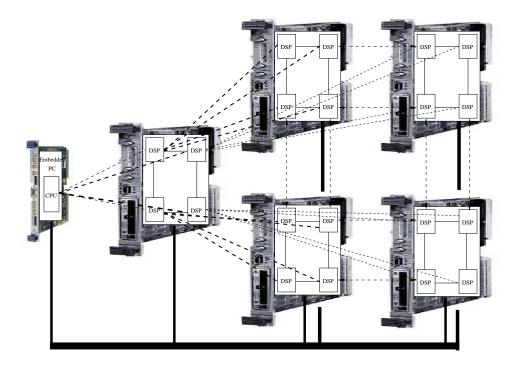

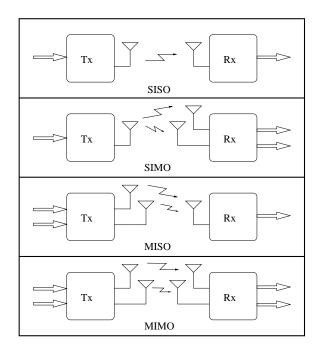

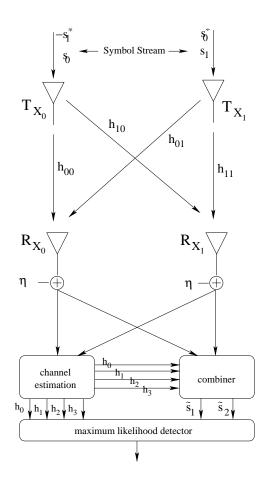

Commercial Off The Shelf (COTS) hardware has the advantages of low cost, modularity, and is easily upgraded. For Multiple-Input Multiple-Output (MIMO) space-time algorithms to be practical they must have the processing capability to execute in real-time. This makes COTS ideal for real-time MIMO research where the processing power increases exponentially with a linear increase in antennas. The BYU Electrical Engineering wireless lab has designed and built an eight processor transmitter and a twenty processor receiver to research and develop MIMO wireless communication.

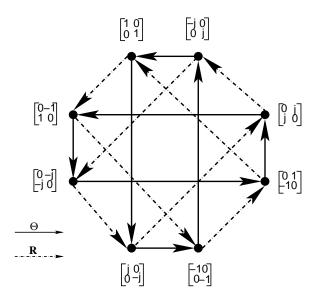

The Alamouti,  $2 \times 2$  and  $4 \times 4$  differential space-time MIMO algorithms have been partially implemented on the receiver using a variety of common parallel processing topologies to include: bus, line/ring, star, grid, hypercube, binary tree, and pyramid. Processor and inter-processor communication benchmarks were measured and used to quickly explore the performance of the previously mentioned topologies

without expending time and effort on a full implementation of these MIMO algorithms using each topology. This methodology has the benefit of the creation of software libraries that can be used for testing or for complete MIMO algorithm implementation in the future.

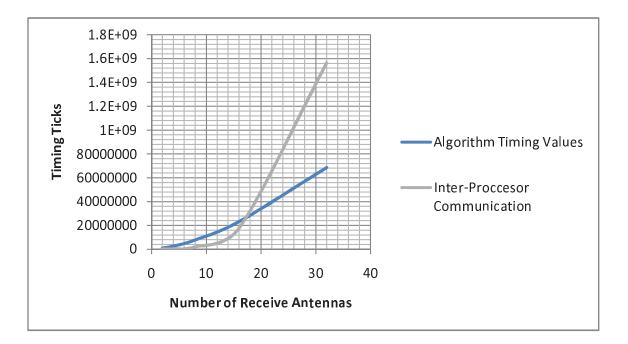

This thesis shows that a simple bus-based topology gives the best results when combined with the  $4 \times 4$  differential space-time algorithm. This thesis also shows that if the number of receiving channels and processors increase at the same rate as the  $2 \times 2$  to the  $4 \times 4$  differential cases, then the ratio of decoding processing time to inter-processor communication time is reduced. If this trend continues, inter-processor communication will require more processing time than the actual space-time decoding algorithm.

Due to the exponential increase in required processing, doubling the processing requirements obtained from the  $4 \times 4$  case is not an adequate solution to implement real-time  $8 \times 8$  differential decoding. As such, the BYU wireless lab's test system does not have enough processors to implement real-time  $8 \times 8$  differential decoding. The BYU wireless lab should concentrate on a complete  $4 \times 4$  implementation with increased bandwidth to make full use of the available processing power. The  $8 \times 8$  case should also be explored but without the expectation of real-time communication. However, with the test system, additional DSP processors can easily be added to allow for increased processing requirements.

## ACKNOWLEDGMENTS

I would like to express my gratitude to all of the people that kept pushing me to finish this thesis. I would also like to thank those that made this possible through their hard work, dedication, and love. I thank you all.

## Table of Contents

| Acknowledgements |                |         | 2                             | xiii |       |  |

|------------------|----------------|---------|-------------------------------|------|-------|--|

| Li               | List of Tables |         |                               | x    | xxiii |  |

| Li               | st of          | Figure  | es                            | xx   | vii   |  |

| 1                | Intr           | roducti | on                            |      | 1     |  |

|                  | 1.1            | Comm    | ercial-Off-The-Shelf Hardware |      | 3     |  |

|                  | 1.2            | MIMC    | Space-Time Codes              |      | 4     |  |

|                  | 1.3            | BYU     | Wireless Lab                  |      | 5     |  |

|                  | 1.4            | Object  | sive                          |      | 7     |  |

|                  | 1.5            | Overvi  | ew                            |      | 9     |  |

| <b>2</b>         | MI             | MO Re   | eal-Time System               |      | 11    |  |

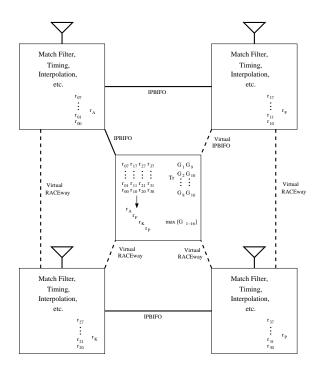

|                  | 2.1            | System  | n Level Diagram               |      | 12    |  |

|                  | 2.2            | Transr  | nitter                        |      | 13    |  |

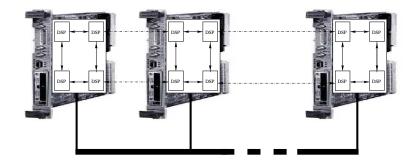

|                  |                | 2.2.1   | DSP and Host Hardware         |      | 15    |  |

|                  |                | 2.2.2   | RF Transmission               |      | 18    |  |

|                  | 2.3            | Receiv  | er                            |      | 19    |  |

|                  |                | 2.3.1   | RF Front-End                  |      | 20    |  |

|                  |                | 2.3.2   | DSP and Host Hardware         |      | 20    |  |

|                  | 2.4            | Summ    | ary                           |      | 23    |  |

| 3        | Par | allel P | rocessing                                | <b>25</b> |

|----------|-----|---------|------------------------------------------|-----------|

|          | 3.1 | Need 2  | For Parallel Processing                  | 26        |

|          | 3.2 |         |                                          | 27        |

|          | 3.3 |         |                                          | 28        |

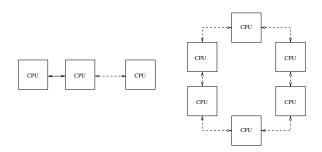

|          |     | 3.3.1   | Bus Parallel Processing                  | 29        |

|          |     | 3.3.2   | Line and Ring Parallel Processing        | 30        |

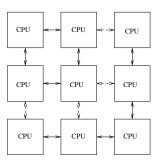

|          |     | 3.3.3   | Mesh Parallel Processing                 | 32        |

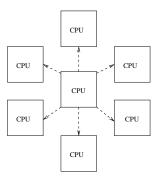

|          |     | 3.3.4   | Star Parallel Processing                 | 33        |

|          |     | 3.3.5   | Hypercube or n-Cube Parallel Processing  | 35        |

|          |     | 3.3.6   | Binary Tree Parallel Processing          | 37        |

|          |     | 3.3.7   | Pyramid Parallel Processing              | 38        |

|          |     | 3.3.8   | Summary                                  | 39        |

| 4        | Spa | ce-Tin  | ne Algorithms                            | 41        |

|          | 4.1 | Backg   | round                                    | 42        |

|          | 4.2 | Space-  | Time Coding Algorithms                   | 43        |

|          |     | 4.2.1   | Alamouti Space-Time Codes                | 43        |

|          |     | 4.2.2   | 2 x 2 Differential Space-Time Modulation | 48        |

|          |     | 4.2.3   | 4 x 4 Differential Space-Time Modulation | 50        |

|          | 4.3 | Summ    | ary                                      | 51        |

| <b>5</b> | Spa | ce-Tin  | ne Algorithms and Parallel Processing    | 53        |

|          | 5.1 | Bench   | marks                                    | 53        |

|          | 5.2 | Assum   | ptions and Methods                       | 55        |

|          | 5.3 | Alamo   | outi Parallel Processing                 | 56        |

|          |     | 5.3.1   | Bus                                      | 57        |

|          |     | 5.3.2   | Line/Ring                                | 58        |

|   |                      | 5.3.3   | $\operatorname{Grid}/\operatorname{Mesh}$    | 59 |

|---|----------------------|---------|----------------------------------------------|----|

|   |                      | 5.3.4   | Star                                         | 59 |

|   | 5.4                  | 2 x 2 1 | Differential Space-Time Parallel Processing  | 59 |

|   |                      | 5.4.1   | Bus                                          | 61 |

|   |                      | 5.4.2   | Line/Ring                                    | 62 |

|   |                      | 5.4.3   | Grid/Mesh                                    | 63 |

|   |                      | 5.4.4   | Star                                         | 63 |

|   | 5.5                  | 4 x 4 2 | Differential Space-Time Parallel Processing  | 64 |

|   |                      | 5.5.1   | Bus                                          | 66 |

|   |                      | 5.5.2   | Line/Ring                                    | 67 |

|   |                      | 5.5.3   | Grid/Mesh                                    | 68 |

|   |                      | 5.5.4   | Star                                         | 69 |

|   |                      | 5.5.5   | Hypercube                                    | 70 |

|   |                      | 5.5.6   | Binary Tree                                  | 71 |

|   |                      | 5.5.7   | Pyramid                                      | 73 |

|   | 5.6                  | Summ    | nary                                         | 74 |

| 6 | $\operatorname{Res}$ | ults    |                                              | 75 |

|   | 6.1                  | Metho   | odology                                      | 75 |

|   | 6.2                  |         | nunications Processors                       | 78 |

|   | 6.3                  | Alamo   | outi Real-Time Processing                    | 79 |

|   |                      | 6.3.1   | Bus                                          | 80 |

|   |                      | 6.3.2   | Line/Ring                                    | 81 |

|   |                      | 6.3.3   | Comparison                                   | 81 |

|   | 6.4                  | 2 x 2 1 | Differential Space-Time Real-Time Processing | 82 |

|   |                      | 6.4.1   | Bus                                          | 83 |

|   |                                                                       | 6.4.2                                             | Line/Ring                                    | 84                              |

|---|-----------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------|---------------------------------|

|   |                                                                       | 6.4.3                                             | Star                                         | 85                              |

|   |                                                                       | 6.4.4                                             | Comparison                                   | 85                              |

|   | 6.5                                                                   | 4 x 4 2                                           | Differential Space-Time Real-Time Processing | 87                              |

|   |                                                                       | 6.5.1                                             | Bus                                          | 88                              |

|   |                                                                       | 6.5.2                                             | Line/Ring                                    | 89                              |

|   |                                                                       | 6.5.3                                             | $\operatorname{Grid}/\operatorname{Mesh}$    | 89                              |

|   |                                                                       | 6.5.4                                             | Star                                         | 89                              |

|   |                                                                       | 6.5.5                                             | Hypercube                                    | 91                              |

|   |                                                                       | 6.5.6                                             | Binary Tree                                  | 91                              |

|   |                                                                       | 6.5.7                                             | Pyramid                                      | 93                              |

|   |                                                                       | 6.5.8                                             | Comparison                                   | 93                              |

|   | 6.6                                                                   | Interp                                            | retation                                     | 95                              |

| 7 | Con                                                                   | clusio                                            | n                                            | 99                              |

|   | 7.1                                                                   | Discus                                            | ssion and Recommendations                    | 99                              |

|   | 7.2                                                                   | Future                                            | e Work                                       | 101                             |

|   | _                                                                     |                                                   |                                              |                                 |

| Α | Ben                                                                   |                                                   |                                              |                                 |

|   | 201                                                                   | chmar                                             |                                              | 103                             |

|   | A.1                                                                   |                                                   | <b>'ks</b><br>l Memory Benchmarks            | <b>103</b><br>103               |

|   |                                                                       | Globa                                             |                                              |                                 |

|   | A.1                                                                   | Globa<br>Flash                                    | l Memory Benchmarks                          | 103                             |

|   | A.1<br>A.2                                                            | Globa<br>Flash<br>Arithr                          | l Memory Benchmarks                          | 103<br>105                      |

|   | A.1<br>A.2<br>A.3                                                     | Globa<br>Flash<br>Arithr<br>Memo                  | I Memory Benchmarks                          | 103<br>105<br>106               |

|   | A.1<br>A.2<br>A.3<br>A.4                                              | Globa<br>Flash<br>Arithn<br>Memo<br>IPBIF         | I Memory Benchmarks                          | 103<br>105<br>106<br>108        |

|   | <ul><li>A.1</li><li>A.2</li><li>A.3</li><li>A.4</li><li>A.5</li></ul> | Globa<br>Flash<br>Arithr<br>Memo<br>IPBIF<br>RACE | I Memory Benchmarks                          | 103<br>105<br>106<br>108<br>111 |

Bibliography

## List of Tables

| 4.1  | The Encoding and Transmission Sequence - Matrix ${\bf S}$                       | 45 |

|------|---------------------------------------------------------------------------------|----|

| 4.2  | Channel Matrix Components (As Seen by the Receiver)                             | 46 |

| 4.3  | Definition of the Received Signals                                              | 47 |

| 5.1  | Inter-Processor Communication Benchmark Comparison                              | 54 |

| 5.2  | DSP Benchmark Comparison (MB/s)                                                 | 54 |

| 0.2  |                                                                                 | 01 |

| 6.1  | Communications Processor Tasks & Timing Results                                 | 79 |

| 6.2  | Alamouti Bus Tasks & Timing Results                                             | 81 |

| 6.3  | Alamouti Line/Ring Tasks & Timing Results                                       | 81 |

| 6.4  | Alamouti Real-Time Timing Results Comparison                                    | 82 |

| 6.5  | $2\times 2$ Differential Space-Time Bus Tasks & Timing Results $\ . \ . \ .$ .  | 84 |

| 6.6  | $2\times 2$ Differential Space-Time Line/Ring Tasks & Timing Results $~$ .      | 85 |

| 6.7  | $2\times 2$ Differential Space-Time Star Tasks & Timing Results                 | 86 |

| 6.8  | $2\times 2$ Differential Real-Time Timing Results Comparison $\hdots$           | 87 |

| 6.9  | $4\times 4$ Differential Space-Time Bus Tasks & Timing Results $\ . \ . \ .$ .  | 89 |

| 6.10 | $4\times 4$ Differential Space-Time Line/Ring Tasks & Timing Results $~$ .      | 90 |

| 6.11 | $4\times 4$ Differential Space-Time Grid Tasks & Timing Results $\ \ . \ . \ .$ | 90 |

| 6.12 | $4\times 4$ Differential Space-Time Star Tasks & Timing Results                 | 91 |

| 6.13 | $4\times 4$ Differential Space-Time Hypercube Tasks & Timing Results $~$ .      | 92 |

| 6.14 | $4\times 4$ Differential Space-Time Binary Tree Tasks & Timing Results $~$ .    | 92 |

| 6.15 | $4 \times 4$ Differential Space-Time Pyramid Tasks & Timing Results $\ldots$    | 93 |

| 6.16 | $4\times 4$ Differential Real-Time Timing Results Comparison $\hfill \ldots \hfill hfill \ldots \hfill \ldots \hfill \ldots \hfill \ldots \hfill \ldots \hfill \ldots \hfill \ldots \h$ | 94  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.17 | Differential Space-Time Coding Comparison and Rate of Increase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 96  |

| A.1  | Reading from Global Memory (MB/s) $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 104 |

| A.2  | Writing to Global Memory (MB/s) $\ \ldots \ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 104 |

| A.3  | Writing VME - DSP to Another Board's Global Memory (MB/s) $~$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 104 |

| A.4  | Reading VME - Another Board's Global Memory to DSP (MB/s) $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 105 |

| A.5  | Reading from Flash Memory (MB/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 105 |

| A.6  | Addition (MB/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 106 |

| A.7  | Subtraction (MB/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 106 |

| A.8  | Multiplication (MB/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 107 |

| A.9  | Division $(MB/s)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 107 |

| A.10 | Moving Data from IDRAM to IDRAM (MB/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 108 |

| A.11 | Moving Data from SDRAM to SDRAM (MB/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 108 |

| A.12 | Moving Data from IDRAM to SDRAM (MB/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 109 |

| A.13 | Moving Data from SDRAM to IDRAM (MB/s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 109 |

| A.14 | Library Function memcpy<br>() - IDRAM to IDRAM (MB/s) $\hfill \ldots \ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 109 |

| A.15 | Library Function memcpy<br>() - SDRAM to SDRAM (MB/s) $\ . \ . \ .$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 110 |

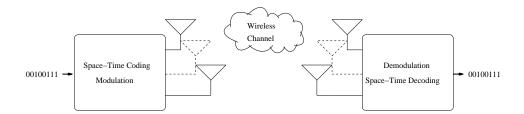

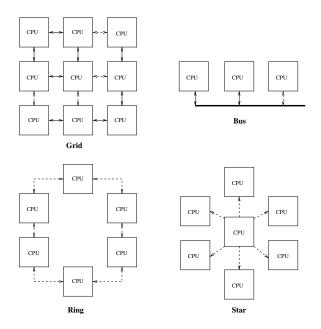

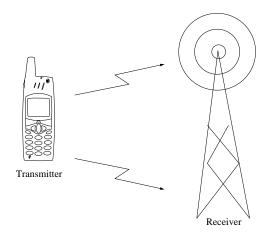

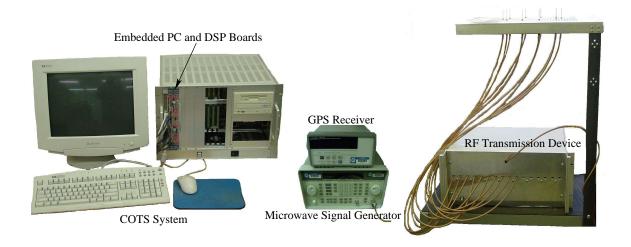

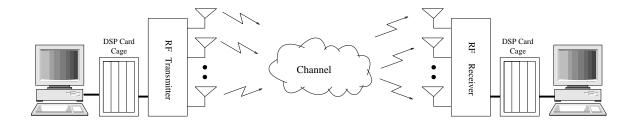

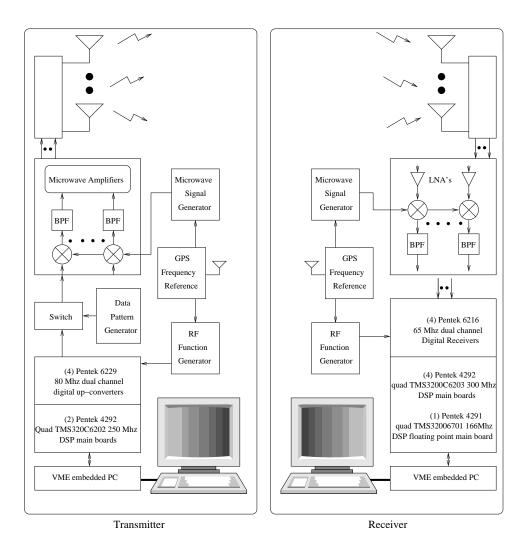

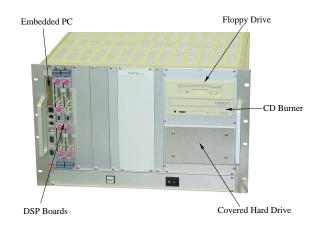

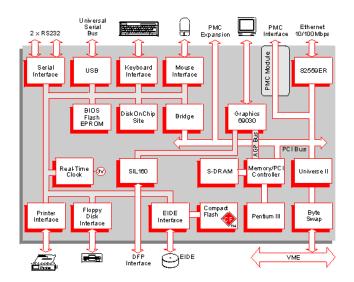

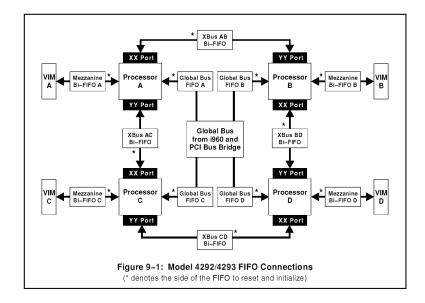

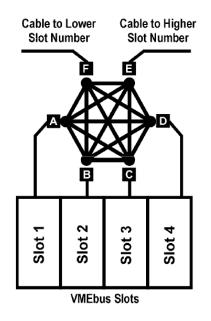

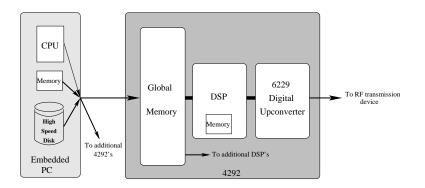

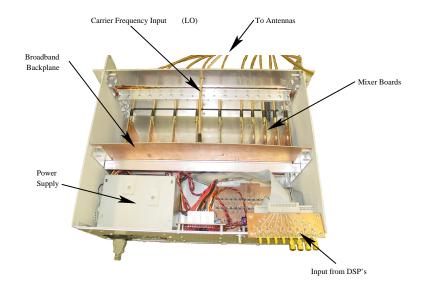

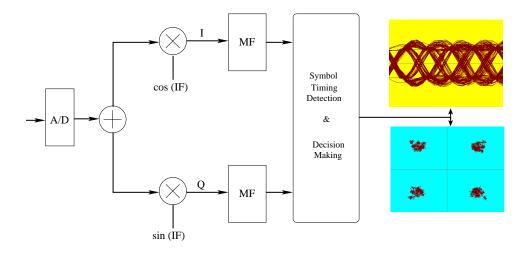

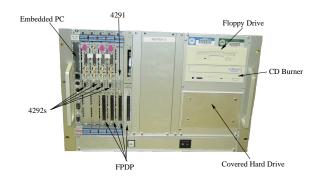

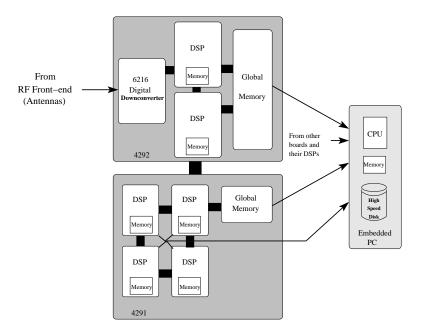

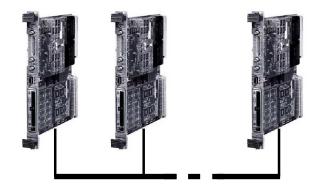

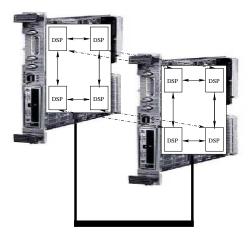

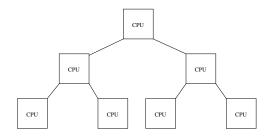

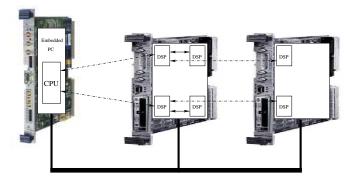

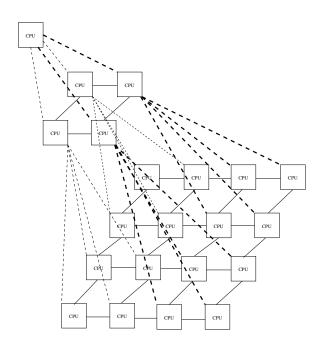

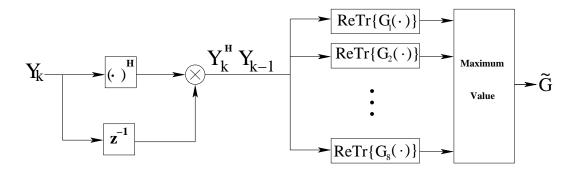

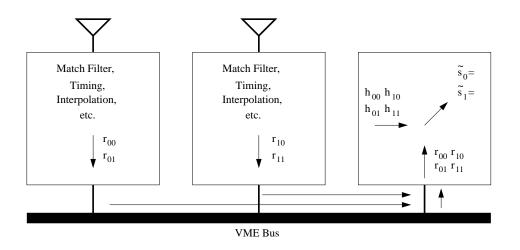

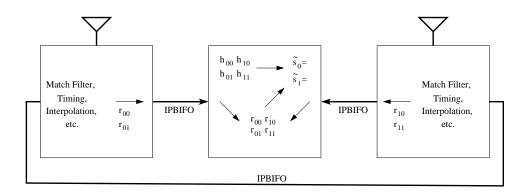

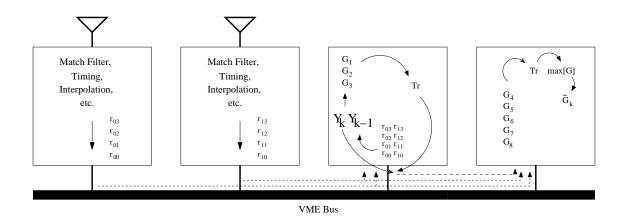

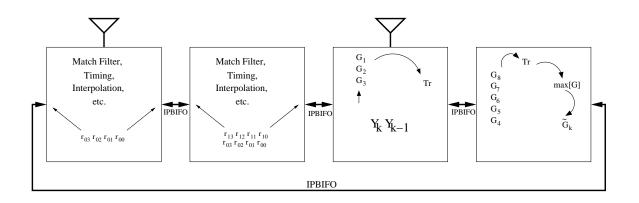

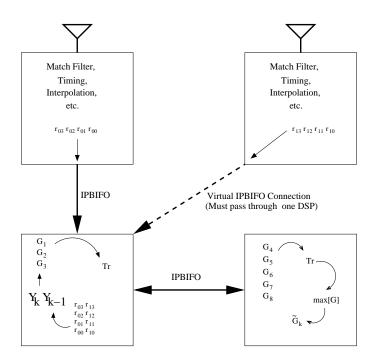

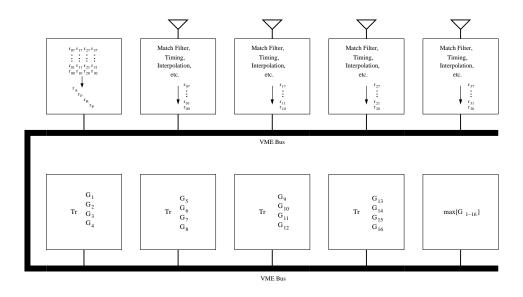

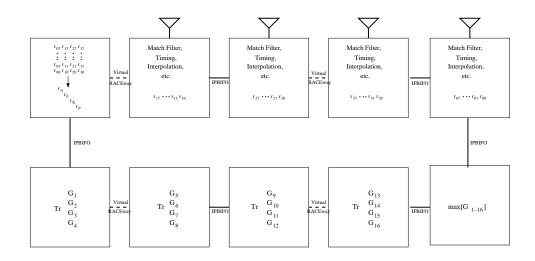

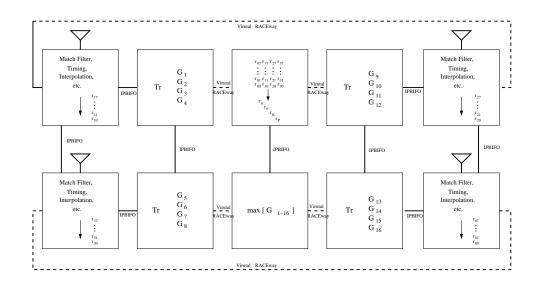

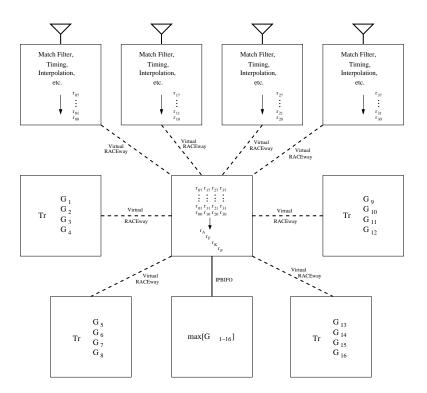

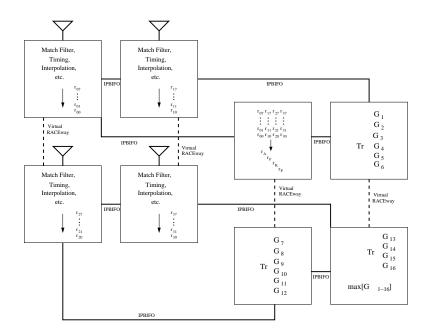

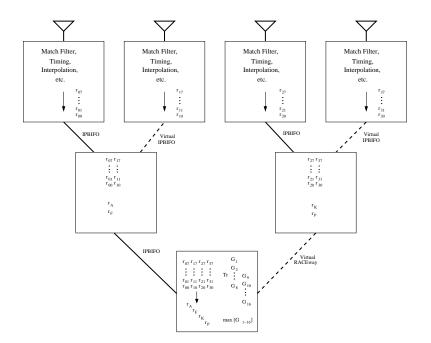

| A.16 | Library Function memcpy<br>() - IDRAM to SDRAM (MB/s) $\ . \ . \ .$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 110 |