Brigham Young University BYU ScholarsArchive

Theses and Dissertations

2006-09-28

# Design and Realization of a Single Stage Sigma-Delta ADC With Low Oversampling Ratio

Yongjie Cheng Brigham Young University - Provo

Follow this and additional works at: https://scholarsarchive.byu.edu/etd

Part of the Electrical and Computer Engineering Commons

### **BYU ScholarsArchive Citation**

Cheng, Yongjie, "Design and Realization of a Single Stage Sigma-Delta ADC With Low Oversampling Ratio" (2006). *Theses and Dissertations*. 796. https://scholarsarchive.byu.edu/etd/796

This Dissertation is brought to you for free and open access by BYU ScholarsArchive. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of BYU ScholarsArchive. For more information, please contact scholarsarchive@byu.edu, ellen\_amatangelo@byu.edu.

# DESIGN AND REALIZATION OF A SINGLE STAGE SIGMA-DELTA ADC WITH LOW OVERSAMPLING RATIO

by

Yongjie Cheng

A dissertation submitted to the faculty of

Brigham Young University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

Brigham Young University

December 2006

## BRIGHAM YOUNG UNIVERSITY

## GRADUATE COMMITTEE APPROVAL

## of a dissertation submitted by

## Yongjie Cheng

This dissertation has been read by each member of the following graduate committee and by majority vote has been found to be satisfactory.

Date

David J. Comer, Chair

Date

Donald T. Comer

Date

Michael D. Rice

Date

Doran K. Wilde

Date

Richard H. Selfridge

### BRIGHAM YOUNG UNIVERSITY

As chair of the candidate's graduate committee, I have read the dissertation of Yongjie Cheng in its final form and have found that (1) its format, citations, and bibliographical style are consistent and acceptable and fulfill university and department style requirements; (2) its illustrative materials including figures, tables, and charts are in place; and (3) the final manuscript is satisfactory to the graduate committee and is ready for submission to the university library.

Date

David J. Comer Advisor Chair, Graduate Committee

Accepted for the Department

Michael J. Wirthlin Graduate Coordinator

Accepted for the College

Alan R. Parkinson Dean, Ira A. Fulton College of Engineering and Technology

### ABSTRACT

## DESIGN AND REALIZATION OF A SINGLE STAGE SIGMA-DELTA ADC WITH LOW OVERSAMPLING RATIO

Yongjie Cheng Department of Electrical Engineering Doctor of Philosophy

Due to the rapid growth of the communication market, a large amount of research is in process toward a high speed and high resolution sigma-delta A/D converter. This dissertation focuses on the design of a single-stage sigma-delta A/D converter with very low oversampling ratio for the wireless application. An architecture for a multibit singlestage delta-sigma A/D converter with two-step quantization is proposed. Both the MSB and LSB signals produced by the two-step quantization are fed back simultaneously to all integrator stages, making it suitable for low oversampling ratios. The two-step ADC avoids the problem that the complexity of an internal flash ADC increases exponentially with each added bit. A segmented architecture with coarse/fine DEM and DAC is proposed to reduce the complexity of DEM and DAC due to the large internal quantizer. The consequence of the segmentation, mismatch between coarse and fine DACs can be

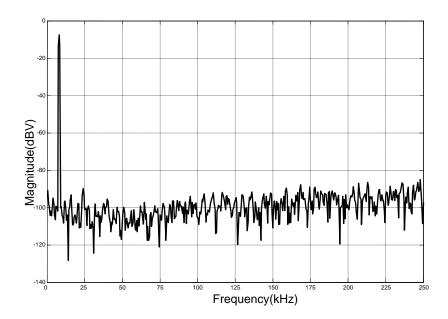

noise-shaped by using a digital requantization (REQ) algorithm. A second-order singlestage sigma-delta A/D converter with 8-bit two-step inner quantization is proposed in this dissertation, which employs the feed-forward branches to reduce the integrator output swing. The proposed modulator is implemented with TSMC 0.25  $\mu$ m mixed-signal process, using the switched-capacitor circuit. The measured system achieves the dynamic range of 70 dB under an oversampling ratio of 16 with the REQ algorithm reducing the noise floor in the signal bandwidth by 20 dB.

#### ACKNOWLEDGMENTS

My sincere gratitude goes to the chair of my committee, Dr. David Comer, for his great supervising and support to help me complete my research work at the Brigham Young University. I also want to thank my former advisor, Dr. Craig Petrie, for his guidance, advice and encouragement during my first three years' research.

Furthermore, my deep thanks extend to the other members of committee, Dr. Donald Comer, Dr. Michael Rice, Dr. Doran Wilde, and Dr Richard Selfridge for their valuable comments and suggestions on this research.

This work is supported by Intel Inc. For this, I am thankful to Mr. Dennis Newmeyer, Dr. Vijay Nair, and Dr. Yorgos Palaskas for the valuable technical discussion.

Also, I would like to acknowledge all my colleagues, Tim Hollis, Lisha Li, Xiongliang Lai, and Adrian Genz for many discussions and help.

Thanks also go to my parents, brother, and sister for their unfailing love.

Finally, I would like to dedicate this thesis to my wife, Gendi Yang, for her love and support through my graduate studies. Without her, my study would not be possible.

## TABLE OF CONTENTS

| L      | LIST OF TABLES xi |                                            |      |

|--------|-------------------|--------------------------------------------|------|

| L      | IST C             | OF FIGURES                                 | xiii |

| 1      | In                | troduction                                 | 1    |

|        | 1.1               | Nyquist-rate ADC                           | 2    |

|        | 1.2               | Oversampled Converters                     | 7    |

|        | 1.3               | Research Contributions                     | 11   |

|        | 1.4               | Dissertation Outline                       | 14   |

| 2      | Sig               | gma Delta ADC Fundamentals                 | 17   |

|        | 2.1               | Single Stage Modulators                    |      |

|        | 2.2               | Cascade Modulators                         |      |

|        | 2.3               | Multibit Modulators                        |      |

|        | 2.4               | Conclusion                                 |      |

| 3 Inne |                   | ner Quantization with Large Number of Bits | 29   |

|        | 3.1               | Introduction                               |      |

|        | 3.2               | Two-step Quantization                      |      |

|        | 3.3               | Noise Shaped Requantization                | 35   |

|        | 3.4               | Conclusion                                 | 44   |

| 4      | Ar                | chitecture and Behavior Simulation         | 47   |

|        | 4.1               | System Architecture                        | 48   |

|        | 4.2               | Matlab Simulations                         | 51   |

|   | 4.3 E  | ffects of Nonidealities        | . 52 |

|---|--------|--------------------------------|------|

|   | 4.3.1  | Finite DC Gain of Integrators  | . 52 |

|   | 4.3.2  | Finite GBW and Slew Rate       | . 55 |

|   | 4.3.3  | Capacitor Mismatch of DACs     | . 56 |

|   | 4.3.4  | Offsets of Two-Step Quantizer  | . 63 |

|   | 4.3.5  | Thermal Noise and Clock Jitter | . 65 |

|   | 4.4 S  | imulation Results Summary      | . 68 |

| 5 | СМО    | S VLSI Implementation          | . 69 |

|   | 5.1 T  | wo-Step ADC                    | . 69 |

|   | 5.1.1  | Flash ADC                      | . 71 |

|   | 5.1.2  | Comparators                    | . 74 |

|   | 5.1.3  | Subtractor                     | . 84 |

|   | 5.2 In | ntegrator and Adder            | . 89 |

|   | 5.3 0  | )pamp                          | . 94 |

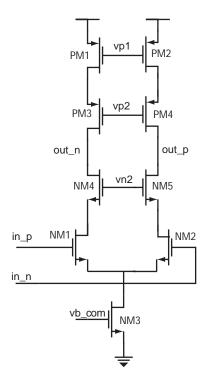

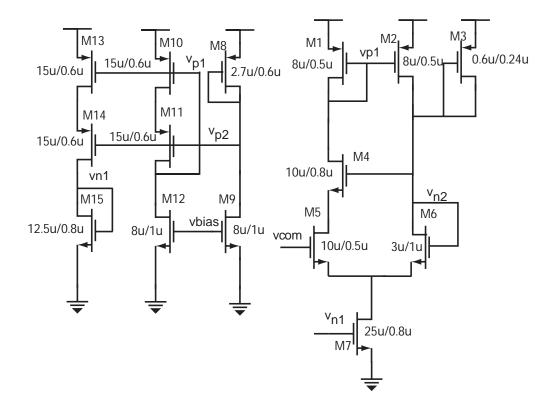

|   | 5.3.1  | Telescopic Architecture        | . 95 |

|   | 5.3.2  | Folded-Cascode Architecture    | 101  |

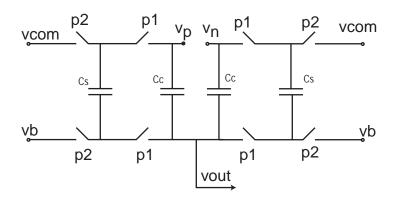

|   | 5.3.3  | Common-Mode Feedback           | 103  |

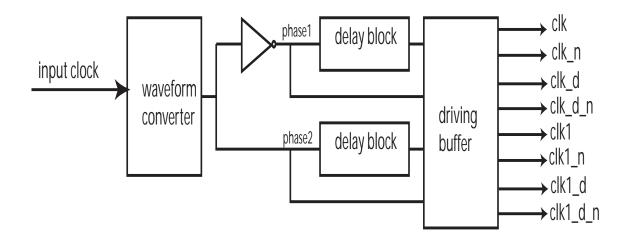

|   | 5.4 E  | Digital Circuitry              | 105  |

|   | 5.4.1  | Clock Generator                | 105  |

|   | 5.4.2  | Digital Feedback Block         | 106  |

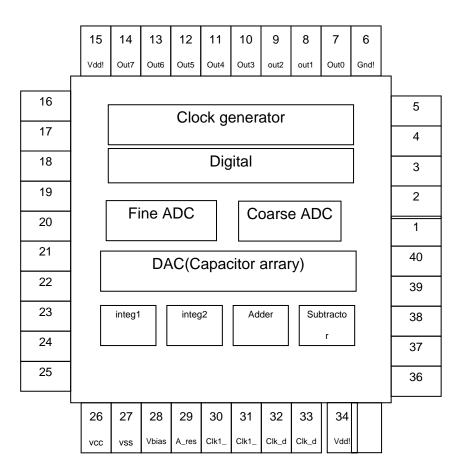

|   | 5.5 F  | loor plan and layout design    | 112  |

|   | 5.5.1  | Floor plan                     | 112  |

|   | 5.5.2  | Layout Design                  | 114  |

| 6 | Exper  | imental Results                | 117  |

|   | 6.1 T  | est Setup                      | 117  |

| B | Bibliography |                                        |     |

|---|--------------|----------------------------------------|-----|

|   | 7.2          | Future Work                            | 132 |

|   | 7.1          | Contributions of the Dissertation      | 129 |

| 7 | Con          | clusions and Future Work               | 129 |

|   | 6.3          | Test Results                           | 121 |

|   | 6.2          | Printed Board and Environment Features | 117 |

## LIST OF TABLES

| Table 4.1 | Circuit design parameters                                               | 68  |

|-----------|-------------------------------------------------------------------------|-----|

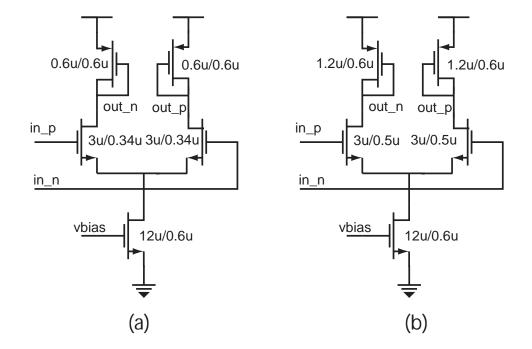

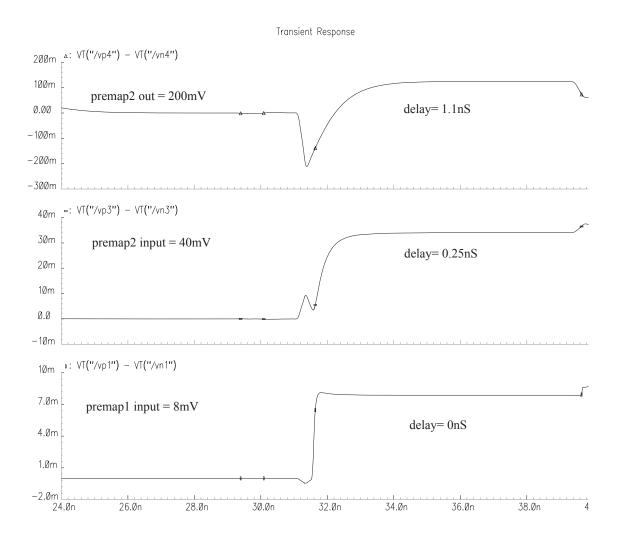

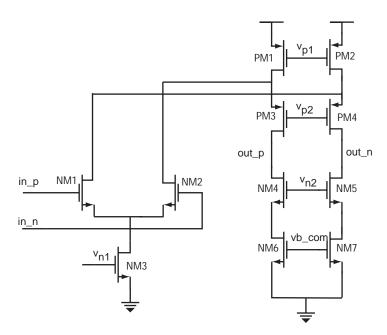

| Table 5.1 | Performance summary of the two preamplifiers inside the comparator      | 79  |

| Table 5.2 | Summary of the coarse and fine DAC inside the integrator                | 92  |

| Table 5.3 | The performance summary of the telescopic opamps                        | 100 |

| Table 5.4 | The performance summary of the folded-cascode opamp                     | 104 |

| Table 6.1 | The performance comparison with or without the requantization algorithm | 126 |

| Table 6.2 | Summary of the measured system                                          | 126 |

## LIST OF FIGURES

| Figure 1.1 | Typical Digital Signal Processing System                                                                                               | 1  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2 | Spectrum of input signal                                                                                                               | 3  |

| Figure 1.3 | Anti-aliasing filter for nyquist-rate ADC                                                                                              | 3  |

| Figure 1.4 | Linear model of the nyquist-rate ADC.                                                                                                  | 4  |

| Figure 1.5 | Sawtooth waveform of the quantization noise                                                                                            | 5  |

| Figure 1.6 | Assumed probability density function for the quantization error $E_q$                                                                  | 6  |

| Figure 1.7 | Sigma-delta ADC overview (a) block diagram (b) spectrum content                                                                        | 8  |

| Figure 1.8 | Signal Flow of the Sigma-Delta modulator                                                                                               | 10 |

| Figure 2.1 | Block diagram of a second-order single-stage sigma-delta modulator                                                                     | 19 |

| Figure 2.2 | Block diagram of an Lth-order single-stage sigma-delta modulator                                                                       | 20 |

| Figure 2.3 | Block diagram of a third-order modulator in a cascade architecture                                                                     | 22 |

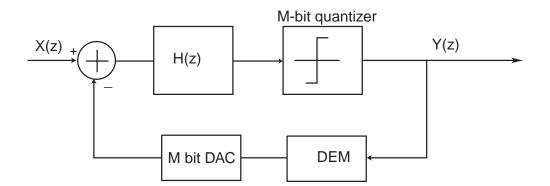

| Figure 2.4 | A multibit sigma-delta modulator with dynamic element matching(DEM)                                                                    | 25 |

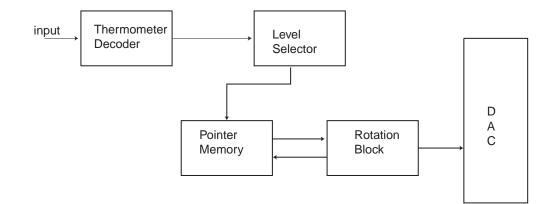

| Figure 2.5 | Block diagram of the individual level averaging (ILA) block                                                                            | 26 |

| Figure 2.6 | Graphical Explanation of DEM Operation                                                                                                 | 27 |

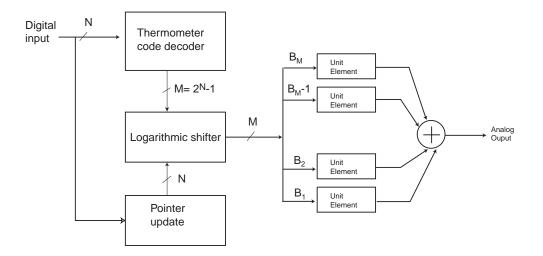

| Figure 2.7 | Block diagram of the data weighted averaging (DWA) method                                                                              | 28 |

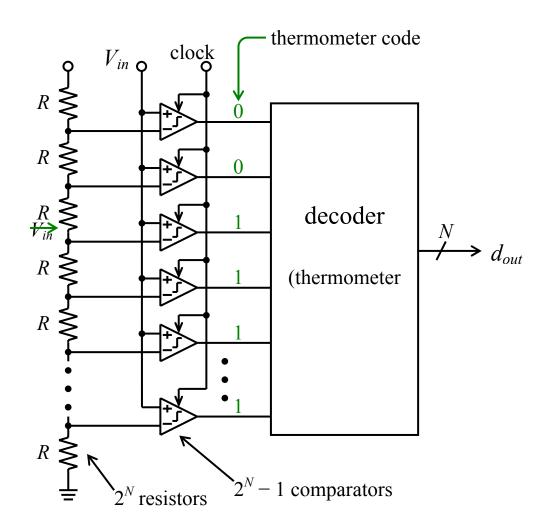

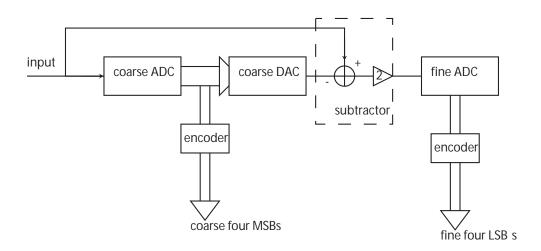

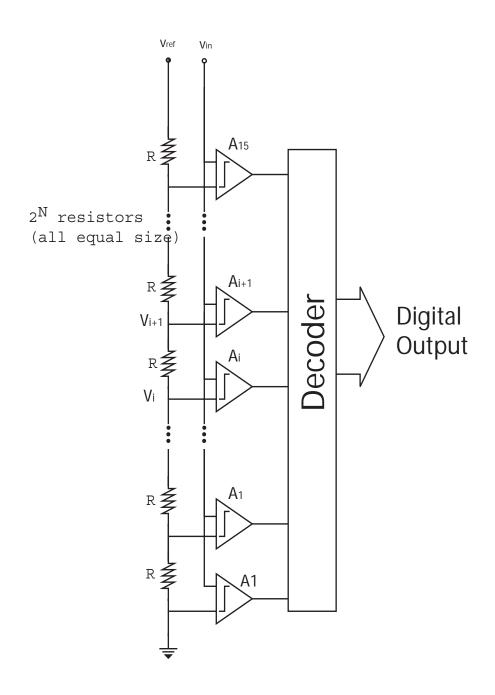

| Figure 3.1 | Block diagram of the flash ADC                                                                                                         | 30 |

| Figure 3.2 | Block diagram of the quantizer and last integrator in a typical single-stage multibit sigma-delta modulator                            |    |

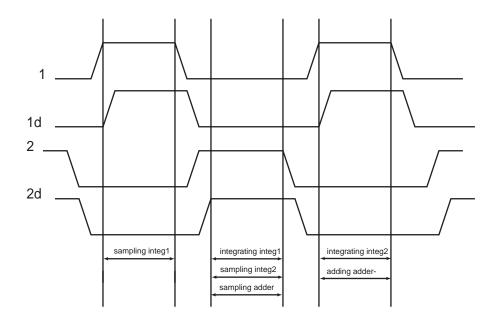

| Figure 3.3 | Timing diagram for Figure 3.2                                                                                                          | 34 |

| Figure 3.4 | Two-step quantizer with time slot allocation                                                                                           | 34 |

| Figure 3.5 | The system SNR in a second-order $\Sigma\Delta$ modulator versus the offset of coarse/fine ADCs inside an eight bit two-step quantizer | 35 |

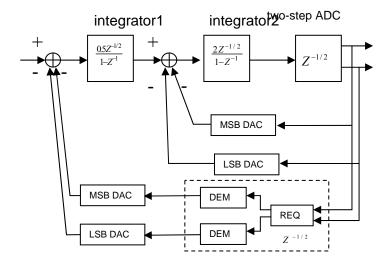

| Figure 3.6  | Example 2nd-order sigma-delta modulator with two-step quantizer                                                                  | .36 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------|-----|

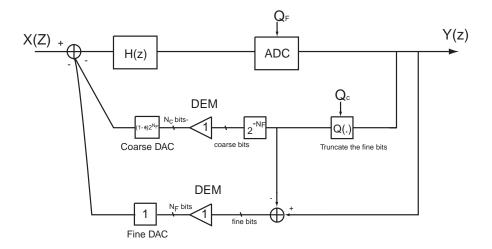

| Figure 3.7  | Block diagram of $\Sigma\Delta$ ADC with the segmented DAC                                                                       | 36  |

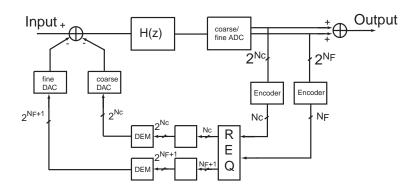

| Figure 3.8  | Block diagram of $\Sigma\Delta$ ADC with a first-order requantization block                                                      | 39  |

| Figure 3.9  | Expanded View of REQ Block                                                                                                       | 39  |

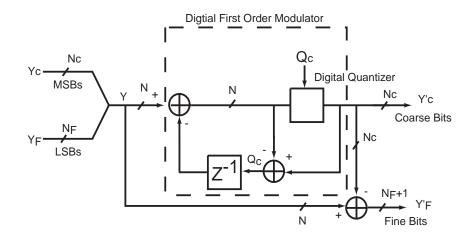

| Figure 3.10 | The signal flow graph of a $\Sigma\Delta$ ADC with a first-order requantization block                                            | 41  |

| Figure 3.11 | The signal flow graph of a $\Sigma\Delta$ ADC with a second-order requantization block                                           | 41  |

| Figure 3.12 | The simulated spectrums with different REQ orders in a second-order $\Sigma\Delta$ modulator with 4+4 bit two-step quantization. | 43  |

| Figure 3.13 | The simulated system SNR versus oversampling ratio under different REQ orders                                                    | 44  |

| Figure 4.1  | Block diagram of the system                                                                                                      | .49 |

| Figure 4.2  | Linear model of the systems. (a) proposed system (b) proposed system without two feed forward paths                              | 51  |

| Figure 4.3  | System SNR versus the dc gain of opamp                                                                                           | 54  |

| Figure 4.4  | System SNR versus gain error of the integrators                                                                                  | 57  |

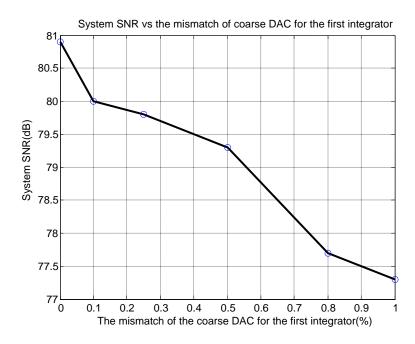

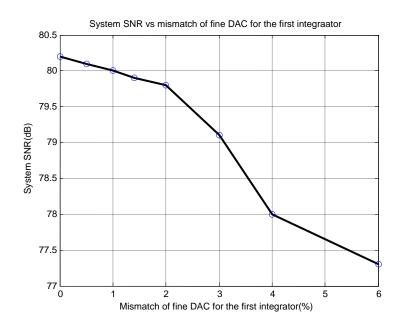

| Figure 4.5  | System SNR vs mismatch of coarse DAC for the first integrator                                                                    | 59  |

| Figure 4.6  | System SNR vs mismatch of fine DAC for the first integrator                                                                      | 59  |

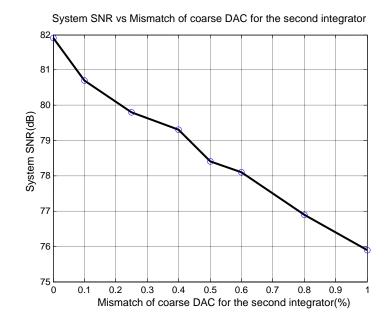

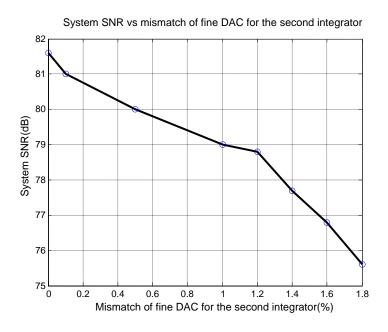

| Figure 4.7  | System SNR vs mismatch of coarse DAC for the second integrator                                                                   | 61  |

| Figure 4.8  | System SNR vs mismatch of coarse DAC for the second integrator                                                                   | 61  |

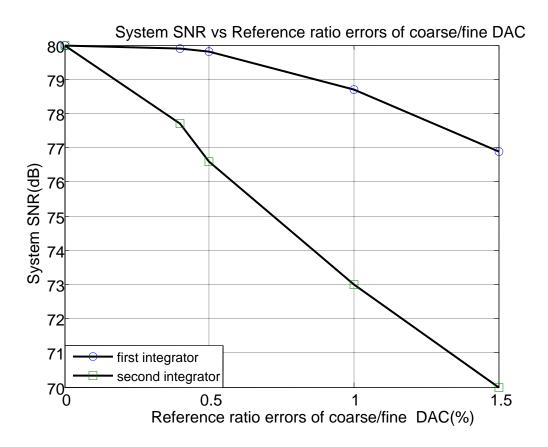

| Figure 4.9  | System SNR vs Reference ratio errors of coarse/fine DAC                                                                          | 62  |

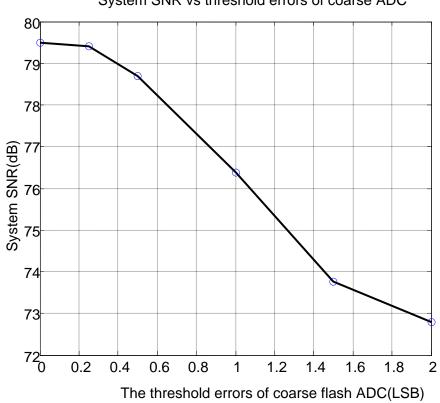

| Figure 4.10 | System SNR vs Offset Error of Coarse ADC                                                                                         | 63  |

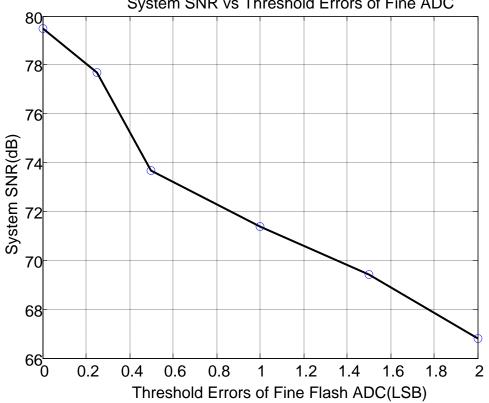

| Figure 4.11 | System SNR vs Threshold Errors of fine ADC                                                                                       | 65  |

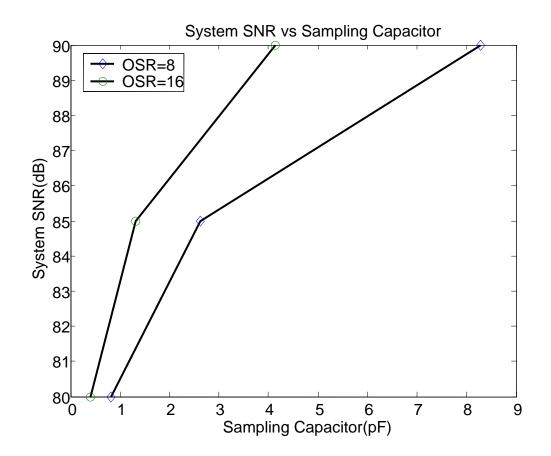

| Figure 4.12 | System SNR vs the sampling capacitor of the first integrator                                                                     | 67  |

| Figure 5.1  | The block diagram of the two-step ADC                                                                                            | .71 |

| Figure 5.2  | The block diagram of the flash ADC                                                                                               | .73 |

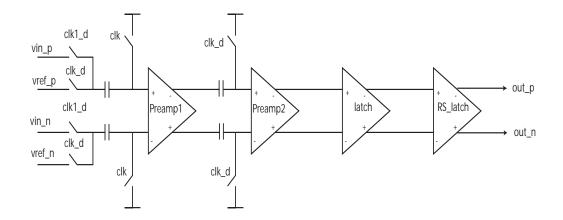

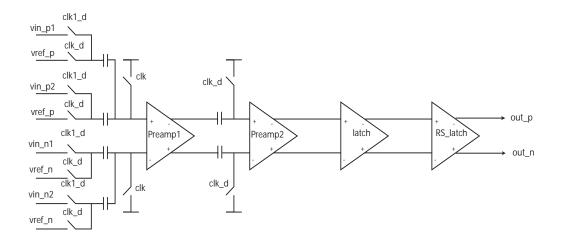

| Figure 5.3  | The block diagram of the comparator                                                                             | 75   |

|-------------|-----------------------------------------------------------------------------------------------------------------|------|

| Figure 5.4  | Block diagram of the new type comparator with short-delay adder                                                 | 78   |

| U           | The schematics of the two preamplifiers. (a) and (b) are the schematic of the preamp1 and preamp2 respectively. | 79   |

| Figure 5.6  | The post-layout simulation of the two preamplifiers                                                             | 80   |

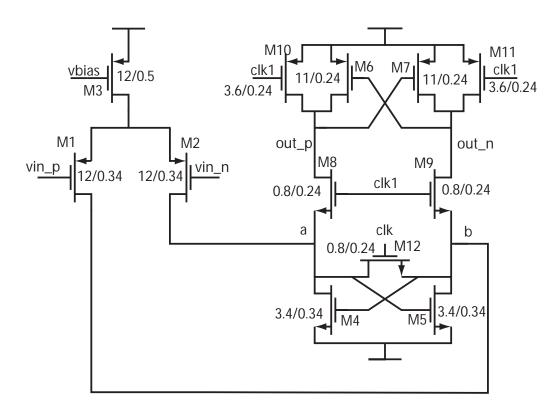

| Figure 5.7  | The schematic of the latch                                                                                      | 82   |

| Figure 5.8  | The block diagram of a simple single-ended subtractor                                                           | 85   |

| Figure 5.9  | The schemtic of the subtractor/DAC                                                                              | 88   |

| Figure 5.10 | Block diagram of an integrator/DAC                                                                              | 90   |

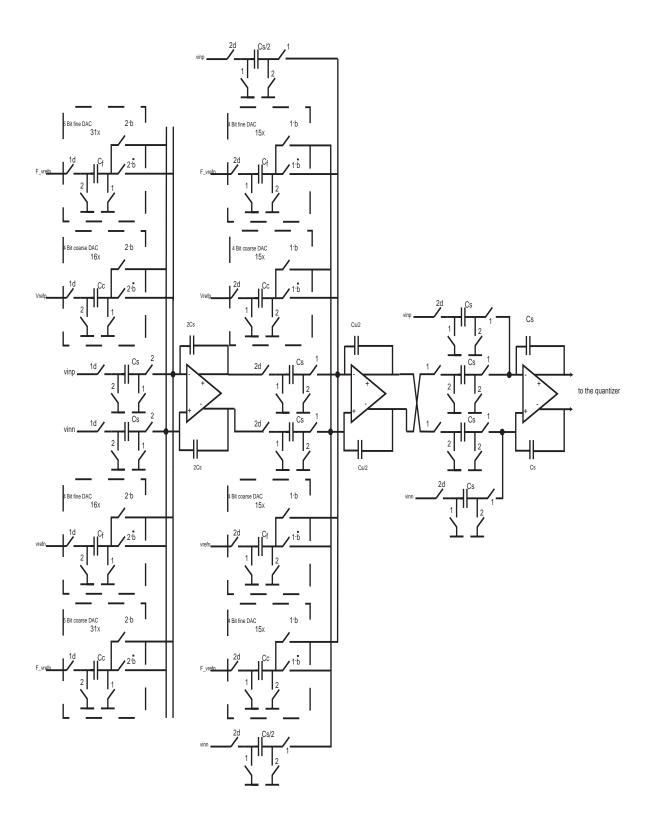

| Figure 5.11 | Block diagram of the adder                                                                                      | 93   |

| Figure 5.12 | Overall timing diagram of the system                                                                            | 95   |

| Figure 5.13 | Block diagram of two integrators and adder                                                                      | 96   |

| Figure 5.14 | The schematic of telescopic opamp                                                                               | 97   |

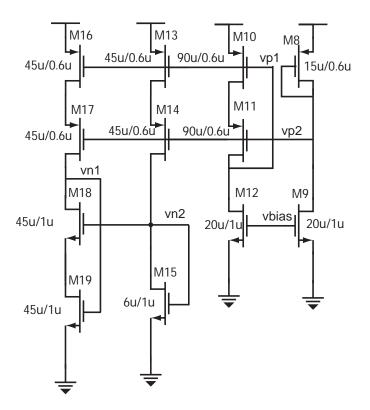

| Figure 5.15 | The schematic of bias circuit for the telescopic opamp                                                          | 100  |

| Figure 5.16 | The schematic of the folded-cascode opamp                                                                       | 102  |

| Figure 5.17 | The bias-circuit of the folded-cascode opamp                                                                    | 103  |

| Figure 5.18 | The schematic of the common-mode feedback circuit                                                               | 105  |

| Figure 5.19 | Block diagram of the clock generator circuit                                                                    | 106  |

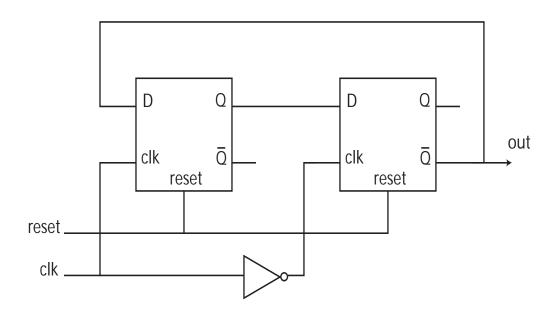

| Figure 5.20 | Block diagram of the waveform converter circuit                                                                 | 107  |

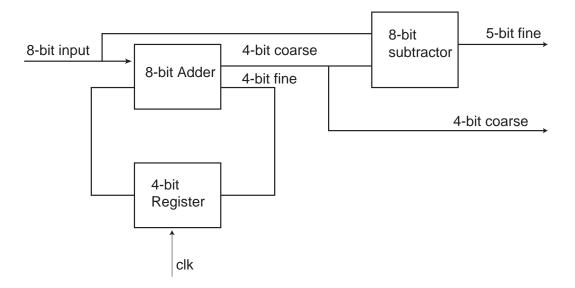

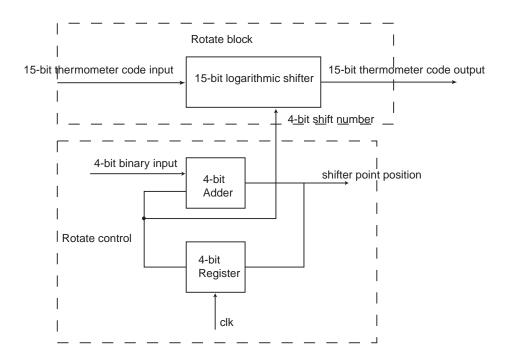

| Figure 5.21 | Block diagram of the digital circuit                                                                            | 108  |

| Figure 5.22 | Block diagram of REQ circuit                                                                                    | 109  |

| Figure 5.23 | Block diagram of 8-bit ripple adder                                                                             | .109 |

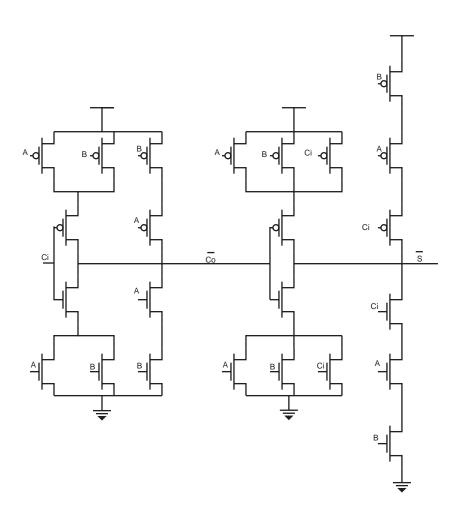

| Figure 5.24 | Schematic of one-bit fully adder                                                                                | 110  |

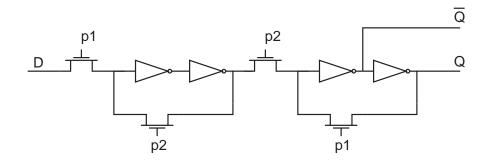

| Figure 5.25 | Schematic of D-register                                                                                         | 111  |

| Figure 5.26 | Block diagram of the DEM circuit                                                                                | .111 |

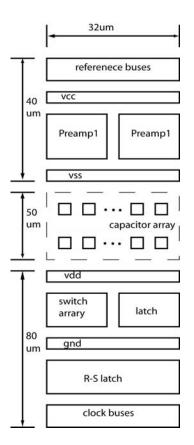

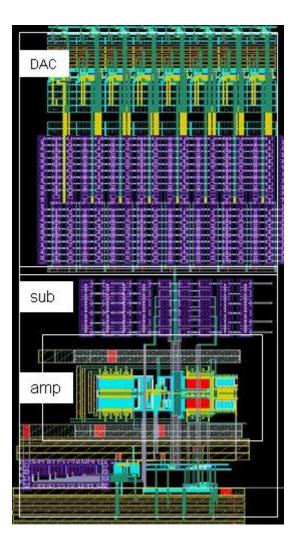

| Figure 5.27 | Floor-plan of the chip                                                                                          | .113 |

| Figure 5.28 | The diagram of the layout design of the comparator           | .114 |

|-------------|--------------------------------------------------------------|------|

| Figure 5.29 | The layout of the Subtractor/DAC                             | .115 |

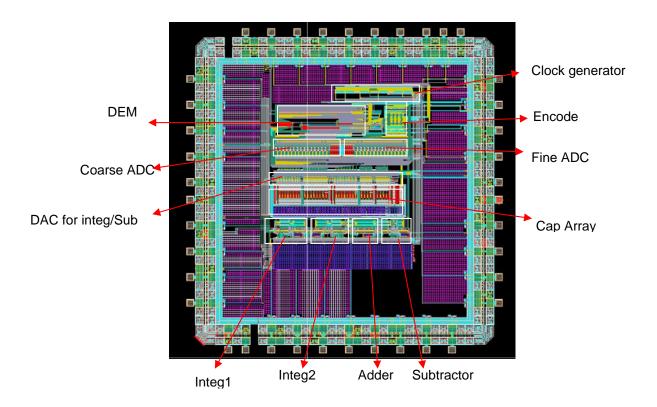

| Figure 5.30 | The layout of the whole chip                                 | .116 |

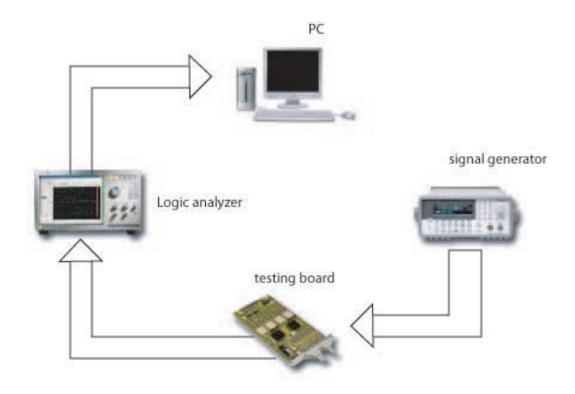

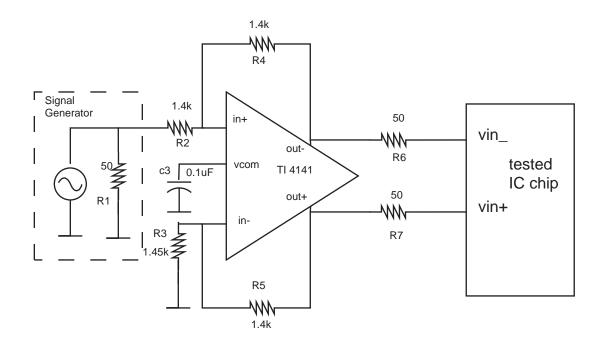

| Figure 6.1  | Measurement configuration                                    | .118 |

| Figure 6.2  | Schematic of the differential inputs generator               | .119 |

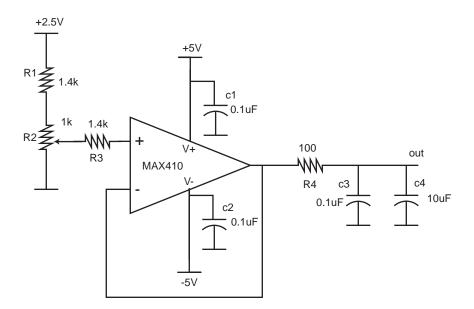

| Figure 6.3  | Schematic of the voltage buffer                              | .120 |

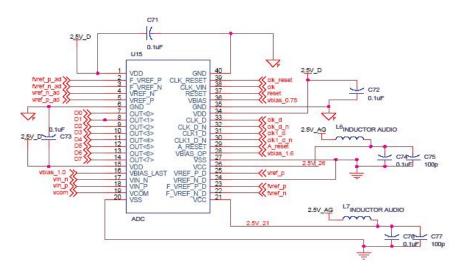

| Figure 6.4  | Part of the testing board                                    | .122 |

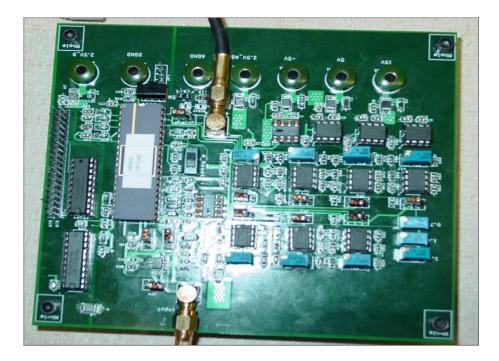

| Figure 6.5  | The picture of the testing board                             | .123 |

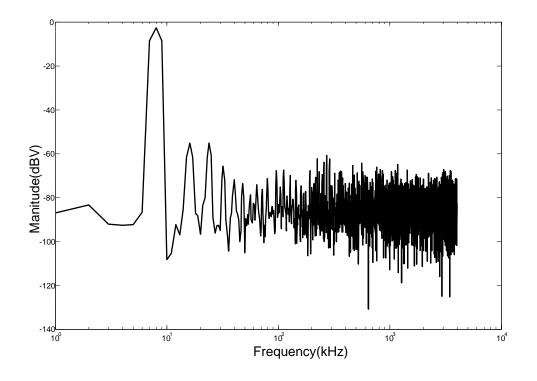

| Figure 6.6  | The power spectrum of the two-step 8-bit inner quantizer     | .124 |

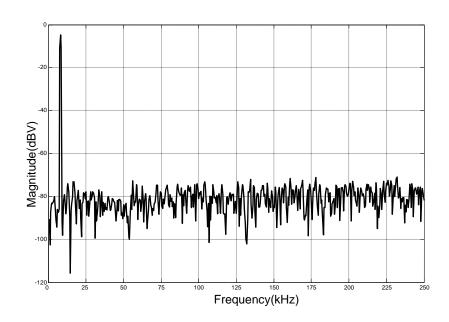

| Figure 6.7  | The output spectrum without digital requantization algorithm | .125 |

| Figure 6.8  | The output spectrum with digital requantization algorithm    | .125 |

## **1** Introduction

Data converters including analog-to-digital converters (ADC) and digital-toanalog converters (DAC) are the essential link between the real analog world and the digital world [1]. ADCs convert the analog signal to a digital counterpart, which is then processed in the digital domain while DACs convert the digital codes back into the analog signals. Data converters are always in demand with the rapid development of computing and digital signal processing. For example, electronic devices such as compact disc players, digital cameras, telephones, modems, and high-definition television (HDTV) require a high resolution and/or high speed converter to interface to the analog world [2,3].

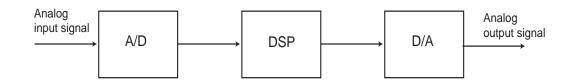

Figure 1.1 Typical Digital Signal Processing System

Figure 1.1 shows a simple block diagram of a typical signal processing system. To take advantage of the powerful digital signal processors (DSP), all input analog signals are digitalized using ADCs. After converting to digital signals, the output of the ADC is then processed by DSP and finally converted back to analog signals through DACs.

There are two main types of ADCs, Nyquist-rate converters and oversampling converters [4]. Nyquist-rate converters are used in high-speed applications, such as video and radar signal processing, as they generate a series of output values in which each value has a one-to-one correspondence with a signal input value. However, the precision of analog components in current semiconductor processes limits the resolution of Nyquist-rate converters. Oversampling converters, on the other hand, find application in lower or medium speed applications such as digital audio and asymmetrical digital subscriber line(ADSL), as they convert a large number of analog input signal samples to their corresponding digital representations. As a result of taking more input signal samples, the oversamped converters can achieve high-resolution without using high precision analog components, making them easier to implement in modern submicron processes.

This thesis is concerned with a practical realization of an oversampled A/D converter. Section 1.1 discusses the Nyquist-rate converters while Section 1.2 is concerned with oversampled converters. Finally, an overview of this thesis is in Section 1.3.

### 1.1 Nyquist-rate ADC

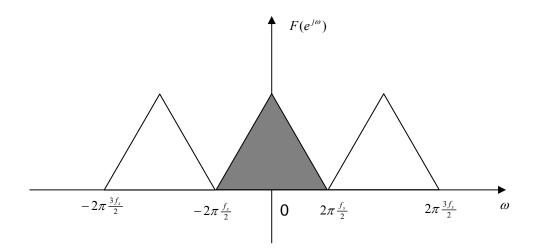

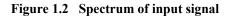

Nyquist-rate ADCs sample the analog input signal at the Nyquist-rate  $f_s=2f_b$ , where  $f_b$  is the highest frequency component of the input signal. If the input signal is not bandlimited, an anti-aliasing filter must be used before the converter to prevent aliasing. Figure 1.2 shows the spectrum of the sampled input signal. A typical frequency response of the anti-aliasing filter is shown in Figure 1.3. To ensure that the filtered signal does not contain any frequency components above  $f_s/2$  [5], the anti-aliasing filter must have a very narrow transition band, which is not easy to realize.

Figure 1.3 Anti-aliasing filter for nyquist-rate ADC

In the Nyquist-rate ADC, the relationship between input voltage ( $V_{in}$ ), the reference voltage ( $V_{ref}$ ) and the digitized results ( $b_0 - b_N$ ) can be represented by

$$V_{ref}(b_1 2^{-1} + b_2 2^{-2} + \dots + b_n 2^{-N}) = V_{in} + E_q$$

(1.1)

and the range of  $E_q$ , the quantization error caused by the converter is

$$-\frac{1}{2}V_{LSB} \le E_q < \frac{1}{2}V_{LSB} \tag{1.2}$$

where  $V_{LSB}$  is defined to be

$$V_{LSB} = \frac{V_{ref}}{2^N}.$$

(1.3)

Since there is a range of valid input values that produce the same digital output code, this signal ambiguity causes the quantization error,  $E_q$  for all A/D converters even ideal converters.

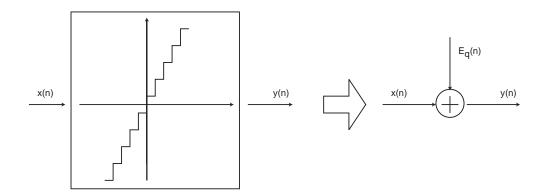

Equation (1.2) shows that the difference between the input signal and the output signal is only the quantization noise  $E_q$ . So a linear model with a simple additive noise source shown in Fig. 1.4 can be used to model the converter.

Figure 1.4 Linear model of the nyquist-rate ADC.

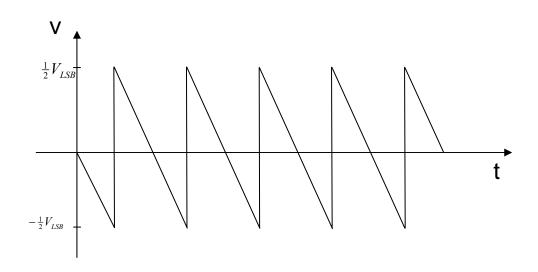

To gain an understanding of the properties of the quantization noise signal,  $E_q$ , a ramp signal from 0 to  $V_{ref}$  is assumed to be the input of the converter. Figure 1.5 is the sawtooth waveform of the quantization noise,  $E_q$ . Note that the quantization error,  $E_q$  is limited to LSB/2 and –LSB/2 and its average value is zero.

Figure 1.5 Sawtooth waveform of the quantization noise

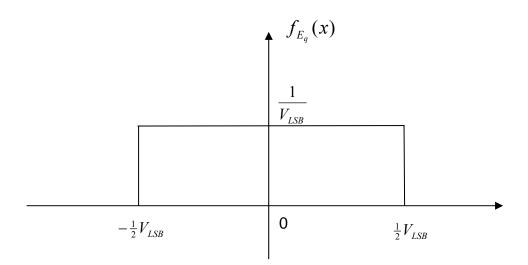

For an arbitrary input to the converter, the quantization noise will not have a sawtooth waveform. However, we can assume that the input signal changes rapidly such that the quantization error,  $E_q$ , is a random variable uniformly distributed between  $-\frac{1}{2}V_{LSB}$  and  $-\frac{1}{2}V_{LSB}$  [4]. So the probability density function for such signal will be a constant value, as shown in Figure 1.6.

The power of the quantization noise error can be found as

$$P_E = \int_{-\infty}^{\infty} x^2 f(x) dx = \frac{1}{V_{LSB}} \int_{-V_{LSB}/2}^{V_{LSB}/2} x^2 dx = \frac{V_{LSB}^2}{12}.$$

(1.4)

The above suggests that given an input signal waveform, a formula can be derived to get the best possible signal-to-noise ratio (SNR) for a given number of bits in an ideal ADC.

Figure 1.6 Assumed probability density function for the quantization error Eq

Because most ADC are tested by inputting a pure sinusoidal signal, a common SNR formula of the converters with a sinusoidal input can be derived as

$$SNR = 10\log\frac{P_s}{P_E} = 10\log\frac{V_{ref}^2/2}{V_{LSB}^2/12} = 10\log\left(\frac{3}{2}2^{2N}\right) = 6.02N + 1.76.$$

(1.5)

Equation (1.5) reveals that each additional bit increases the SNR of the converter by 6 dB. Thus for a Nyquist rate converter to achieve a SNR of 98 dB(or 16bits) requires a 16-bit quantizer. This requirement is beyond the practical achievable accuracy for untrimmed monolithic circuits, since matching of one part in 65535 (0.0015%) element matching is required. As will be demonstrated, the methods employed in sigma-delta modulation allow much higher SNRs to be achieved without high precision element matching.

### **1.2** Oversampled Converters

The previous section outlines the basic relationships between the number of bits of the converter and SNR for the Nyquist-rate converters. Although increasing the converter bits can reduce the power of the quantization error, the implementation imperfections such as component mismatches limit the SNR of Nyquist-rate converters.

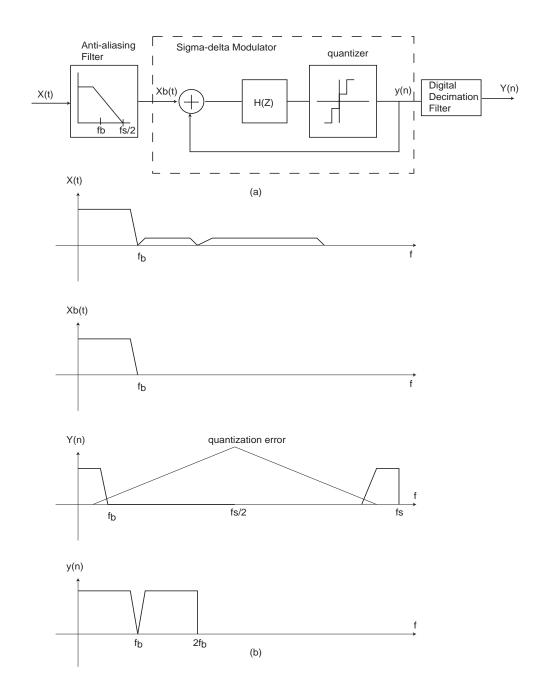

To achieve high-resolution without requiring high precision analog components, oversampling techniques are often used. This relies on three techniques: oversampling of the input signal, quantization error shaping and digital filtering. The general topology of a sigma-delta ADC is shown in Figure 1.7. The core circuit of the ADC is a sigma-delta modulator, which acts as a high pass filter to filter the quantization error in the signal bandwidth. Because of the oversampling that makes the signal bandwidth much smaller than half of the sampling frequency, a digital decimation filter can be used to downsample and filter the modulated signal to the Nyquist bandwidth. A summary of the signal spectrum inside the sigma-delta ADC showing the spectrum change after anti-aliasing filtering, noise shaping, and digital filtering is also in Figure 1.7.

That the anti-aliasing filter in Figure 1.7 has a much wider transition band than that of Nyquist-rate converters in Figure 1.3 because the sampling frequency in the oversampled converters is much higher than the input signal bandwidth. Thus the design of the anti-aliasing filter for the oversampled converters becomes much easier.

Figure 1.7 Sigma-delta ADC overview (a) block diagram (b) spectrum content

Even without noise shaping, oversampling can also help to increase the resolution of the ADC because it spreads the power of the quantization error over the sampling bandwidth. To see the effect of oversampling on the SNR, we first define the oversampling ratio, OSR, as

$$OSR = \frac{f_s / 2}{f_b} = \frac{f_s}{2f_b}$$

(1.6)

where  $f_s$  is the sampling frequency and  $f_b$  is the highest signal frequency. Because the quantization error is equally distributed over the sampling bandwidth without the noise shaping, an oversampling ratio of M means that the power of the quantization error in the signal band width is reduced by M. Thus the SNR of the ADC will increase M times and can be expressed as

$$SNR = 10 \log\left(\frac{3}{2} 2^{2N} OSR\right) = 10 \log(OSR) + 6.02N + 1.76.$$

(1.7)

The above equation shows that 1-bit improvement in SNR requires a factor of four increase in OSR. To improve SNR by 4 bits, the OSR needs to be 256. This exponential relationship quickly reaches a practical implementation limit due to the speed of the quantizer. So the improvement of ADC resolution simply by increasing the oversampling alone is somewhat limited.

Further improvement in the resolution of the oversampled converter can be obtained using the sigma-delta modulator of Figure 1.7 so that the majority of the quantization error is moved out of the signal bandwidth. To characterize the performance of the sigma-delta modulator, both signal and noise transfer functions are developed.

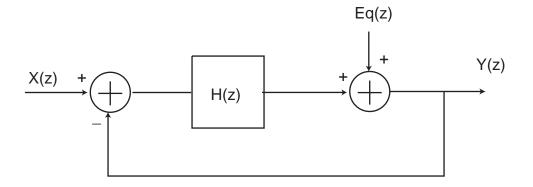

The basic transfer function for the sigma-delta modulator can be easily developed using the linear model in Figure 1.8 where the quantizer error is modeled as an additive noise source similar to that shown in Fig. 1.4 and H(z) is the transfer function of the integrator. The feedback modulator is a linear, time-invariant system allowing superposition for analysis of the input signal transfer function and the quantization noise transfer function.

Figure 1.8 Signal Flow of the Sigma-Delta modulator

Assuming that the quantization noise is zero, the output signal, Y(z) can be determined as

$$(X(z) - Y(z))H(z) = Y(z).$$

(1.8)

Simplifying 1.8 leads to the signal transfer function that is

$$S_{TF}(z) = \frac{Y(z)}{X(z)} = \frac{H(z)}{1 + H(z)}.$$

(1.9)

By assuming that the input signal is zero, in the same way, one can get the noise transfer function that is

$$N_{TF}(z) = \frac{Y(z)}{E_q(z)} = \frac{E_q(z)}{1 + H(z)}.$$

(1.10)

Using superposition, the system output is the combination of the signal and noise transfer function, which can be written as

$$Y(z) = S_{TF}(z)X(z) + N_{TF}(z)E_q(z) = \frac{H(z)X(z) + E_q(z)}{1 + H(z)}.$$

(1.11)

For first-order noise shaping when  $H(z) = z^{-1}/(1-z^{-1})$ , the modulator output is

$$Y(z) = z^{-1}X(z) + (1 - z^{-1})E_q(z).$$

(1.12)

We can see that the signal transfer function is simply a delay, while the noise transfer function is a discrete-time differentiator. An analysis of the first-order sigmadelta modulator reveals that the quantization noise is given by [2]

$$P_{E} = \left(\frac{V_{LSB}^{2}}{12}\right) \left(\frac{\pi^{2}}{3}\right) \left(\frac{2f_{0}}{f_{s}}\right)^{3} = \frac{V_{LSB}^{2}\pi^{2}}{36} \left(\frac{1}{OSR}\right)^{3}.$$

(1.13)

So the SNR of the sigma-delta ADC with first order noise shaping is

$$SNR = 10 \log\left(\frac{P_s}{P_E}\right) = 10 \log\left(\frac{3}{2}2^{2N}\right) + 10 \log\left(\frac{3}{\pi^2}(OSR)^3\right).$$

(1.14)

From the above equation, one can find that doubling the OSR gives an SNR improvement for a first-order modulator of 9 dB. However, for the system without noise shaping, the SNR improvement is only 3 dB.

The SNR expression for the oversampling sigma-delta A/D converter reveals a high resolution A/D converter can be obtained by oversampling the input signal and is not limited by the precision of the analog components.

### **1.3 Research Contributions**

Several original contributions are made and documented in this dissertation to allow the inner quantization with a large number of bits in a single-stage  $\Sigma\Delta$  modulator. Additionally, an experimental prototype has been fabricated with the TSMC 0.25um mixed-signal process to verify the design of a single stage  $\Sigma\Delta$  modulator with 8-bit twostep inner quantization. This section gives a brief summary and a detailed description of the contributions that will appear in the corresponding chapters.

- 1. *Two-step quantization*. Two-step inner quantization using traditional, powerefficient switched-capacitor circuits has been developed in a single-stage mulibit  $\Sigma\Delta$  modulator by incorporating half-delay integrators, careful two-step ADC timing, and other architectural changes. The two-step quantization avoids the problem that the complexity of an internal flash ADC increases exponentially with each added bit. Because both the MSB and LSB signals produced by the two-step quantization are fed back simultaneously to all integrator stages, it is made suitable for low oversampling ratios. This part of research found in chapter 3 has been published in two conference papers [6,7].

- 2. Segmented architecture with coarse/fine DAC and DEM. A segmented architecture with coarse/fine Dynamic Element Matching (DEM) and DAC has been proposed to reduce the complexity of DEM and DAC due to the internal quantization with large number of bits. The consequence of the segmentation, mismatch between coarse and fine DACs can be noise-shaped by using a digital requantization (REQ) algorithm. A theoretic analysis of the REQ algorithm has been conducted to obtain the upper limit of the gain mismatch between coarse and fine DACs. Both behavior simulation and the circuit implementation demonstrated the effectiveness of the REQ algorithm. This part of research found in chapter 3 has been accepted in a journal paper [8].

- 3. A new architecture of the  $\Sigma \Delta$  modulator. A new architecture of the secondorder  $\Sigma \Delta$  modulator illustrated in chapter 4 has been developed. This architecture uses the 8-bit two-step ADC for the inner quantization, achieving high resolution with a very low oversampling ratio. Two feed-forward branches are used to reduce the output swing of the integrators, therefore greatly relaxing the requirement on the DC gain of the opamp inside the integrators. A theoretic analysis of the feed-forward branches was performed to find the best gain of the branches.

- 4. First reported ΣΔ modulator with 8-bit inner quantization. An experimental prototype with the implementation of a single-stage ΣΔ modulator with 8-bit inner quantization has been fabricated with the TSMC 0.25um mixed-signal process. Chapter 5 describes the VLSI implementation of this prototype chip. It is the first reported single-stage ΣΔ modulator with 8-bit inner quantization. The REQ algorithm implemented in the system helped to decrease the noise floor in the signal band by 20 dB. The measured system achieved the dynamic range of 70 dB with an oversampling ratio of 16.

- 5. A static adder circuit. A static circuit with only switches and capacitors was developed to realize a short delay adder before the inner quantization. By adding two extra capacitors to the frond-end of the fully differential comparators, the short delay adder becomes the integral part of the flash quantizer, which firstly adds two signals together and then quantizes their sum. The static circuit adder has less power and chip area than that

implemented with the switched-capacitor circuit. The details of this circuit can be found in chapter 5.

### **1.4 Dissertation Outline**

Conventionally, sigma-delta ADCs are used for low frequency applications due to the limit of the sampling frequency. One method of extending the signal bandwidth of a sigma-delta ADC is to appropriately trade internal quantization with oversampling ratio. This dissertation explores the possible benefits of applying the inner quantization with a large number of bits to a single stage sigma-delta modulator to reduce the oversampling ratio (OSR). Problems arising from this approach will be discussed in this dissertation. A prototype chip with 8-bit inner quantization was fabricated to demonstrate the performance of this approach. The dissertation is organized as follows.

In Chapter 2, the basics of the sigma-delta modulator are reviewed and several architectures are discussed along with their advantages and limitations.

In Chapter 3, the system architecture of a single-stage sigma-delta ADC with 8-bit two-step quantization is presented. Two problems encountered during the system design, the complexity of the quantizer and DACs are addressed and their respective solutions are presented.

In Chapter 4, the results of the behavior simulation are presented to determine the critical parameters of all sub-circuits of the system.

In Chapter 5, the detailed VLSI implementation of the system with the TSMC 0.25um mixed-signal process is presented with an emphasis on the switched-capacitor

14

integrator. The optimization of the circuit performance and the design of the digital circuit are also included.

In Chapter 6, the experimental prototype and the measurement results are presented along with the discussion of the key performance issues.

In Chapter 7, the contributions of the thesis are presented and further improvements of this project are proposed.

# 2 Sigma Delta ADC Fundamentals

The basic concept for the sigma-delta ADC is using the feedback to improve the effective resolution of a coarse inner quantizer. An early description of this concept was given in a patent by Culter [9]. His idea was to take a measurement of the quantization error in one sample and subtract it from the next input sample by using a delta modulator. Sigma-delta modulation employing noise shaping was proposed by Inose, Yasuda, and Murakami in 1962 [10] who added the loop filter to the frond end of a delta modulator and then move it inside the loop. Since the system contained a delta modulator and an integrator, it was named a delta-sigma modulator, where the "sigma" denoted the summation performed by the integrator. However, this technique was not widely used until the mid-1980s, because the use of a sigma-delta ADC required a digital decimation filter to digitally filter the high frequency noise, which was not realistic to build. With the development of VLSI technology, from mid-1980s, the sigma-delta converters have gradually become an area of great interest.

Based on the architecture, there are three types of sigma-delta modulators: singlestage modulators, cascade modulators and multibit modulators. Each type of modulator has both advantages and disadvantages. The following sections will provide an overview of these three types of modulators and compare their advantages and disadvantages.

## 2.1 Single Stage Modulators

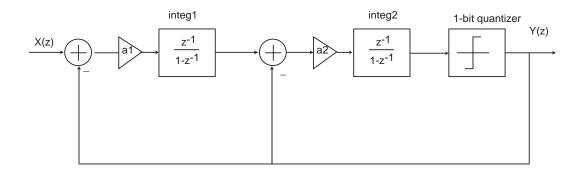

A single loop sigma-delta modulator is the most straightforward architecture. Like the example of the first-order sigma-delta modulator in chapter 1, more integrators can be added to the feed-forward path of the modulator to increase the noise shaping order. Figure 2.1 shows the diagram of a second-order single-stage sigma-delta modulator. Compared with the first-order modulator, it has two integrators in the feed forward paths, which integrate the difference between the feed forward signal and the feedback signal from the output.

Let the gains of two integrators: a1, a2 equal 0.5 and 2 respectively, the signal and noise transfer function of the second-order modulator are given by

$$STF(z) = z^{-2}$$

(2.1)

and

$$NTF(z) = (1 - z^{-1})^2.$$

(2.2)

The above equations show that the signal component at the output of the secondorder modulator is simply a two clock cycle delay of the input signal while the noise component gets the second-order noise shaping.

From the noise transfer function of equation (2.2), one can also obtain the expression of SNR for a second-order modulator. The magnitude of the noise transfer function can be shown to be

$$\left|N_{TF}(f)\right| = \left[2\sin\left(\frac{\pi f}{f_s}\right)\right]^2 \tag{2.3}$$

leading to a quantization noise power over the signal bandwidth of

$$P_{E} = \frac{V_{LSB}^{2} \pi^{4}}{60} \left(\frac{1}{OSR}\right)^{5}.$$

(2.4)

Again assuming the input of the converter is the full scale sinusoidal signal, the maximum SNR for the second-order modulator becomes

$$SNR = 10 \log\left(\frac{3}{2} 2^{2N}\right) + 10 \log\left[\frac{5}{\pi^4} (OSR)^5\right].$$

(2.5)

We see here that doubling the OSR improves the SNR for the second-order modulator by 15 dB while for the first-order modulator the improvement is only 9 dB.

Figure 2.1 Block diagram of a second-order single-stage sigma-delta modulator

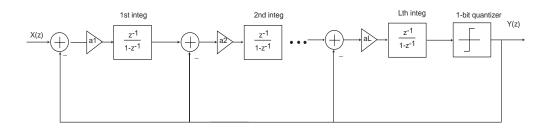

One can increase the modulator beyond second-order by including more integrators in the feed forward path as shown in Figure 2.2 where L integrators are used. Since the noise transfer function of an L-order modulator is

$$N_{TF}(z) = (1 - z^{-1})^{L}, \qquad (2.6)$$

in the same way, one can get the maximum SNR for the L-th order modulator, which can be written as

$$SNR = 10 \log\left(\frac{3}{2} 2^{2N}\right) + 10 \log\left[\frac{(2L+1)}{\pi^{2L}} (OSR)^{2L+1}\right].$$

(2.7)

Figure 2.2 Block diagram of an Lth-order single-stage sigma-delta modulator

Although, it is convenient to use a high-order modulator to achieve high-order noise shaping, the high order (order >2) single-stage modulator has a problem in that the system becomes unstable due to the overload of the quantizer caused by the high gain of the noise transfer function. There are several different approaches to solve the problem of the instability while maintaining high-order noise shaping.

One approach to obtain a stable high-order single loop modulator is to scale down the gain coefficient of each integrator stage so that the highest gain of the noise transfer function can be controlled below 2 [11-14]. When the integrator gain is down-scaled, the modulator noise shaping is degraded from the standard shape form of  $(1 - z^{-1})^L$ . As a result, a bigger OSR is needed to get the SNR predicted by equation (2.7). A systematic analysis of the tradeoff between the performance and integrator coefficients can be found in [3].

The other two approaches are either using cascade architecture or applying the multi-bit inner quantization to get the high-order noise shaping, which will be discussed in the following section.

## 2.2 Cascade Modulators

In cascade modulators, the combination of a first-order or second-order sigmadelta modulator is used to obtain higher-order noise shaping. Because each stage only has a 1<sup>st</sup> or 2<sup>nd</sup> order noise shaping, the whole system has no instability problem.

The quantization noise from each stage is fed as input into the following stage and the output of each stage is digitally filtered and a single output is obtained as the sum of the filter outputs. Proper selection of the filter stages results in cancellation of the quantization noise of each stage except the last. The final stage quantization noise is shaped to the order of the overall modulator, which is the sum of the order of every stage.

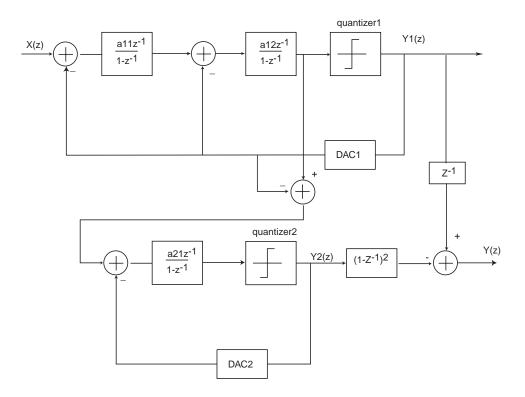

Figure 2.3 shows an example of cascade architecture, where a second-order modulator is followed by a first-order modulator. The quantization error of the first modulator stage is fed to the input of a second modulator. The signal transfer function and noise transfer function of the two modulators can be respectively written as:

$$Yl(z) = z^{-2}X(z) + (1 - z^{-1})^{2}Ql(z)$$

(2.8)

and

$$Y2(z) = z^{-1}Ql(z) + (1 - z^{-1})Q2(z).$$

(2.9)

The digital outputs of two sigma-delta modulator stages, Y1(z) and Y2(z) are then processed with one clock cycle delay unit and second order differentiator unit respectively and finally pass through a subtractor to form the output of the system Y(z). This output can be calculated as

$$Y(z) = z^{-1}Y1(z) - (1 - z^{-1})^2 Y2(z) = z^{-3}X(z) - (1 - z^{-1})^3 Q2(z).$$

(2.10)

Equation (2.10) indicates that a third-order noise shaping can be obtained by combining a second-order and a first-order modulator in cascade. Since no single stage is greater than  $2^{nd}$  order, the whole system achieving  $3^{rd}$  order noise shaping is stable.

This cascade approach can be extended to a higher-order simply by adding more first-order or second-order stages. For example, fourth-order noise shaping can be obtained by using two second-order stages (2-2 architecture).

Besides achieving high-order noise shaping without the problem of instability, the cascade architecture has another advantage over its single stage counterparts. For most single-stage modulator, the inner quantization is only 1-bit due to the nonlinearity of multibit DAC, which will be discussed in the next section. However, in cascade modulators, the multibit quantizer and DAC can be used in the last stage to increase the system resolution because the nonlinear errors of DACs are shaped by the sigma-delta modulator in the previous stage [16-19]. An example of a cascade modulator with multibit quantizer can be found in [20].

Figure 2.3 Block diagram of a third-order modulator in a cascade architecture

In cascade architecture, the limit on the increase of the noise shaping order is set by matching requirements. If the gains between the analog and digital paths do not match, the quantization noise in different single loops can not be cancelled effectively, and the quantization noise will leak through to the modulator output. As the order of the noise shaping in the cascade is increased, the constraints on this mismatch become more severe.

## 2.3 Multibit Modulators

One-bit noise shaping modulators have achieved popularity for use in integrated circuit data converters largely due to the fact that they employ 1-bit internal DAC that does not require precision component matching. However, as shown in equation 2.1, the resolution that a 1-bit sigma-delta modulator can achieve at a given oversampling ratio is limited. Although the achievable resolution increases with increasing single-stage order, these improvements rapidly diminish because of the problem of instability.

The primary advantage of multibit modulators is that the power of the quantization noise decreases dramatically and the SNR increases by 6 dB for each additional bit. Therefore, we can increase the overall resolution of any oversampled data converter without increasing the oversampling ratio, simply by increasing the number of levels in the internal data converters. This performance improvement in reducing the oversampling ratio while maintaining the resolution can be a significant advantage in high speed and high resolution application. The use of the multibit inner quantizers also facilitates the design of high-order single-stage modulators because the multibit quantizer is less likely to be overloaded than a 1-bit quantizer.

A big disadvantage of multibit modulators is that the multibit DAC inside the feedback path loses the excellent linearity as found in the one-bit DAC. Since the linearity of an oversampling converter is no better than the linearity of the DAC, the undesirable nonlinearity of the DAC directly limits the performance of the system [21, 22]. As the smallest component mismatch that can be achieved is on the order of 0.1-0.5% in an inexpensive CMOS IC fabrication process, the harmonic created by multibit modulators can approach -60 dB relative to the full-scale fundamental.

To deal with the nonlinarity problem of a multibit DAC, several circuit techniques from electronic trimming to digital corrections have been proposed. Because the digital correction technique called dynamic element matching (DEM) is the most popular method, the following section will focus on the introduction of the DEM method.

DEM is designed to convert a DC error into a wide-bandwidth noise by choosing different elements to represent a digital input code K at different times. In short, the DEM technique does not eliminate errors but spreads the power of errors over a widebandwidth. Four possible approaches are listed below to implement the DEM technique.

- Random Dynamic Averaging (RDA)

- Data Weighted Averaging (DWA)

- Individual Level Averaging (ILA)

- Clock Level Averaging (CLA)

For practical purposes, ILA and DWA are performed for the matching of the DAC. Figure 2.4 shows an example where DEM is used in the system. Before the feedback signal is fed to the DAC, the DEM block controls the elements to be chosen for the DAC operation.

Figure 2.4 A multibit sigma-delta modulator with dynamic element matching(DEM)

The goal of the individual level averaging algorithm is to improve the SNR in the signal band while avoiding the generation of tones. The basic idea of individual level averaging is to guarantee that each element is used with equal probability for each digital input code [23, 24]. In order to use this algorithm, each output level has its own pointer to remember the position of the last elements. For a certain digital input code, the ILA block first finds the pointer for the input. Once the pointer is known, the Rotation block will select a certain number of elements starting from the pointer. For example, a 4-bit DAC has 15 elements. If the input code is 4, the ILA block first finds a pointer associated with the input code 4. If that pointer is 2, the rotation block then selects the elements numbered from 3 to 7 and updates the pointer from 2 to 6. Figure 2.5 shows the diagram of the ILA block. In summary, the ILA algorithm decides which elements are used for a specific digital code each time in such way that each element is equally used no matter what the input code is.

Figure 2.5 Block diagram of the individual level averaging (ILA) block

Although the ILA can remove most harmonics of the DAC nonlinearity and spread out the noise widely in the Nyquist band, it increases the design complexity in the digital circuit due to the needs of storing the pointers for all the different quantization levels. The data weighted averaging (DWA) method, in contrast is much simpler than ILA only requiring one pointer for all the quantization levels.

Unlike ILA, DWA modulates the nonlinearity error around the subharmoinics of the sampling clock frequency by making the mismatch noise a periodic signal instead of making the mismatch noise white [25, 26, 27]. This method keeps track of the last element used in the previous code, and uses the next group of elements sequentially. Figure 2.6 demonstrates how the DWA algorithm works in a 4-bit DAC with fifteen unit elements. For the first input code of "2", the algorithm chooses the first two unit elements if the initial pointer position is 0. Then it would choose the elements from 3 to 5 and elements from 6 to 10 for two consecutive input codes, "3" and "5". Finally it would choose the last five elements and the first element for last input code of "6". The pointer in the DWA block always points to the position of the last elements used in the previous code.

Although the DWA method can not remove the harmonic distortion of the DAC as well as the ILA method, it modulates the nonlinarity of the DAC, moving the harmonic distortion out of the signal bandwidth, which can be removed by the digital filter in the following stage.

Figure 2.6 Graphical Explanation of DEM Operation

The block diagram of the DWA method can be found in Figure 2.7 where the binary input signal controls the update of the pointer while the thermometer code of the input determine which elements are chosen based on the position of the pointer. Instead of having pointers for every quantization level as illustrated in the ILA block, the DWA block only has one pointer updated with the input digital code, thus greatly reducing the complexity of the digital circuit.

### 2.4 Conclusion

The tradeoffs involved in achieving high resolution in sigma-delta ADCs usually lead to low internal quantization levels and high oversampling rates. However, in order to achieve both high resolution and high speed, the oversampling ratio (OSR) must be reduced, which requires an increase in the noise shaping order or the inner quantization levels.

Figure 2.7 Block diagram of the data weighted averaging (DWA) method

New DEM algorithms make it possible to use multibit inner quantization inside the single-stage sigma-delta modulator in spite of the nonlinearity of the analog DAC. However, there is a limit on increasing the quantization levels of the multibit sigma-delta modulator. The limit is imposed by the exponential increase of the complexity of the DAC, DEM, and inner quantizer with each additional bit of internal quantization. To further push the limit of the quantization bits of the inner quantizer, the next chapter will discuss a new system architecture, which solves the problem of the exponential increase in the complexity.

# **3** Inner Quantization with Large Number of Bits

#### 3.1 Introduction

The multibit delta-sigma modulator has become a popular architecture for implementing high-resolution ADCs for digital communications [28][29]. Due to the introduction of efficient dynamic element matching (DEM) techniques [23], single-stage multibit modulators have also gained interest. They offer a potentially low-power solution because of their relative insensitivity to integrator inaccuracies.

Most single-stage multibit modulators use a low number of bits (six or less) for internal quantization [28,30]. Each additional quantizer bit improves overall SNR by 6 dB and also improves modulator stability, which permits more aggressive noise shaping. However, power dissipation quickly becomes unmanageable because of the exponential increase in complexity of the internal flash ADC, the DEM circuitry, and the capacitive DACs. Figure 3.1 shows the schematic of a flash ADC in which 2<sup>N</sup>-1 comparators are needed to distinguish 2<sup>N</sup> quantization levels. So for the 8-bit flash ADC, the total number of the comparators is 255.

The two-step flash quantizer architecture can potentially solve this problem, but the latency of a two-step system normally causes modulator instability. Some attempts at solving this problem have been made, but with limited success. Lindfors [46] proposes an architecture with two-step quantization in which the coarse quantization noise can be removed by using digital noise cancellation. Another attempt at internal multi-step quantization is proposed in [30]. However, both methods need digital filtering and recombination to cancel coarse ADC quantization noise, which again are subject to noise leakage and the nonidealities of analog circuits.

Figure 3.1 Block diagram of the flash ADC

To solve this problem, new single-stage modulator architecture with two-step quantization is described. The effectiveness of the two-step quantization is not restricted by quantization noise leakage. A segmented DEM/DAC system with digital requantization is proposed to accommodate the high level of quantization achieved with two-step coarse/fine quantizers. The mismatch between two segmented DACs can be filtered by using a noise-shaped requantization.

#### 3.2 Two-step Quantization

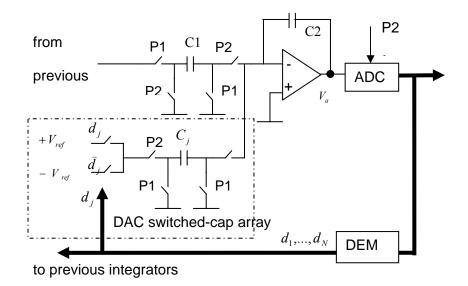

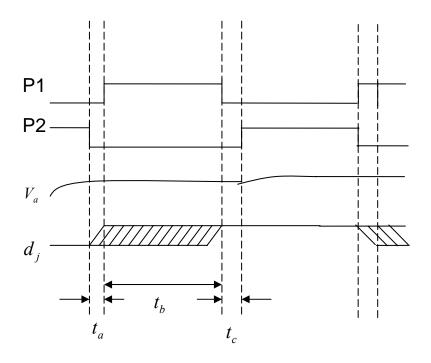

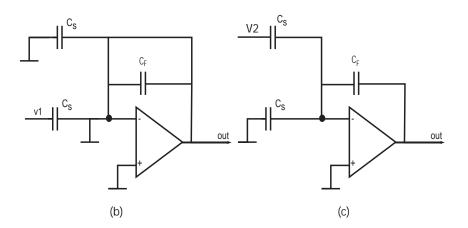

Performing two-step quantization within a single-stage modulator is challenging because only one-half clock cycle quantizer delay is permitted for stability reasons. Figure 3.2 shows a diagram of the quantizer (ADC block) and last integrator of a typical single-stage multibit sigma-delta ADC. The system is controlled by two non-overlapping clocks P1 and P2, shown in Figure 3.3. The parasitic-insensitive integrator of Figure 3.2 samples the input when P1 is high and updates its output ( $V_a$  of Figs. 3.1 and 3.2) when P2 is high. Figure 3.3 shows the total processing time,  $t_a + t_b + t_c$ , allowed for both quantizer and dynamic element matching (DEM) block.  $t_b$  corresponds to the pulse width of the clock P1, while  $t_a$  and  $t_c$  represent the "dead zones," when both P1 and P2 are low. DEM outputs  $d_j$  must assume their logical values before the next integration phase, or before the end of time  $t_c$ . With little more than half a clock cycle to accomplish A/D conversion and DEM, it appears that only a flash quantizer can be used in the traditional multibit modulator architecture.

The proposed architecture permits two-step A/D conversion by employing the following two techniques. First, the conversion time of a two-step quantizer is

compressed by utilizing the dead zone between the two non-overlapping clocks. Second, half-delay integrator stages are used to permit additional delay in the feedback path to all integrators except the last.

Figure 3.2 Block diagram of the quantizer and last integrator in a typical single-stage multibit sigma-delta modulator

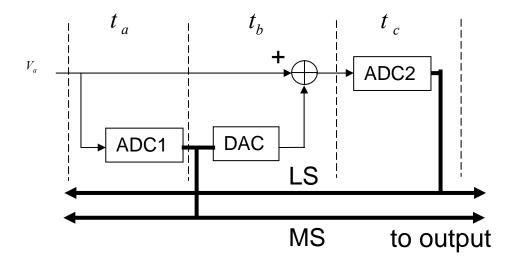

By using the special timing, the overall delay of a two-step quantizer can be compressed to half a clock cycle. Figure 3.4 shows a diagram of a two-step quantizer, where the two-step operations have been allocated to time slots  $t_a$ ,  $t_b$  and  $t_c$  corresponding to Figure 3.3. At the beginning of time  $t_a$ , the last integrator has just finished integrating and is driving ADC1, the coarse flash ADC. At the falling edge of clock P2, the latches of ADC1 begin to regenerate, and at the end of  $t_a$ , the conversion is complete. During  $t_b$ when P1 is high, the op-amp based DAC and subtractor, similar in appearance to the DAC/integrator stage of Figure 3.2, has time to settle. At the beginning of time slot  $t_c$ , the output of the subtractor is available and ADC2, the fine flash ADC, is strobed as P1 falls. If the fine flash latches can regenerate during  $t_c$ , both coarse and fine bits are available at the beginning of P2 for the integrator of Figure 3.2.

Although the conversion time of the comparator is much longer than the dead  $zone(t_a, t_b)$ , the time required for the preamplifier in the comparator is overlapped with the settling time of either the last integrator or subtractor, resulting in no additional delay in the signal path. So the only extra delay imposed by the comparators is the regeneration time of the latch. Circuit simulation of the two-stage regenerative latch in [31] shows that the latch settling time in 0.18-um CMOS technology is under 1 ns. Thus for typical clock rates, the dead zone requirement does not reduce significantly the settling time of the two-step ADC subtractor or the last integrator. The pulse width  $t_b$  is determined by the speed of the subtractor, which is restrained by the power budget. However, the subractor does not require high settling accuracy because its errors are noise-shaped by the modulator.

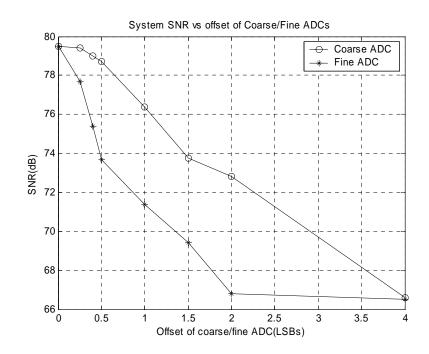

For the flash quantizer inside a common  $\Sigma\Delta$  modulator, comparator offsets usually need to be less than 0.5 LSB. However, the simulation result in Fig. 3.4 shows that the maximum allowable offset of the fine ADC is 0.25 LSB doubling the precision of the coarse ADC.

Because of capacitor mismatch, DAC noise will seriously degrade the system performance if it is not shaped by DEM. To allow processing time for DEM, additional delay can be added in the feedback path if half-delay integrators are used as shown in Figure 3.6. Half-delay integrators sample on one clock phase and update their outputs on the next, with the following stage sampling this output at the end of the update phase. The half-clock delay added to the feedback path makes it possible to apply DEM to shape the first-stage DAC noise digitally.

Figure 3.3 Timing diagram for Figure 3.2

Figure 3.4 Two-step quantizer with time slot allocation

Figure 3.5 The system SNR in a second-order  $\Sigma\Delta$  modulator versus the offset of coarse/fine ADCs inside an eight bit two-step quantizer

Even though two half-delay integrators are applied in the system of Figure 3.6, it has the same form of signal/noise transfer function as a standard second-order modulator because both the two-step ADC and the DEM block have half a clock delay.

Since the feedback loop of the last integrator only allows for one clock cycle delay, the DEM has to be removed from the loop. Although the DAC mismatch noise at the input of the last integrator is not digitally shaped, the gain of previous integrators shapes its spectrum, preventing it from dominating in-band noise.

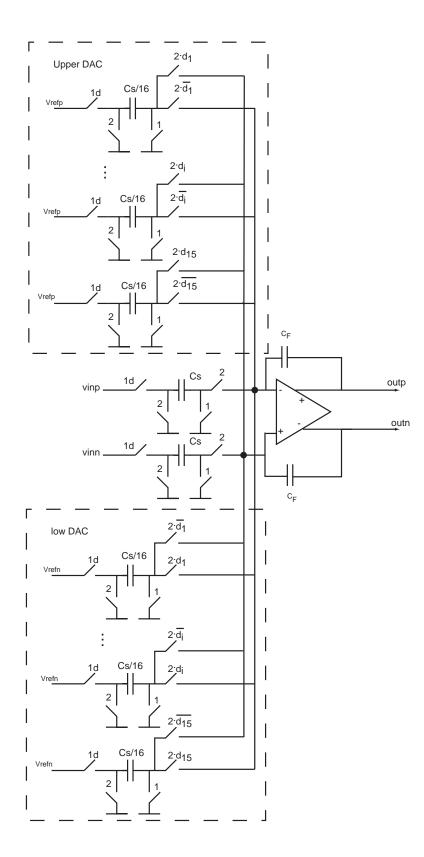

#### 3.3 Noise Shaped Requantization

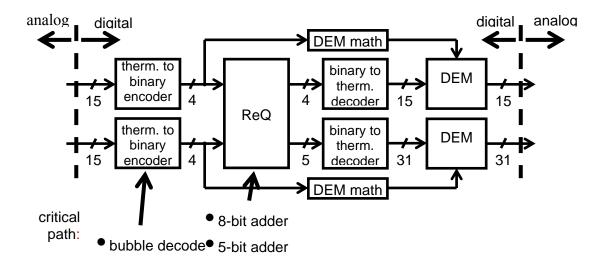

Similar to using two-step quantization to reduce the number of comparators in the flash ADC, one can use the segmented DACs(coarse/fine DACs) to greatly reduce the

number of unit elements in the DAC, as illustrated in Figure 3.7. Due to the mismatch of the analog components, this segmented architecture is subject to the leakage of the coarse quantization noise.

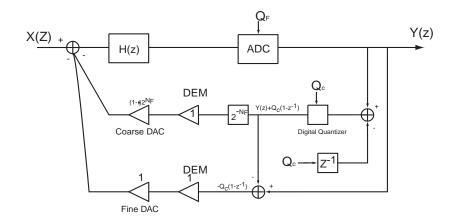

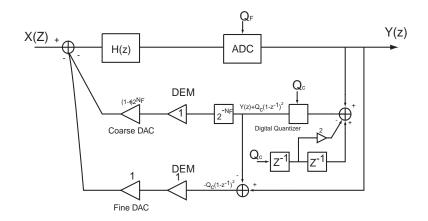

Figure 3.6 Example 2nd-order sigma-delta modulator with two-step quantizer

Figure 3.7 Block diagram of  $\Sigma \Delta$  ADC with the segmented DAC

In order to reduce the leakage coarse quantization noise, a noise-shaped requantization (REQ) method is introduced here. This method was originally proposed in [32] for a  $\Sigma\Delta$  DAC, however, in this chapter this concept is extended to  $\Sigma\Delta$  ADCs.

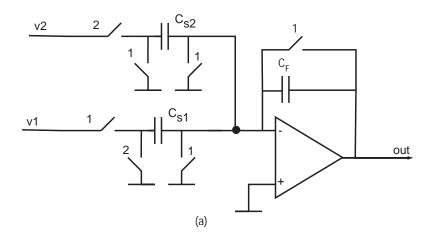

In Figure 3.7,  $N_C$  and  $N_F$  are the number of coarse and fine bits respectively and  $Q_C$  and  $Q_F$  are the coarse and fine quantization noise respectively. To obtain the coarse bits from the digital output, all the fine bits are truncated after passing a simple digital quantizer, introducing the coarse quantization noise to the feedback loop. This high level of noise should be cancelled when coarse and fine DACs are summed at the input of the modulator. The output of the quantizer is then divided by 2 <sup>NF</sup> to represent the binary right shift by  $N_F$ ; this is because the coarse output is the  $N_C$  most significant bits of an N-bit digital output. To compensate for this binary right shift, the gain of the coarse DAC should be 2 <sup>NF</sup> times that of the fine DAC. However, any mismatch between coarse and fine DAC will change this fixed ratio from its ideal value, noted as gain mismatch error, 1-0 in Figure 3.7. Although the mismatch noise inside each individual DAC can be filtered by two independent DEM circuits shown in Figure 3.7, part of the coarse quantization noise caused by the DAC gain mismatch directly leaks into the system output with no noise shaping, as will be shown below.

It can be found from the output of system, which is given by

$$Y(z) = \frac{X(z)H(z)}{1+(1-\theta)H(z)} + \frac{Q_F}{1+(1-\theta)H(z)} + \frac{\theta Q_C H(z)}{1+(1-\theta)H(z)}.$$

(3.1)

The last term in equation 3.1 is the leakage component, which vanishes as  $\theta \rightarrow 0$ . To prevent the leakage noise from dominating the output, the power of the leakage noise should be less than that of the fine quantization noise. This relation can be expressed as:

$$P_{Q_C} < P_{Q_F} \tag{3.2}$$

where  $P_{QC}$  and  $P_{QF}$  represent the power of the coarse leakage noise and fine quantization noise respectively. Since the coarse leakage noise has no noise shaping and fine quantization noise gets second-order noise shaping in a typical second-order  $\Sigma\Delta$ modulator, their powers are given as:

$$P_{Q_c} = \frac{\theta^2 2^{-2N_c}}{12} V_{\text{ref}}^2 \frac{2f_0}{f_s}$$

(3.3)

$$P_{\mathcal{Q}_F} = \int_{-f_0}^{f_0} \frac{2^{-2(N_c + N_F)}}{12} V_{\text{ref}}^2 \frac{1}{f_s} \left[ 2\sin(\frac{\pi f}{f_s}) \right]^4 df .$$

(3.4)

where  $V_{ref}$  stands for the reference voltage of the inner quantizer and  $N_{C}$ ,  $N_{F}$  is the number of coarse and fine quantization bits respectively.  $f_{0}$  is the highest signal frequency and  $f_{s}$  is the sampling clock rate.

Combining equation (3.2)-(3.4), one can get the condition for the coarse quantization noise leakage in a second-order  $\Sigma\Delta$  modulator, which is given by

$$\frac{\theta^2 2^{-2N_c}}{12} V_{\text{ref}}^2 \frac{2f_0}{f_s} < \int_{-f_0}^{f_0} \frac{2^{-2(N_c+N_F)}}{12} V_{\text{ref}}^2 \frac{1}{f_s} \Big[ 2\sin(\frac{\pi f}{f_s}) \Big]^4 df \qquad (3.5)$$

Assuming that the signal band is much lower than half of the sampling frequency, we may approximate equation (3.5) by

$$\frac{\theta^2 2^{-2N_c}}{12} V_{\text{ref}}^2 \frac{2f_0}{f_s} < \int_{-f_0}^{f_0} \frac{2^{-2(N_c+N_F)}}{12} V_{\text{ref}}^2 \frac{1}{f_s} \left(\frac{2\pi f}{f_s}\right)^4 df$$

$$= \frac{2^{-2(N_c+N_F)}}{60} V_{\text{ref}}^2 \pi^4 \left(\frac{2f_0}{f_s}\right)^5 \qquad (3.6)$$

Simplifying equation (3.6) leads to

and

$$\theta < \frac{2^{-N_F}}{\sqrt{5}} \pi^2 \left(\frac{2f_0}{f_s}\right)^2 = \frac{2^{-N_F}}{\sqrt{5}} \pi^2 \left(\frac{1}{\text{OSR}}\right)^2.$$

(3.7)

From equation 3.7, one can see that even for a moderate oversampling ratio of 16, the maximum allowable gain mismatch between the coarse and fine DAC in a second order  $\Sigma\Delta$  modulator with 4+4 inner quantizer is 0.1%, which is not easy to achieve.

Figure 3.9 Expanded View of REQ Block

In a  $\Sigma\Delta$  ADC with two-step quantization, the MSB and LSB signals can be combined and requantized using a first-order digital  $\Sigma\Delta$  modulator as shown in Fig. 3.7 and Figure 3.9. Referring to Figure 3.8, the digital coarse and fine signals from the quantizer are first concatenated to form an N-bit signal. This signal is then requantized to N<sub>C</sub> bits using a digital first-order modulator. The coarse signal is then subtracted from the original N-bit signal to form a new fine signal with N<sub>F</sub>+1 bits. After requantization, the new coarse and fine signals are:

$$Y'_{C}(z) = Y(z) + Q_{C}(1 - z^{-1})$$

(3.8)

and

$$Y'_F(z) = -Q_C(1-z^{-1}).$$

(3.9)

Signals  $Y'_{C}$  and  $Y'_{F}$  then pass through the independent DEM blocks and DACs and are summed at the input of the modulator. The effectiveness of the REQ block can be seen in Figure 3.10 where inside the REQ block the coarse quantization noise gets firstorder noise shaping before passing to the next stage. When the new coarse and fine signals are summed at the input of the modulator, the leakage noise component due to the DAC gain mismatch gets first-order noise shaping. This is manifested in the expression of the system output, which is given by

$$Y(z) = \frac{X(z)H(z)}{1+(1-\theta)H(z)} + \frac{Q_F}{1+(1-\theta)H(z)} + \frac{\theta Q_C(1-z^{-1})H(z)}{1+(1-\theta)H(z)}.$$

(3.10)

The last term of equation (3.10) is the leakage coarse quantization noise with first-order noise shaping.

Figure 3.10 The signal flow graph of a  $\Sigma \Delta$  ADC with a first-order requantization block

Figure 3.11 The signal flow graph of a  $\Sigma \Delta$  ADC with a second-order requantization block

The above first-order requantization can be extended to high-order at the expense of the complexity of fine DAC and DEM. Figure 3.11 shows the signal flow graph of a  $\Sigma\Delta$  ADC with a second-order requantization block where coarse quantization noise gets second-order noise shaping. The system output in Figure 3.11 can be written as

$$Y(z) = \frac{X(z)H(z)}{1 + (1 - \theta)H(z)} + \frac{Q_F}{1 + (1 - \theta)H(z)} + \frac{\theta Q_C (1 - z^{-1})^2 H(z)}{1 + (1 - \theta)H(z)}$$

(3.11)

Although the leakage coarse quantization noise can be greatly suppressed by using second-order requantization, the complexity of the fine DEM and DAC increases four times.

Since the leakage coarse quantization noise is shaped by the REQ block, the stringent requirement on the DAC gain mismatch can be greatly relaxed. As shown in equation (3.2), the power of leakage coarse quantization noise should be less than that of fine quantization noise. And their relative powers in a second-order  $\Sigma\Delta$  modulator with a first-order requantization are found to be

$$P_{Q_c} = \int_{-f_0}^{f_0} \frac{\theta^2 2^{-2N_c}}{12} \operatorname{V}_{\text{ref}}^2 \frac{1}{f_s} \left(2\sin\frac{\pi f}{f_s}\right)^2 df$$

(3.12)

and

$$P_{\mathcal{Q}_F} = \int_{-f_0}^{f_0} \frac{2^{-2(N_c + N_F)}}{12} \operatorname{V}_{\text{ref}}^2 \frac{1}{f_s} \left( 2\sin\frac{\pi f}{f_s} \right)^4 df .$$

(3.13)

Combining equation 3.2, 3.12 and 3.13 and assuming  $f_0 \ll f_s$ , the new condition for the DAC gain mismatch can be written as

$$\theta < 2^{-N_F} \pi \sqrt{\frac{3}{5}} \left(\frac{1}{\text{OSR}}\right).$$

(3.14)

For an OSR of 16 and fine bits  $N_F$  of 4, the maximum allowable DAC gain mismatch is 0.95%, which is nearly ten times bigger than that without noise shaping.

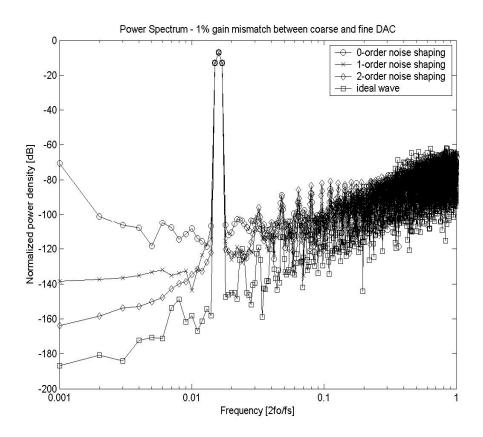

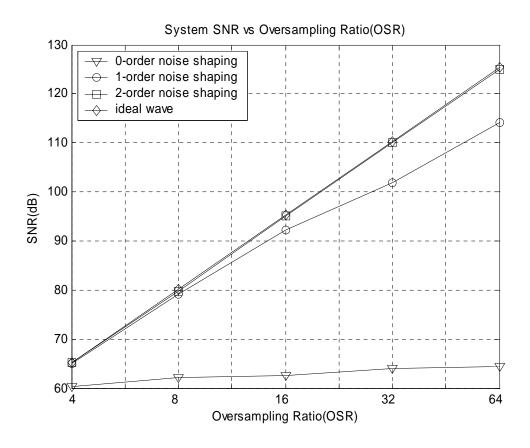

The effectiveness of the REQ block can also be seen in the behavioral simulation results shown in Figure 3.12 and Figure 3.13. By comparing the spectrum and SNR of a second-order  $\Sigma\Delta$  modulator with the same DAC gain mismatch and different order noise shaping of REQ, the simulation shows that the REQ block can greatly lower the quantization noise floor and increase the system SNR especially in the case of high oversampling ratio.

Although the REQ method can greatly relax the stringent requirement on gain mismatch between coarse and fine DAC, it contains several minor drawbacks. As the REQ order increases, more additional bits are needed for the fine DAC and DEM because the signal range of the new fine bits increases exponentially with the noise shaping order. Another potential drawback is a slight reduction in the input signal range due to the possible overflow of the REQ circuitry. This is because the REQ circuitry uses a fixedpoint number to represent the signal. For the second-order system simulated, no overflow occurs if the input is limited to 90% of full scale.

Figure 3.12 The simulated spectrums with different REQ orders in a second-order  $\Sigma \Delta$  modulator with 4+4 bit two-step quantization.

Figure 3.13 The simulated system SNR versus oversampling ratio under different REQ orders

## 3.4 Conclusion

The exponential increase in the complexity of the flash ADC, DEM and DAC circuitry with each added quantizer bit limits the internal resolution of a single-stage multibit  $\Sigma\Delta$  modulator. Two techniques have been proposed to resolve this dilemma. By incorporating half-delay integrators, careful two-step ADC timing, and other architectural changes, two-step quantization becomes feasible in a single-stage multibit  $\Sigma\Delta$  modulator using traditional, power-efficient switched-capacitor circuits. Coarse/fine segmentation combined with an REQ block allows for larger internal quantization without the

exponential increase in complexity of DEM and DAC circuitry, while still maintaining performance close to the alternative non-segmented system.

Although the two-step inner quantization with a moderate number of bits increases the complexity of the digital circuitry, this burden can be substantially reduced as CMOS technologies continue to scale.

## **4** Architecture and Behavior Simulation

In general, there are three primary degrees of freedom associated with the architecture selection for sigma-delta modulators: oversampling ratio, noise shaping order, and inner quantization bits. For the high-speed and high resolution sigma-delta modulator, the oversampling ratio must fall below the range of 64-512 typically used in low and medium speed oversampling converters [28, 30]. To offset the resolution loss caused by the decreased oversampling ratio, either noise shaping order or inner quantization bits must increase.

Although cascade architectures can easily increase noise shaping without the problem of instability, they are subject to noise leakage and the nonidealities of analog circuits. So increasing the inner quantization bits becomes a reasonable alternative to realize a high speed and high resolution modulator even though this introduces nonlinearity due to the multibit DAC.

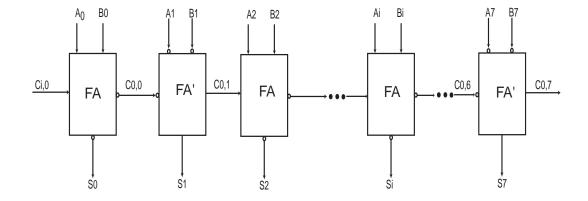

Chapter 3 shows that it is possible to build a single-stage modulator with a large inner quanitzer (above 6 bits) so that the oversampling ratio can be reduced to 8 or 16. To demonstrate that the novel architecture in chapter 3 can achieve high resolution (SNR > 70 dB) with very low oversampling ratio, a proposed high-speed, high resolution single-stage sigma-delta modulator with 8-bit inner quantization is implemented in the TSMC 0.25um mixed-signal process. The following section will introduce the architecture of the

proposed modulator and show how to find the critical design parameter using the behavior simulation.

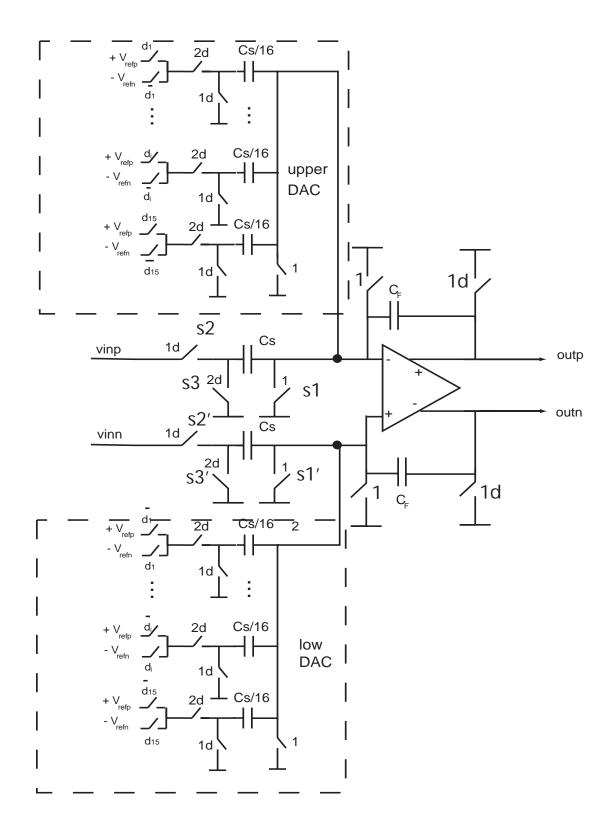

#### 4.1 System Architecture

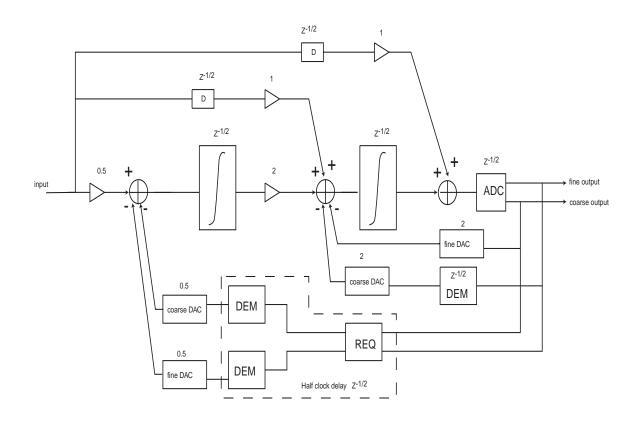

The proposed system architecture shown in Figure 4.1 extends the example of the second-order single-stage architecture in Figure 3.6. Based on two techniques discussed in chapter 3, a special 8-bit two-step ADC with only half a clock delay is chosen as the inner quantizer for the system. To reduce the complexity of DEM and the DAC, a segmented structure with 4-bit coarse and fine DACs associated with coarse and fine DEMs are also used in the system. Finally, to reduce the leakage of the coarse quantization noise caused by the mismatch between coarse and fine DAC, a digital noise shaping block called the requantization block is used in the feedback path of the system.

Due to the delay restraint of the feedback loop associated with the last integrator, only the coarse bits for the coarse DAC of the last integrator pass through a DEM block and the fine bits go directly the fine DAC. Since any nonlinearities from the DAC of the second integrator can be shaped by the gain of the first integrator, the elimination of DEM for the fine DAC of the last integrator does not degrade the performance of the system.

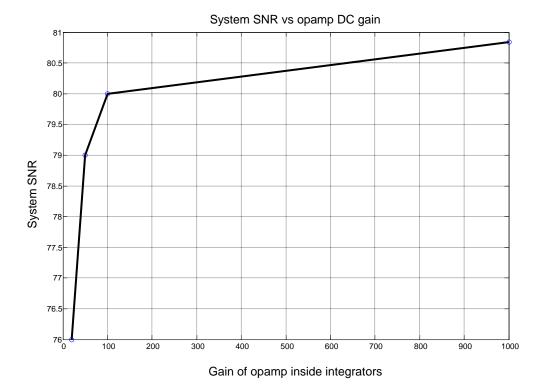

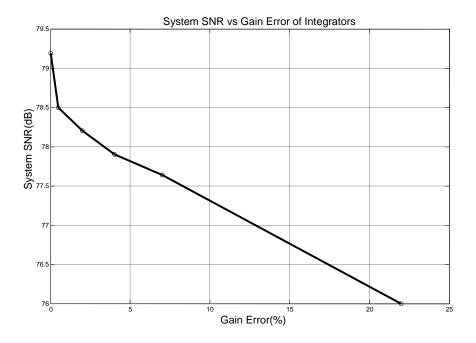

Compared with the typical second-order single-stage sigma-delta modulator, the proposed system in Figure 4.1 has two additional feed-forward paths. Although these two feed-forward paths do not change the noise transfer function, they help to reduce the output swing of two integrators. Because the large output swing of integrators requires very high opamp gain, which is not easy to achieve in the submicron process, the

48

proposed feed-forward paths help to alleviate the stringent requirement on the opamp gain even though they increase complexity of the system.

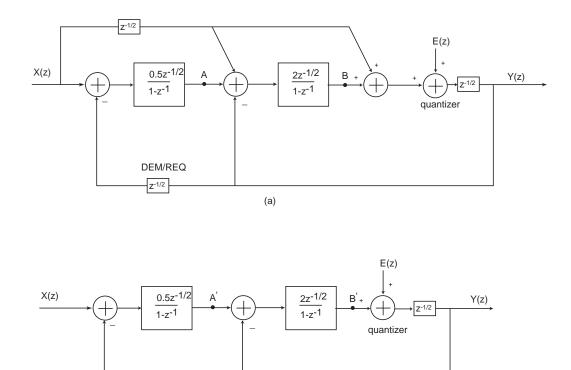

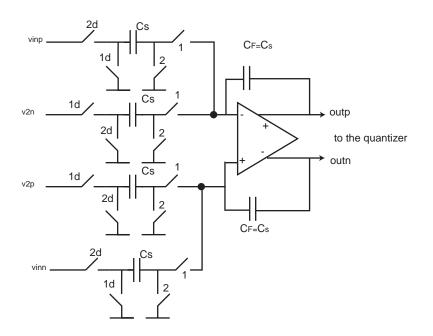

To better illustrate the functionality of the feed forward path, a linear approximation of the system is shown in Figure 4.2 (a), wherein the quantizer is modeled by signal-independent additive error sources and half a clock cycle delay, while the integrators are represented by their transfer function in the z-domain and the total delay of the digital feedback blocks, DEM/REQ is half clock cycle. E(z) represents the quantization noise caused by the 8-bit two-step ADC. Note that node A and B are the output of the first and second integrators respectively.

Figure 4.1 Block diagram of the system

From the linearized model of Figure 4.2 (a), the signal component of the first integrator output, A(z) is

$$A(z) = (0.5z^{-1/2} + 0.5z^{-3/2} - z^{-5/2})X(z).$$

(4.1)

In the same way, one can get the signal component of the second integrator output, B(z), which can be expressed as

$$B(z) = (z^{-1} - z^{-5/2})X(z).$$

(4.2)

Because in oversampling converters, the sampling clock frequency is much higher than the bandwidth of the input signal,  $z^{-1/2}X(z)$ ,  $z^{-3/2}X(z)$  and  $z^{-5/2}X(z)$  are very close. So the signal components in node A and B as illustrated equation 4.1-2 will be very small. Although the outputs of both integrators also include the components of quantization noise, this can be ignored because an 8-bit inner quantizer is used in the system.

By comparison, Figure 4.2 (b) is a linear model of the second modulator without a feed forward path. In the same way one can calculate the signal components in the outputs of the two integrators in Figure 4.2 (b). The expression for the signal components in both nodes are

$$A' = (0.5z^{-1/2} + 0.5z^{-3/2})X(z)$$

(4.3)

and

$$B' = z^{-1}X(z). (4.4)$$

Equations (4.3)-(4.4) demonstrate that the amplitudes of the signal components in the outputs of the integrators are very close to that of the input signal if no feed forward paths are used. As will be shown in the following sections, the small amplitude of the integrator outputs facilitates the circuit design of the integrators.

(b)

two feed forward paths

Figure 4.2 Linear model of the systems. (a) proposed system (b) proposed system without

#### 4.2 Matlab Simulations

DEM/REQ