Brigham Young University BYU ScholarsArchive

Theses and Dissertations

2005-04-13

# A Flexible Circuit-Switched Communication Network for FPGA-Based SOC Design

Clint Richard Hilton Brigham Young University - Provo

Follow this and additional works at: https://scholarsarchive.byu.edu/etd

Part of the Electrical and Computer Engineering Commons

### **BYU ScholarsArchive Citation**

Hilton, Clint Richard, "A Flexible Circuit-Switched Communication Network for FPGA-Based SOC Design" (2005). *Theses and Dissertations*. 312. https://scholarsarchive.byu.edu/etd/312

This Thesis is brought to you for free and open access by BYU ScholarsArchive. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of BYU ScholarsArchive. For more information, please contact scholarsarchive@byu.edu, ellen\_amatangelo@byu.edu.

# A FLEXIBLE CIRCUIT-SWITCHED COMMUNICATION NETWORK FOR FPGA-BASED SOC DESIGN

by

Clint R. Hilton

A thesis submitted to the faculty of

Brigham Young University

in partial fulfillment of the requirements for the degree of

Master of Science

Department of Electrical and Computer Engineering

Brigham Young University

August, 2005

Copyright © 2005 Clint R. Hilton

All Rights Reserved

# BRIGHAM YOUNG UNIVERSITY

### GRADUATE COMMITTEE APPROVAL

of a thesis submitted by

Clint R. Hilton

This thesis has been read by each member of the following graduate committee and by majority vote has been found to be satisfactory.

Date

Brent E. Nelson, Chair

Date

Michael J. Wirthlin

Date

Doran K. Wilde

### BRIGHAM YOUNG UNIVERSITY

As chair of the candidate's graduate committee, I have read the thesis of Clint R. Hilton in its final form and have found that (1) its format, citations, and bibliographical style are consistent and acceptable and fulfill university and department style requirements; (2) its illustrative materials including figures, tables, and charts are in place; and (3) the final manuscript is satisfactory to the graduate committee and is ready for submission to the university library.

Date

Brent E. Nelson Chair, Graduate Committee

Accepted for the Department

Michael A. Jensen Graduate Coordinator

Accepted for the College

Douglas M. Chabries Dean, Ira A. Fulton College of Engineering and Technology

#### ABSTRACT

# A FLEXIBLE CIRCUIT-SWITCHED COMMUNICATION NETWORK FOR FPGA-BASED SOC DESIGN

Clint R. Hilton

Department of Electrical and Computer Engineering

Master of Science

As FPGA densities continue to improve, single chips are becoming capable of implementing larger and more complex systems. Even today these systems may include several processors working in conjuction with a handful of other standard interfaces or custom modules. Additional system complexity naturally leads to added complexity throughout the different design and implementation stages. Attempting to design such a system while maintaining high performance and within a reasonable time frame is becoming more and more difficult.

Architectural design approaches ranging from direct module interconnection to sophisticated bus schemes have been used to build such systems, all with their own trade-offs. Often direct module interconnection results in the best overall performance but at the cost of design time and flexibility. Bus schemes on the other hand attempt to simplify the integration of the different hardware modules and allow for a more modular design approach. However, since the bus is a single shared interconnection medium, a practical limit is placed on the system's acheivable throughput. A relatively new architectural approach to system design involves a network-based communication infrastructure. A network-based interconnect scales much better than the shared bus and provides a potential increase in system throughput capabilities.

An effective approach would be one that can provide the throughput capabilities of direct interconnect, the modular design advantages of the shared bus, and the flexibility to adapt to different system requirements while maintaining lightweight communication.

A design infrastructure that attempts to meet these requirements has been developed. This infrastructure is based on a circuit-switched network architecture. The circuit-switching aspect allows two nodes, or modules, to temporarily establish a direct and dedicated connection for high-throughput data transfer. The networkbased topology allows this to occur without tying up all the interconnect resources as other routes can be used to connect the other nodes. Each node is connected to the network via a well-defined interface therefore allowing for modular design. Flexibility is built into the architecture to accommodate many different topology configurations. Lightweight protocols and handshaking mechanisms are used to establish node-tonode connections, and initiate and terminate data transfers.

Two different example applications have been implemented with this networkbased interconnect: one that involves the use of a single resource that must be shared among different modules, and another that has high system bandwidth requirements and dynamically schedules the use of functionally identical resources. These implementations were then compared against that of a bus-based approach. Both applications illustrate the effectiveness of this network architecture in SoC implementation.

# Contents

| Li       | st of | Tables   x                                    | vii       |

|----------|-------|-----------------------------------------------|-----------|

| Li       | st of | Figures                                       | xx        |

| 1        | Intr  | oduction                                      | 1         |

|          | 1.1   | Programmable SoCs                             | 2         |

|          |       | 1.1.1 Dynamic Module Replacment               | 3         |

|          | 1.2   | Ideal Architectural Approach                  | 4         |

|          | 1.3   | Common Architectural Approaches               | 4         |

|          | 1.4   | Programmable Network on Chip                  | 8         |

|          | 1.5   | Structure of This Work                        | 8         |

| <b>2</b> | Bac   | ground                                        | 11        |

|          | 2.1   | Relevant Work in SoC Design                   | 11        |

|          | 2.2   | Relevant Work in NoC Design                   | 13        |

|          |       | 2.2.1 Packet-Switching Architectures          | 13        |

|          |       | 2.2.2 FPGA-Specific Architecture              | 14        |

|          |       | 2.2.3 Packet Switching vs Circuit Switching   | 15        |

|          | 2.3   | Status of Xilinx Partial Reconfiguration      | 17        |

|          | 2.4   | JHDL                                          | 19        |

|          | 2.5   | Summary                                       | 19        |

| 3        | Pro   | rammable Network on Chip: General Description | <b>21</b> |

|          | 3.1   | Circuit-Switched Architecture                 | 21        |

|          |       | 3.1.1 Network Routers                         | 23        |

|          |       | 3.1.2 Network Modules                         | 26        |

|          |     | 3.1.3 CPU Interfaces            | 27 |

|----------|-----|---------------------------------|----|

|          | 3.2 | Modular Design Flow             | 28 |

|          | 3.3 | Clocking Scheme                 | 28 |

|          | 3.4 | Data Flow Control               | 28 |

|          | 3.5 | Summary                         | 29 |

| 4        | PN  | oC Router Description           | 31 |

|          | 4.1 | Router Component Overview       | 32 |

|          | 4.2 | Parameterizable Features        | 32 |

|          |     | 4.2.1 Port Interface            | 32 |

|          |     | 4.2.2 Router Connectivity       | 34 |

|          | 4.3 | Routing Table                   | 34 |

|          |     | 4.3.1 Table Updates             | 34 |

|          |     | 4.3.2 Illustrative Example      | 36 |

|          | 4.4 | Connection Process              | 37 |

|          |     | 4.4.1 Table Arbitration         | 37 |

|          |     | 4.4.2 Port Arbitration          | 39 |

|          |     | 4.4.3 Termination Process       | 41 |

|          |     | 4.4.4 Illustrative Example      | 41 |

|          | 4.5 | Summary                         | 43 |

| <b>5</b> | PN  | oC Module Interface             | 45 |

|          | 5.1 | Node Interface                  | 45 |

|          |     | 5.1.1 Router Updates            | 46 |

|          |     | 5.1.2 Interface FIFOs           | 48 |

|          | 5.2 | Data Transfer Process           | 48 |

|          |     | 5.2.1 Master Node Data Transfer | 48 |

|          |     | 5.2.2 Slave Node Data Transfer  | 50 |

|          |     | 5.2.3 Illustrative Examples     | 50 |

|          | 5.3 | Summary                         | 52 |

| 6 | $\mathbf{PN}$ | oC CPU Interface                     | 53 |

|---|---------------|--------------------------------------|----|

|   | 6.1           | Memory-Mapped Interfacing            | 53 |

|   | 6.2           | Network CPU Software                 | 54 |

|   |               | 6.2.1 CPU As Master                  | 55 |

|   |               | 6.2.2 CPU As Slave                   | 59 |

|   | 6.3           | Summary                              | 60 |

| 7 | PN            | oC Implementation Results            | 61 |

|   | 7.1           | PNoC Router Results                  | 61 |

|   | 7.2           | PNoC Module Interface Results        | 62 |

|   | 7.3           | PNoC CPU Interface Results           | 63 |

|   | 7.4           | Network Architecture Comparison      | 63 |

|   | 7.5           | Summary                              | 65 |

| 8 | PN            | oC Test Applications                 | 67 |

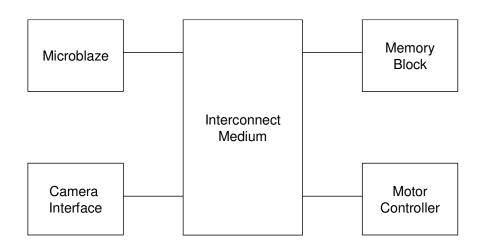

|   | 8.1           | Autonomous Robot                     | 68 |

|   |               | 8.1.1 General Implementation Details | 69 |

|   |               | 8.1.2 Shared Bus Implementation      | 70 |

|   |               | 8.1.3 Network Implementation         | 70 |

|   |               | 8.1.4 System Comparisons             | 71 |

|   | 8.2           | Image Binarization                   | 72 |

|   |               | 8.2.1 General Implementation Details | 74 |

|   |               | 8.2.2 Shared Bus Implementation      | 76 |

|   |               | 8.2.3 Network Implementation         | 76 |

|   |               | 8.2.4 System Comparisons             | 77 |

|   | 8.3           | Summary                              | 79 |

| 9 | Cor           | nclusion                             | 81 |

|   | 9.1           | Summary                              | 81 |

|   | 9.2           | Conclusions                          | 82 |

|   | 9.3           | Future Work                          | 83 |

| A PNoC Tutorial                                | 87  |

|------------------------------------------------|-----|

| A.1 Hello World Hardware Design                | 87  |

| A.1.1 The NetInterface Class                   | 88  |

| A.1.2 Network Module Design: A UART Example    | 88  |

| A.1.3 Network CPU Design: A Microblaze Example | 89  |

| A.1.4 Top-Level System Design                  | 89  |

| A.2 Hello World Software                       | 90  |

| A.3 Building the System                        | 90  |

| A.4 Hello World Source Code                    | 91  |

| A.4.1 UartNode.java                            | 91  |

| A.4.2 MicroblazeNode.java                      | 92  |

| A.4.3 NetMicroblaze.java                       | 93  |

| A.4.4 Microblaze.java                          | 95  |

| A.4.5 HelloWorld.java                          | 97  |

| A.4.6 HelloWorld.c                             | 100 |

| A.4.7 Software Makefile                        | 102 |

| A.4.8 Hardware Makefile                        | 103 |

| Bibliography                                   | 107 |

# List of Tables

| 4.1 | Router Port Interface Signals  | 33 |

|-----|--------------------------------|----|

| 5.1 | Node Port Interface Signals    | 46 |

| 7.1 | Router Results                 | 61 |

| 7.2 | Module Interface Results       | 62 |

| 7.3 | CPU Interface Results          | 63 |

| 7.4 | Network Comparison Results     | 65 |

| 8.1 | Robot System Comparison        | 71 |

| 8.2 | Binarization System Comparison | 78 |

# List of Figures

| 1.1 | System on Chip Mapping                             | 2  |

|-----|----------------------------------------------------|----|

| 1.2 | Direct Module Interconnect                         | 5  |

| 1.3 | Memory-mapped Peripheral Bus                       | 5  |

| 1.4 | Bus/Direct-interconnect Hybrid                     | 6  |

| 1.5 | Network on Chip Interconnect                       | 7  |

| 2.1 | The CLICHE Architecture                            | 14 |

| 2.2 | Butterfly Fat-Tree Network                         | 15 |

| 2.3 | Xilinx System Floorplan for Dynamic Module Support | 18 |

| 3.1 | Example PNoC Topology                              | 22 |

| 3.2 | A Single Router System                             | 23 |

| 3.3 | High Intra-Router Bandwidth                        | 24 |

| 3.4 | Routing Table Updates                              | 26 |

| 4.1 | Router Block Diagram                               | 31 |

| 4.2 | Topology for Dynamic Module Support                | 35 |

| 4.3 | Router Update Process                              | 36 |

| 4.4 | Table Arbitration Process - Block Diagram          | 38 |

| 4.5 | Table Arbitration Process - Timing Diagram         | 39 |

| 4.6 | Switch-box Hardware Diagram                        | 40 |

| 4.7 | Port Connection Process                            | 42 |

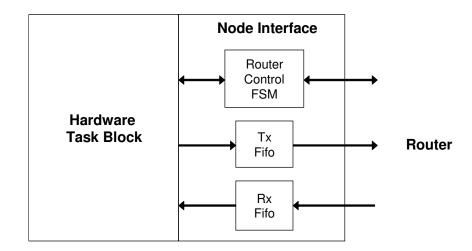

| 5.1 | Node Interface Hardware                            | 47 |

| 5.2 | A Module's Router Update Request                   | 47 |

| 5.3 | A Module's Connection Request                      | 49 |

| 5.4 | Master Node Write Sequence                         | 51 |

| 5.5 | Master Node Read Sequence                          | 52 |

| 6.1 | Network CPU Interfacing             | 54 |

|-----|-------------------------------------|----|

| 6.2 | Network CPU Interfacing in Software | 56 |

| 6.3 | CPU Interface - Connection Request  | 58 |

| 6.4 | CPU Interface - Data Transfer       | 59 |

| 6.5 | CPU Interface - Connection Release  | 60 |

| 7.1 | Network Architectures               | 64 |

| 8.1 | Robot Top-Level Modules             | 68 |

| 8.2 | Binarization Top-Level Modules      | 73 |

| A.1 | Hello World System                  | 87 |

### Chapter 1

## Introduction

The number of transistors that can be packed onto a single chip continues to increase at an exponential rate [1]. This increase in chip density clearly leads to an increase in the amount of logic that can be incorporated on the chip. More available logic resources allow for the implementation of larger and more complex systems. As a result the notion of a *System on Chip* (SoC) has taken form and become a popular research topic.

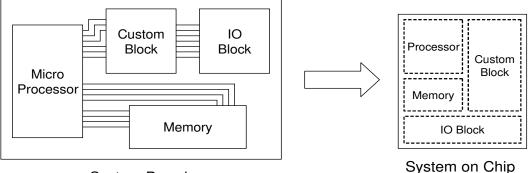

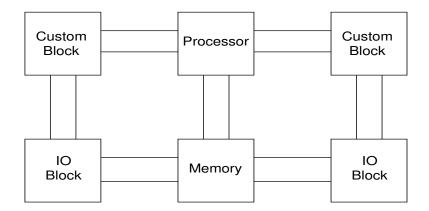

In the context of this work, an SoC is a system of interconnected components that are implemented on a single chip. SoCs often consist of a heterogeneous mix of components that include one or more general purpose microprocessors. Traditionally, systems often required complex board-level design since each component was implemented on a separate chip (ASSP, ASIC). Today however, similar systems can be targeted to a single chip as illustrated in Figure 1.1. Integrating everything onto a single chip often results in improvements in power consumption, manufacturing costs, and in many cases design time.

As these systems continue to grow in size and complexity, incorporating effective communication between components in a reasonable time-frame is becoming increasingly difficult. A significant amount of work has been done in an attempt to standardize SoC communication in order to facilitate intellectual property (IP) reuse and reduce design time. Shared buses and packet-switched network architectures are two of the more commonly proposed standard interconnects. This work compares these different approaches and presents an alternative interconnection scheme that

System Board

Figure 1.1: System on Chip Mapping

consists of a flexible circuit-switched rather than packet-switched network infrastructure. The advantages of this approach will be explained throughout this work.

#### 1.1 Programmable SoCs

A special family of chips known as Field Programmable Gate Arrays (FPGAs) are among those that have taken advantage of increasing chip densities. FPGAs are chips whose function can be defined at run-time through the downloading of a configuration bitstream. Because of the amount of logic resources available on today's FPGAs, entire systems can be implemented thereon. The combination of fast reconfigurability and vast resource availability make FPGAs an attractive target for SoC implementation. For these reasons the research presented in this work is targeted to FPGAs.

Though FPGAs are often larger, slower, and less energy efficient than their ASIC counterparts, FPGA-based SoC design provides several important advantages as identified in [2]:

• Fast Time-to-Market. The process of implementing a circuit onto an FPGA simply requires the generation and downloading of a configuration bitstream. Since this bitstream is generated with software tools and can be downloaded onto the FPGA in just seconds, these systems can quickly be tested and made ready for production. ASICs on the other hand require a mask to be generated and then shipped off for fabrication, which can take months, before being able to test the actual hardware implementation.

- Lower Manufacturing Costs. This bitstream generation process is not only fast, it is also inexpensive. Improvements can be made to the system design and a new bitstream generated without any additional cost. Fabrication of ASICs however, is extremely expensive. Unless the product is intended for mass production, many cannot even afford the manufacturing costs.

- Flexibility. The flexibility provided by FPGAs through reconfiguration is what set them apart from traditional ASICs. This allows for system updates as improvements are made and bugs are identified and corrected. The ability to completely change the system's operation on the fly is a valuable feature for many application domains. Several FPGA families also come equipped with the ability to perform *partial* reconfiguration, where only a specific portion of the circuitry is modified on the fly while the rest remains busy performing its defined task. This opens up a completely new design paradigm that involves the capabilities of dynamic module replacement.

#### 1.1.1 Dynamic Module Replacment

In order to understand where dynamic module replacement might prove useful, it is first important to discuss the different components that might make up an SoC. In many system-based applications a CPU, or a group of CPUs, make up the primary control for the system. The CPU core communicates with the other modules of the system to complete the desired task. These other modules may consist of standard interfaces such as a UART controller or memory interface, or they may be completely custom circuits that perform some specialized computation.

The advantage of dynamic module replacement arises when certain modules are used during specific time periods throughout the system's active life. In such cases these modules can be plugged in only when needed, and then replaced by something that would prove more useful during the times the module is not needed. Likewise, if certain responsibilities of the system change over time, more appropriate modules can be plugged into the system to meet its changing needs.

#### 1.2 Ideal Architectural Approach

In considering the challenges of system design, an ideal SoC architecture would be one that includes the following characteristics:

- High system throughput. Fast and unimpeded data transfer between modules.

- System flexibility. Architecture configurability that enables the construction of numerous topologies to meet the specific system requirements.

- Lightweight communication. Interconnect mechanism doesn't severely limit the resources available for system task modules and simple protocols for lowoverhead communication.

- Modular design. Design approach that facilitates reuse of IP blocks with as little concern for the interconnect mechanism as possible.

#### **1.3** Common Architectural Approaches

Many different architectural approaches have been proposed to meet the challenges of complex SoC design. Some of the more common SoC architectural approaches and their respective trade-offs can be categorized as follows:

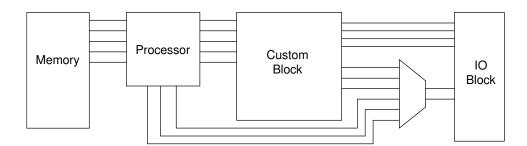

• Direct Module Interconnect. Shown in Figure 1.2, this approach consists of modules that are directly connected in a custom manner so data can be transferred between modules exactly as needed. As a result, systems designed using this approach tend to achieve higher throughput, lower latency, and in most cases require fewer resources. However, since this is a more custom approach, design time is lengthened, and flexibility is reduced. Whenever a module is

Figure 1.2: Direct Module Interconnect

modified during the design phase, the entire interconnection associated with that module may also require modification.

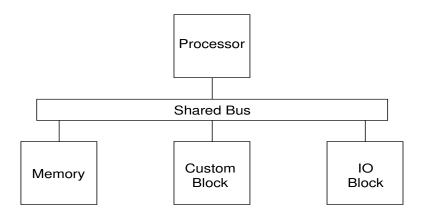

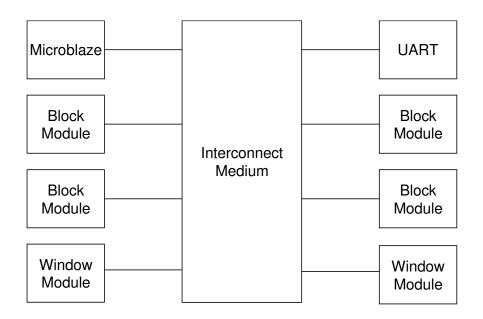

Figure 1.3: Memory-mapped Peripheral Bus

• Memory-mapped Peripheral Bus. By nature this approach, shown in Figure 1.3, is often processor-centric and uses a shared memory/peripheral bus to allow for communication between modules. Because there is a fixed interface to the shared bus, this architecture lends itself to a modular design approach therefore resulting in reduced design time and increased flexibility. The use of a single shared bus however, places a limit on the achievable system throughput and can significantly increase the worst-case latency. As the system increases in size the bus becomes an even more severe bottleneck.

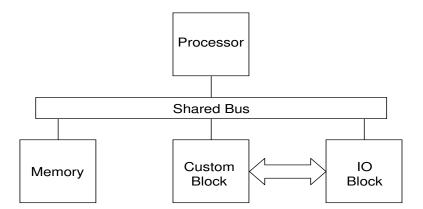

Figure 1.4: Bus/Direct-interconnect Hybrid

- Bus/Direct-interconnect Hybrid. One of the more common approaches currently used is a combination of the previous two design strategies. This hybrid approach, shown in Figure 1.4, generally uses a shared peripheral bus for all communication involving processor(s) and/or memory interface(s). For other intra-module communication, direct interconnect may be used. In many cases this approach takes advantage of the strengths of both strategies. The ability to have modules directly connected may remove the shared bus as the throughput bottleneck, and at the same time reduce average bus access latency. As previously mentioned, this direct interconnect can have adverse effects on the design time and flexibility of the system design.

- Network on Chip Interconnect. There are many different variations of network topologies that have been proposed to serve as the interconnect for SoCs. Most consist of a 2-D mesh-based topology, similar to that shown in Figure 1.5,

Figure 1.5: Network on Chip Interconnect

and perform packet switching using wormwhole or cut-through routing. In general, a network interconnect provides several advantages over the bus architecture. Probably the most important advantage is in its scalability. Systems are only going to get larger and more complex as time goes on, and bus architectures will likely not accommodate the increasing communication demands. Network architectures may soon become the dominant interconnection mechanism. In addition to their scalability, their potential for high-throughput data transfer is a feature that may help to propel them to the forefront of SoC architectures. In many cases network-based interconnect also results in a more energy-efficient system since the data does not need to be broadcast to every module of the system. However, there are a few concerns with the network architectures that have been proposed. The main disadvantages result from the overhead incurred by the networking infrastructure. The routing circuitry tends to tie up a significant portion of the available resources. Also the packet-switched nature of these architectures cause problems for applications that require heavy data flow between modules. The process of forming, parsing, and buffering packets incurs substantial overhead. Because of these weak points, none of the proposed network architectures have become widely accepted for use in SoC design.

#### 1.4 Programmable Network on Chip

An SoC architecture has been created that attempts to match the characterists of the ideal SoC. This architecture is based on a circuit-switched rather than packet-switched networking infrastructure. A router, or series of routers, is used as the interconnect medium for the system's modules. Lightweight protocols and handshaking mechanisms are used to establish dedicated point-to-point connections between two modules to allow for high-throughput data transfer. Other modules can simultaneously establish point-to-point connections since there is no single shared bus but a series of possible routes between modules.

A significant amount of flexibility has been built into this architecture to allow for the creation of numerous network topologies. Due to the programmable nature of the proposed network architecture, this infrastructure will be referred to as Programmable Network on Chip (PNoC). A modular design approach can be used since each module has a well-defined port interface to this network. This often results in improved design time and increased design flexibility as it becomes much easier to modify or replace modules during the design process.

Another important benefit of a fixed communication interface is the ability to support dynamic module replacement. Unfortunately the current design flows as provided by FPGA vendors for partial reconfiguration are not well-developed. Generating dynamic module bitstreams, though possible, is a relatively difficult task. The work described here doesn't actually demonstrate the dynamic replacement feature but support for it is built into the architecture.

#### 1.5 Structure of This Work

In the chapters that follow, current SoC architectures will be identified, and the PNoC will be described in more detail. The following is an outline of what is contained in this work:

- Related work in this area is presented and analyzed.

- A general technical description of the PNoC is provided.

- A discussion of the network router.

- An explanation of network modules and their design requirements.

- The details of the CPU network interface and its corresponding software usage are described.

- Two example applications are presented and the features they exploit are identified. Their PNoC implementation is also compared to that of a more standard approach.

- A conclusion of this work is provided.

The appendix provides a step-by-step tutorial for constructing a system using the PNoC architecture.

### Chapter 2

# Background

A significant amount of work has been done that has helped to inspire and motivate some of the architectural decisions that have gone into this research. The first section of this chapter describes different advancements that have been realized in SoC design. The second section of the chapter analyzes different network-based approaches that have been proposed and their respective contributions. The third section briefly describes the status of partial reconfiguration for Xilinx FPGAs. The fourth and final section introduces JHDL (a Java-based Hardware Description Language), which was used in the implementation of this work.

#### 2.1 Relevant Work in SoC Design

In recent years SoC design has become a viable solution for the implementation of a variety of complex systems. Initially, and still in many cases these SoCs are designed in a custom manner and are specific to the application at hand. Many researchers realize however, that as chip densities continue to increase, and systems grow in size and complexity, the design of such systems in a reasonable time-frame will not likely be feasible. As a result, the push for a more general or standard interconnection mechanism that will allow for a modular design approach is critical for future SoC design.

A common architecture that is based on a processor-centric system is that of the shared bus, shown previously in Figure 1.3. Example bus architectures that have become well established include the ARM-based AMBA bus [3] and IBM's CoreConnect [4]. Since the shared bus is a standard interconnection medium, it allows for a modular design approach that facilitates IP reuse [5]. Given a well-defined interface to the bus, each module can be effectively designed, tested, and debugged independently. However, a strictly bus-based architecture has serious limitations since the modules of the system are confined to a single bus for all data transfers. A more favorable bus architecture is one that supports multiple split buses through the use of bus bridges. This can allow multiple bus transactions to occur simultaneously as long as they occur on different bus segments. However, split-bus architectures affect the design simplicity and flexibility of the system as changes to the system components may also require changes to the overall bus structure.

Another bus-based approach that is often attractive is the bus/directinterconnect hybrid architecture (refer back to Figure 1.4). Such an architecture is provided in both Xilinx's Embedded Development Kit (EDK) [6] and Altera's System On Programmable Chip (SOPC) Builder [7]. Both platforms use a shared bus architecture, but maintain the design flexibility that allows for modules to be directly interconnected as well. The shared bus is primarily used for communication involving the CPU or memory interface. The direct interconnect capabilities allow for high-throughput data transfer between modules.

In such systems the CPU is often used to coordinate the scheduling of tasks and then perform certain functions that are not time-critical while the hardware modules execute the compute-intensive tasks. Since the modules can pass data through direct connections, the shared bus is often eliminated as the system's performance bottleneck. In addition to increasing the system throughput capabilities, this hybrid architecture also scales better than a typical bus approach because only the modules that need to communicate with the CPU actually need to connect to the bus. The direct connection capabilities, however, do complicate the design process. This custom interconnect reduces the modularity of the system so more time must be spent verifying the integration of the system modules.

#### 2.2 Relevant Work in NoC Design

As the trend for larger and more complex SoCs continues, several important design considerations arise. In [8] a few of these are identified and discussed. One that received particular attention involves system clocking schemes. In many current SoC architectures, the systems are implemented using a single clock source. As chips become more dense, and systems become more complex, this simple clocking scheme will not suffice. Instead a globally asynchronous – locally synchronous scheme was proposed to meet the needs of today's growing systems.

In addition to clocking, it was also suggested that the limited scalability of bus architectures will eventually give rise to network-based interconnects. The sharedmedium bus architectures are effective for systems requiring only a handful of interconnected modules, but for larger systems the bus becomes a critical limiting factor. On-chip networks that provide multiple interconnecting routes between modules are an attractive solution for increasingly complex SoCs.

#### 2.2.1 Packet-Switching Architectures

One of the early network architectures proposed for use in SoCs was developed at Stanford and presented in [9]. In making their case for a network-based approach, it was pointed out that networks would be preferred to buses because they have higher potential bandwidth as they are capable of supporting multiple concurrent data transactions. Their proposed architecture consists of a 2-D folded torus topology where each module includes a small area reserved for networking logic so that packets can be routed among all modules on the network.

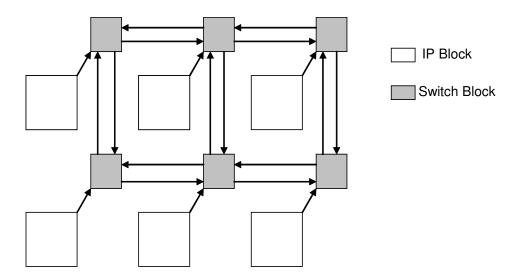

Another group [10], proposed a similar 2-D mesh topology that requires a routing switch for each module on the network as shown in Figure 2.1. They named their approach CLICHE (*Chip – Level Integration of Communicating Heterogeneous Elements*) as they emphasized the notion of heterogeneous system design. They argue that many systems perform a variety of tasks and therefore require a heterogeneous mix of modules to make up the system. Though their architecture is highly scalable, they concede that their architecture is unsuitible for certain heavy data flow

Figure 2.1: The CLICHE Architecture

systems due to its limited performance which comes as a result of its message passing overhead.

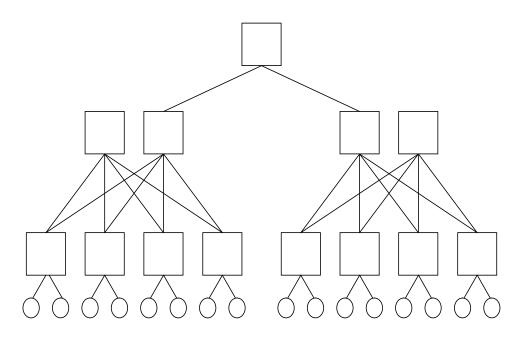

Research published in [11], at the University of British Columbia, proposed a completely different network topology in an attempt to create an effective SoC architecture. This topology, shown in Figure 2.2, is described as a butterfly fat-tree graph where the leaves of the tree represent the IP blocks and the vertices correspond to the network switches. The motivation for this topology is to minimize wire delay for the system. This architecture helps to reduce global wire lengths between nodes and allows for better interconnect delay predictions. Their argument as to why bus architectures are so limited is due to the bus's long wire delays. With their proposed architecture, the minimal wire delays would serve as the major source for improved overall system performance and scalability.

### 2.2.2 FPGA-Specific Architecture

The network architectures previously described are targeted to general SoC platforms. A few network-based SoC architectures have been developed that specifically target FPGAs. One such architecture was proposed by a group from Belgium

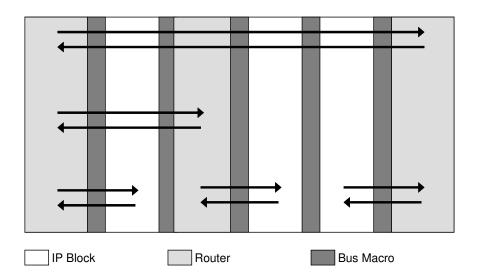

Figure 2.2: Butterfly Fat-Tree Network

[12]. The topology for this architecture is similar to that proposed in [9]. It consists of a 2-D torus topology and performs packet switching through the use of wormhole routing. This work was among the first in publication to use partial reconfiguration for dynamic module replacement in the context of network-on-chip design. With a fixed routing network established, partial reconfiguration could be used to dynamically replace individual modules on the network, allowing for dynamic hardware multi-tasking. A more detailed description of this process is provided in Section 2.3.

#### 2.2.3 Packet Switching vs Circuit Switching

All of the network architectures previously mentioned make use of packet switching, and surprisingly few even mention the possibility of a circuit-switched approach. Two groups: [13] and [14], provide strong arguments for the use of circuitswitched networks in SoC implementations.

The major difference between packet-switched and circuit-switched networks is in how the data is transferred between modules [15]. In packet-switched networks, data packets, also called *datagrams*, consist of fixed-length blocks of data that contain routing information and are independently routed through the network to the desired destination. In circuit-switched networks, a dedicated connection path (i.e. *virtual circuit*) between two modules is established so the raw data can be freely transferred between the modules.

Packet-switched networks often allow for greater resource utilization as many packets can be in flight at a given instant. They are well-suited to systems that exhibit short, bursty data traffic that can easily be formed into packets [14]. However, in general they require more sophisticated congestion control and packet processing. Large buffers are often required to queue up packets awaiting the availability of routing resources.

Circuit-switched networks, on the other hand, are connection-based, meaning that a module must first go through the process of establishing a dedicated connection path to the desired destination before transferring data. This can introduce undesirable latency, but once the connection is made, high-throughput data transfer between the modules can be guaranteed, and the data latency is extremely predictable. In general, circuit-switched networks are better suited for data traffic that is longer in duration as the connection setup time becomes negligible [14]. A common argument against circuit switching is its potential for significant underutilization of the communication links. Connections may be established in which the communication remains idle for an extended period of time. This can result in inefficient resource utilization if other modules need access to that communication link.

Both [13] and [14] propose fixed circuit-switched network topologies and focus on link scheduling techniques to maximize communication link utilization. This research presents a flexible circuit-switched network that uses a low-overhead connection setup process to accommodate both long and short data traffic and improve link utilization. A circuit-switched approach was chosen due to its relative simplicity, low overhead, modular design, and intra-module throughput capabilities.

### 2.3 Status of Xilinx Partial Reconfiguration

Partial reconfiguration as currently supported by Xilinx is explained in [16]. This capability allows one or more configuration frames to be reconfigured while the rest of the chip remains active. Special bus macros are used to retain connectivity between the logic being reconfigured and the active portion. Such a feature allows for the design of a static routing fabric and a series of reconfigurable nodes or modules. The modules retain their connection to the routing fabric during reconfiguration through the use of these bus macros. Because of the frame structure of current Xilinx devices, there are some design limitations when attempting to support partial reconfiguration. The reconfigurable modules must meet the following requirements:

- Since reconfiguration frames are column-based, the module's height must always be the full height of the device.

- Since the reconfiguration frames are each four slices wide, the module must be horizontally placed on four-slice boundaries and its width must be a multiple of four slices.

- All logic resources that lie within the boundary of the reconfigurable module are part of that module's reconfiguration frame. This includes all block RAMs, multiplier blocks, TBUFs, IOBs, and routing resources. This makes generic module-based bitstream generation a difficult task since the configuration frames are not identical.

Generating a bitstream for a module that meets these requirements involves specific floorplanning. This can be done at the HDL level through the use of lowlevel LOC calls to constrain the tools during the placement phase. The alternative is to design the module using a low-level tool such as FPGA Editor. Neither of these solutions are very attractive for large or complex modules. Unfortunately there is currently no high-level constraint parameters that can be applied to a module at the top-level to keep it constrained within a specified reconfiguration frame. Once a partial bitstream has been generated, it can be loaded onto the FPGA through the use of the Xilinx internal reconfiguration access port (ICAP). ICAP consists of an 8-bit input data bus and an 8-bit output data bus that allows internal logic to reconfigure the device's configuration memory, therefore modifying the hardware's functionality. Work presented by a group at Xilinx [17] introduces a software API for accessing the ICAP on a Virtex-II device. Through these API calls the system software can perform the dynamic module insertion/replacement.

As mentioned in Section 2.2.2, the research presented in [12] uses partial reconfiguration to provide dynamic module support. Their work uses the ICAP API calls to perform the desired hardware replacement. In order for their system's modules to meet the reconfiguration requirements previously listed, their 2-D torus was folded into a 1-D torus and bus macros were incorporated at the module port interfaces. A floorplan of their system is shown in Figure 2.3.

Figure 2.3: Xilinx System Floorplan for Dynamic Module Support

As mentioned previously, because of the difficulty in generating useful partial reconfiguration bitstreams, this work doesn't demonstrate the use of dynamic module replacement, but provides architectural support for that capability once partial bitstream generation becomes more widely supported.

### 2.4 JHDL

The actual implementation of this work was done using JHDL and its associated simulation tools. JHDL, developed at Brigham Young University and presented in [18], consists of a library of Java classes that provide an object-oriented approach to structural FPGA circuit design. Also included in this library is a graphical simulation environment and EDIF netlister. The following features of JHDL led to its selection as the principle design tool for this work:

- Standard programming language Java, a well-developed, widely-used programming language with extensive documentation, significantly facilitates the construction of parameterizable circuits.

- **Debugging capabilities** the circuit generation process can be easily monitored and debugged with the use of traditional software debugging tools and print statements. A native Java simulation tool that uses the Swing libraries allows for seamless integration between circuit generation and circuit simulation.

- **Polymorphism** the ability for network modules to extend the NetInterface class simplifies the design of user modules and their integration with the network infrastructure.

### 2.5 Summary

Much work has been done recently in the area of SoC design. As custom approaches have been dominant in SoC design up to this point, two alternatives have been growing in popularity: bus-based and network-based architectures. Shared bus architectures have gained momentum since on-chip processor cores have become increasingly common in SoC implementations. This processor-centric infrastructure allows for a modular design flow that simplifies SoC design. Network architectural approaches have been growing in popularity as chip densities continue to increase and SoCs grow in size and complexity. The network's scalability and potential bandwidth improvements make them an attractive alternative.

Several network architectures have been identified, most of which use packet switching with wormhole routing. The network architecture proposed in this work is based on a circuit-switched communication mechanism to allow for localized highthroughput data transfer. Extensive flexibility is provided to allow for numerous system configurations and run-time dynamic module replacement. Lightweight protocols and modular-based design simplify the creation of systems components. JHDL has been selected as the design tool for this system as its features further simplify the design of parameterizable system modules.

## Chapter 3

## **Programmable Network on Chip: General Description**

The goal of this work is to create an effective interconnection framework for use in SoC design. Two major aspects set this work apart from that which has been previously done. First is the circuit-switched approach that this architecture implements, which can guarantee high-throughput data transfer between two modules that share a dedicated connection. The second characteristic is the flexibility built into this architecture that simplifies the creation of numerous system topologies while maintaining lightweight communication. Several pieces are required to make such a system work. This chapter is dedicated to giving a general description of these pieces and illustrates how they come together to make an effective network architecture. The following chapters provide a more detailed explanation of the actual implementation for each of these pieces.

### 3.1 Circuit-Switched Architecture

As discussed previously, circuit switching provides advantages over packet switching in that once two modules have set up a dedicated connection between each other, they are guaranteed a period of unimpeded data transfer. This takes advantage of an assumption made on general heterogeneous systems – which is that most of the critical high-throughput data transfer occurs between specific nodes, and is not uniform among all modules of the system. Circuit switching can allow the critical nodes to establish dedicated connections to more effectively increase the system's throughput capabilities.

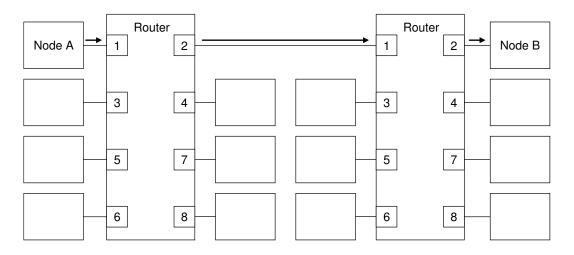

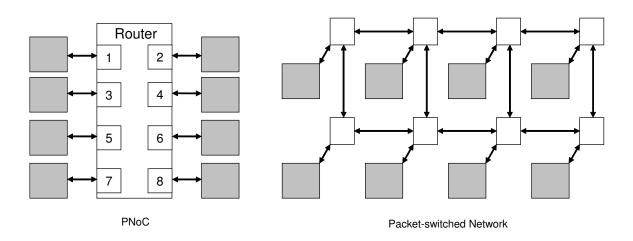

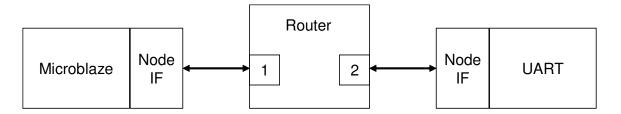

Figure 3.1: Example PNoC Topology

The proposed network topology consists of a series of subnets where each subnet consists of a single router along with several network modules or nodes. Figure 3.1 shows how a simple system might be connected using this architecture. The architectural features that define the circuit-switched nature of this network are built into the system's routers. A lightweight handshaking mechanism is used to establish the dedicated connection between modules. The node that desires to establish the connection, referred to as the master node (Node A in the figure), sends a request to the router. The router services the request and determines which port is associated with the desired target node (Node B). In this example the connection request is forwarded on to the second router since the target node (Node B) resides in its subnet. The second router then processes the request to identify the port connected to the target node. Once that port (port 2) becomes available, the router establishes the dedicated connection and informs the master that the connection has been made. The master and slave are then free to transfer data as necessary.

Once the master has determined that the data transfer is complete, a port release command is sent to the router and the connection is terminated. The released ports then become available for use by other modules. A timeout mechanism has also been incorporated into the router that monitors the requests for a busy port. If a pending request awaits the release of a busy port, a *pend* signal will be issued to that connection's master node. The master node can monitor this signal to detect when a timeout occurs, at which point the master issues a release command to allow the pending module access to the shared resource. If the master node still needs access to the port it can re-issue a connection request command and wait for the port to become available again. It is through this time-multiplexing mechanism that no single module can completely tie up a shared resource. This timeout mechanism is optional since there may be some cases where a master node cannot allow interruption of its dedicated connection.

#### 3.1.1 Network Routers

In this architecture the network is divided up into one or more subnets. The router serves as the central module for each subnet on the network. Each router can be configured with up to eight ports that serve as the interface by which modules are connected to the router.

Figure 3.2: A Single Router System

In systems where several subnets are required, some of those ports must be reserved for intra-router connections so that data can be transferred between subnets. The data widths for these ports are parameterizable. The configurability of these routers allows for the creation of a topology that is specialized for the application at hand. The manner in which modules are connected to the routers is also flexible. In designs that involve only a few modules, a single router can be used with all ports available for module connectivity as shown in Figure 3.2.

Figure 3.3: High Intra-Router Bandwidth

On the other hand, in systems that involve many modules and require significant cross-subnet communication, several of the router's ports can be connected to neighboring routers to increase the intra-subnet bandwidth. An example of such a system is shown in Figure 3.3.

As mentioned in the previous section, the routers are responsible for the establishment of dedicated connections between modules. In making these connections, the router performs two different phases of arbitration. The first phase involves arbitration for access to the routing table. When a connection request is received from a master node, it is accompanied by a destination address. The router arbitrates which master's request to process and then performs a table look-up to see which port is associated with the selected master's target address. Module addresses in this system are function based. For example, two modules that perform the exact same task can be configured to have the same source address. In this way it is possible to increase performance if multiple modules often perform a common task and there exist multiple such resources. Since there may be multiple instances of a particular target address it is likewise possible that there exist multiple ports associated with that address. This is where the second phase of arbitration occurs. The router selects just one of the ports in order to establish the dedicated connection, and leaves the other open for another module to access.

Since the routing table is the means by which the router associates modules and ports, in order to support dynamic module replacement there must exist a mechanism for updating the routing table. This initially occurs at startup. Each module sends a router update request to its associated subnet router. The router services these requests similar to a connection request and modifies its table. Then, when a module is to be replaced via partial reconfiguration, the dynamic module controller, whether it be software based or a dedicated hardware block, is responsible for clearing the module to be replaced from the routing table. Once the new module has been configured into the network it must send a router update request to update the routing table with its source address. When the router services a router update request it forwards that request on to all routers with which it is connected. In this manner each router on the network knows exactly which ports are associated with a particular module address.

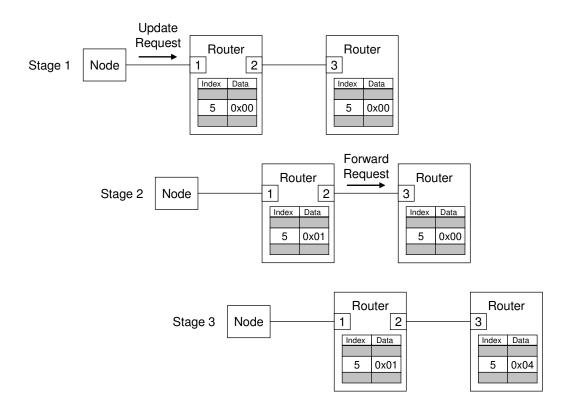

Figure 3.4 illustrates how a recently configured module with a source address of 5 updates the routers on the network. Represented in the figure is a three-stage update process. In the first stage the updating node issues a router update request to its subnet router. During the second stage, the router updates its table by modifying the entry at index 5 (the node's source address). The data in the table is a mask value where each bit corresponds to one of the router's ports. In this example, a 0x01 is written at index 5 for the first router since port 1 was the source of the update request. Also during stage 2, the router forwards the update request to the

Figure 3.4: Routing Table Updates

other router(s) in the network. The neighboring router updates its table during stage three, which involves writing the value 0x04 at index 5. A 0x04 is written as it maps to port 3 (0x04: the third bit is a 1). This process continues until each router has received the update and is capable of associating the node address 5 with one of its port interfaces.

### 3.1.2 Network Modules

A network module can consist of practically any hardware task block. This might range from something as simple as a single adder to something as complex as an entire subsystem. The only qualification for a network module is that it must require some sort of communication with other network modules and it must fit on the target device. Good candidates for network modules are those blocks that can be shared by several different hardware tasks. Some examples might include standard interfaces such as memory controllers, UART controllers, and other off-chip communication interfaces. Special custom modules may also fit these requirements. If several hardware tasks require the use of an FFT block or some common custom computation, that computation can be implemented as a network module and can therefore be shared among the modules that require its services. Another hardware block that is likely a good candidate to be implemented as a network module is a general purpose processor. In many systems, a CPU is the module responsible for controlling the scheduling of tasks and, as a result, requires connectivity to all the hardware modules involved.

Once a hardware task block has been identified as a viable network module it must be appropriately interfaced to the network. As a result, each network module consists of two parts: the hardware task block and the network interface. All modules connected to the network must conform to a well-defined top-level interface so that dynamic module connectivity can be supported. The network interface portion of the module is responsible for performing router update requests and connection requests. It is also responsible for the implementation of congestion control and crossing clock domains if required by the network implementation. Both of these issues will be addressed later in this chapter.

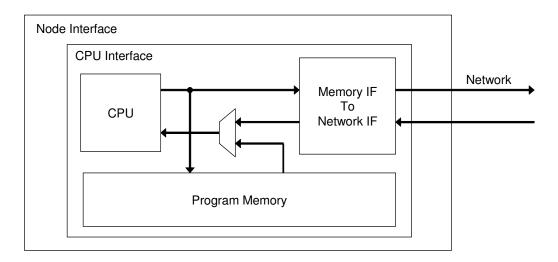

### 3.1.3 CPU Interfaces

In this system, CPU modules are a special type of network module. In order for a CPU to effectively communicate with other modules on the network, there are two types of memory mapping that must take place. The first is a mapping for establishing network connections, and the second is a mapping for network-based data transfers. The CPU's connectivity to the network is directly controlled by the software. The software uses a *network access* pointer to initiate and terminate connections to other modules on the network. Similarly, the software then uses a *network data* pointer to transfer data to the desired network module. Chapter 6 explains the details of the CPU network interface.

### 3.2 Modular Design Flow

One of the design advantages that is shared by both network and bus architectures is that of a modular design flow. Both approaches take advantage of a well-defined interconnection mechanism that allows the designer to focus on the functionality of a module and reduce the effort spent on the design and debug of the interconnect mechanism. In both systems the modules must conform to the top-level port interfaces and obey the associated communication protocol, but in general this can be verified effectively at the module level.

Another advantage that comes as a result of this module-based infrastructure is flexibility both at the design phase and during run-time. Design time flexibility simply involves the notion that top-level module instantiation is similar among all modules. Replacing modules at design time only requires modifications to the module instantiations. Little or no change is required to the interconnect. The only possible change is that of port parameterization and involves no extra design. Run-time module replacement is a little more involved but can be a powerful feature for a system. Dynamic module replacement requires the use of partial reconfiguration as explained in section 2.3.

### 3.3 Clocking Scheme

The clocking scheme envisioned for this network architecture involves a single global clock for the network backbone (i.e. the system routers) and then separate clocks that are local to the modules of the system. For a small network topology a single system clock could be used, but the capability to handle multiple clock domains is vital for large systems. The boundaries for clock domains are located at the node interfaces, where FIFOs are used to accommodate the differing data rates.

### 3.4 Data Flow Control

Supporting multiple data rates on chip implies the potential for overflowing buffers. If a master node is capable of sending data at a rate that exceeds the slave node's ability to receive that data, it won't take long before the slave's buffer is filled and data is lost. In order to prevent such occurrences, a flow-control mechanism has been built into the architecture. This mechainsm involves the use of a clear-to-send (CTS) signal in conjuction with the node interface FIFOs. The CTS signal can either be manually disabled by the node module or it will automatically be disabled when the node interface's receive FIFO is *almost full*. The *almost full* flag is used so that data already in flight can be safely stored in the FIFO.

In order for flow control to be fully supported however, the CTS signal must be taken into account in the module design. The sending module must monitor the CTS signal and stall data transfers until CTS is again raised.

### 3.5 Summary

The strengths of this architecture lie in its circuit-switching advantages and system flexibility. The circuit-switching nature of this architecure allows for localized high-throughput data transfer between nodes. The flexibility includes that from both design and run-time perspectives and comes as a result of a standard interconnection interface and router/module parameterization.

The routers are the pieces responsible for managing the dedicated connections between modules, and the modules themselves contain network interfacing circuitry that aid in the handling of asynchronous data flow. A special CPU interface is used to connect a general processor to the network infrastructure, and its network access is controlled by the software. The chapters that follow describe in detail the implementation for each of these major components.

# Chapter 4

# **PNoC Router Description**

The router is the core of this network architecture. This chapter describes the implementation details of the router and explains the major components involved. The flexibility built into the router is explained, identifying its parameterizable features. Then, a description is provided as to how the routing table works and how it is updated as the system changes. Finally, the process of point-to-point connection control is explained.

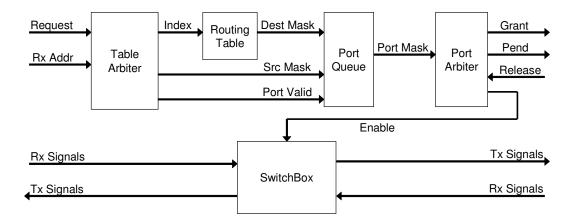

Figure 4.1: Router Block Diagram

### 4.1 Router Component Overview

The major components of the router are shown in the block diagram of Figure 4.1 and described as follows:

- **Table Arbiter** The table arbiter receives connection requests and schedules access to the routing table when mulitple requests are received on the same clock cycle. This block is also responsible for managing the routing table update requests.

- Routing Table The routing table maps network module addresses to ports that may be used to establish connections between modules.

- **Port Queue** This queue is used to maintain the connection request order while the requests await availability of the target port(s).

- **Port Arbiter** Once the target port(s) becomes available, the port arbiter establishes the desired connection and issues the appropriate *grant* signals. This block also monitors the *release* signals for the disabling of connections.

- Switch Box The switch box forms the actual connections between modules by enabling tri-state buffers that allow the Rx signals to drive the appropriate Tx signals.

### 4.2 Parameterizable Features

The flexibility that is built into the routers is key to enabling the construction of a wide variety of systems. Two major pieces of the router design are parameterizable therefore allowing for numerous system topologies. First is parameterization of the port interfaces that connect to the router. Second is the flexible way that routers may be connected to each other and to the other modules of the system.

### 4.2.1 Port Interface

Each router is built with a parameterizable number of port interfaces with up to a maximum of eight ports. The number of port interfaces indicates how many different modules can be connected to the router. The signals that define each port interface as seen by the router are listed in Table 4.1.

| Signal Name  | Direction | Description                                       |

|--------------|-----------|---------------------------------------------------|

| request      | input     | initiates either a router update request or a     |

|              |           | connection request                                |

| release      | input     | initiates a connection release                    |

| grant        | output    | indicates to the network module that its          |

|              |           | connection request has been granted               |

| sl_grant     | output    | indicates a connection has been established       |

|              |           | with the target node as a slave                   |

| pend         | output    | indicates that another module is requesting       |

|              |           | access to the destination port                    |

| rx_data[X:0] | input     | rx data bus of parameterizable width              |

| rx_addr[Y:0] | input     | rx address bus of parameterizable width           |

| rx_rnw       | input     | rx read-not-write signal                          |

| rx_valid     | input     | indicates valid rx data, address, and rnw signals |

| rx_cts       | input     | rx clear-to-send signal                           |

| tx_data[X:0] | output    | tx data bus of parameterizable width              |

| tx_addr[Y:0] | output    | tx address bus of parameterizable width           |

| tx_rnw       | output    | tx read-not-write signal                          |

| tx_valid     | output    | indicates valid tx data, address, and rnw signals |

| tx_cts       | output    | tx clear-to-send signal                           |

Table 4.1: Router Port Interface Signals

The widths of the  $rx\_data$ ,  $tx\_data$ ,  $rx\_addr$ , and  $tx\_addr$  signals are parameterizable up to a maximum width of 32 bits. Since ports of differing widths may be connected to each other, by convention the least significant bits of the larger bus are tied to the smaller bus signals. For example, if a 32-bit  $rx\_data$  from one port connnects to an 8-bit  $tx\_data$  of another port only the least significant 8 bits of  $rx\_data$  will actually be connected to  $tx\_data$ . Care must be taken when parameterizing the bus widths for a router's ports when that router is to be used with dynamic module replacement. Once a router's port widths have been set they are fixed and cannot be dynamically modified.

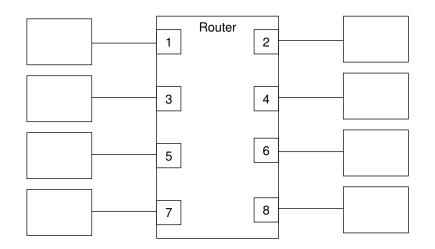

### 4.2.2 Router Connectivity

The other flexible aspect of the routers is in how they can be connected to the other modules of the system, including other routers. A topology can be constructed that best meets the specific system's needs. If a system requires more bandwidth between adjacent routers, mulitple ports can be used to connect the routers. Also if a system would benefit from multiple instances of a particular module, the routers have the capability built-in to establish a connection with whichever one is available at the time. The details of how this works will be described in Section 4.4.2.

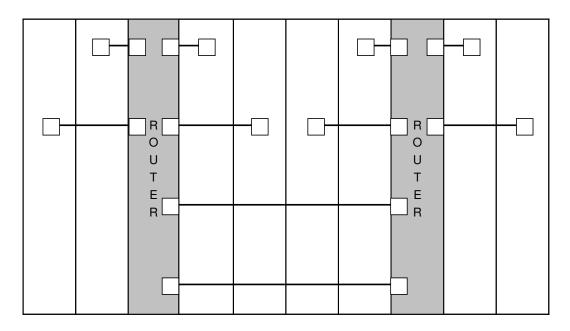

Depending on the FPGA used, this system-level flexibility may be compromised some when support for dynamic module replacement is desired. Because of the design restrictions identified in Section 2.3 to support dynamically replaceable modules, the network, implemented on Xilinx FPGAs, is limited to a column-based topology. Such a system may look similar to that shown in Figure 4.2.

#### 4.3 Routing Table

An important part of the router is its routing table. This table is responsible for mapping a given module address to the appropriate port interface. When a master node requests a connection to a given target node, the address associated with that target node is used as the index to the routing table. The output of the routing table is a mask value that identifies the ports that may be used to establish a route to the target node. Each bit of this mask value maps to one of the router's port interfaces.

### 4.3.1 Table Updates

Upon startup, and whenever a change is made to the network through dynamic module replacement, the routing tables are updated via router update requests. The

Figure 4.2: Topology for Dynamic Module Support

modules are responsible for adding themselves to and removing themselves from the routing table of the router that lies in their subnet.

These router update requests are implemented as connection requests addressed to the router. Routers maintain a fixed source address value of 0x00. Whenever a router receives a request from one of its port interfaces that is addressed to 0x00, it is recognized as a router update request. If the corresponding  $rx\_rnw$  signal is low then the request is to add the module to the routing table, otherwise the request is to remove the module. When adding a module to the routing table, the  $rx\_data$  signal represents the module's source address and is used to index the routing table. A read-modify-write is performed in which the table output is logically or'd with the port mask that made the router update request. Upon completion of the update request, the updating node's grant signal is raised and that node can begin requesting network connections.

Once a router update request has been serviced, that request is forwarded on to all adjacent routers until each router on the network has updated its table appropriately. Each router is initially configured with routing table entries for all of its adjacent routers so that routers know through which ports to forward the router update requests. In order to prevent a flooding of router update requests, the routers check to see if the updating entry is already in the routing table. If so the router does not forward the request.

### 4.3.2 Illustrative Example

A simple example will be used to illustrate how a router update request is processed. The timing waveform in Figure 4.3 will be used to help describe each step of the process.

| Signal Name    | Cycle 1 | Cycle 2  | Cycle 3 | Cycle 4       |

|----------------|---------|----------|---------|---------------|

| port2_request  |         |          |         |               |

| port2_grant    |         |          | /       |               |

| port2_rx_addr  |         | 0x00     |         | ( xxxx        |

| port2_rx_data  | _X      | 0x12     |         | < <u>xxxx</u> |

| port2_rx_rnw   |         |          |         |               |

| request_mask   |         | 0x02     |         | < xxxx        |

| table_read_en  |         | <u> </u> |         |               |

| table_write_en |         |          | \       |               |

| table_index    | _X      | 0x12     | Хх      | xx            |

| table_data_in  | XXXX    | 0x02     | Хх      | xx            |

| table_data_out | XXXX    | 0x00     | Ххх     | XX            |

Figure 4.3: Router Update Process

In this example a module with a source address of 0x12 is connected to the router's port-2 interface. During clock cycle 1, this module initiates the router update request by raising its  $port2\_request$  line while addressing the router ( $port2\_rx\_addr = 0x00$ ) and presenting its source address on the data bus ( $port2\_rx\_data = 0x12$ ). During this cycle the  $port2\_rx\_data$  is used to index the routing table and begin the read-modify-write process. At clock cycle 2 the output of the routing table becomes valid ( $table\_data\_out = 0x00$ ) and is logically or'd with the  $request\_mask$  value. The result ( $table\_data\_in = 0x02$ ) is then written to the routing table. This is how the module's address gets associated with the appropriate port interface. The result of this process is the value 0x02 stored at location 0x12. Then, when a module makes a connection request in which the desired target module has address 0x12, the router will associate that address with the port-2 interface and establish the desired connection.

#### 4.4 Connection Process

The primary function of the routers is to manage the establishment of dedicated connections between modules. Since multiple ports can make requests during the same clock cycle, this process involves a few levels of arbitration. The first is responsible for allowing access to the routing table and is controlled by the table arbiter. The second, controlled by the port arbiter, is in determining which port to use to establish the connection. Once a connection has been established the router serves as a single pipeline stage for the data transfer between the connected modules.

### 4.4.1 Table Arbitration

The routing table can only service one request at a time. Since multiple port requests can be issued on the same clock cycle, a table arbitration scheme is needed to determine which port gets access to the table. This arbitration scheme is implemented in a round-robin-like fashion. A series of ring counters are used to assign priorities to each port's *request* line. The request with the highest priority is given access to the router for that given transaction. The priority ring counter is then incremented, and the next high priority request is determined. This process continues in similar fashion as long as there are pending requests.

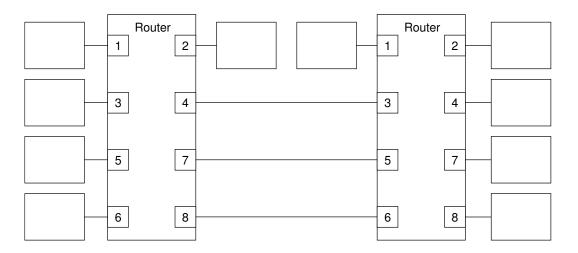

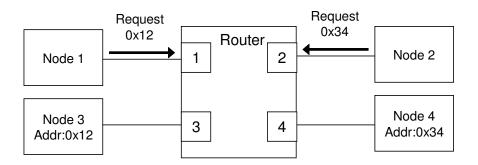

Since the connection requests only require access to the routing table for one cycle, the maximum table access latency is equal to the number of ports in the router. An example will be used to illustrate the table arbitration for two requests that are received on the same clock cycle. The block diagram in Figure 4.4 illustrates the modules involved in the connection process and the corresponding timing diagram is shown in Figure 4.5.

Figure 4.4: Table Arbitration Process - Block Diagram

In this example, Node 1 requests a connection to Node 3, and Node 2 requests a connection to Node 4. Since these requests are issued simultaneously, the router's port interfaces 1 and 2 receive the requests on the same cycle. Port 1 involves a connection request to a module with an address of 0x12 while port 2 addresses 0x34. At the time that these requests occur, during clock cycle 1, port 1 is assigned a priority level of 1 while port 2 is assigned priority level 2. Therefore port 1 is of higher priority and gets access to the routing table first. This is evident during clock cycle 2 where the *table\_index* is 0x12 which is the *port1\_rx\_addr* value. On the next clock cycle port 2 is granted access as the *table\_index* is 0x34, the *port2\_rx\_addr* value.

The module addressed as 0x12 (Node 3) is connected to port 3, and the module addressed as 0x34 (Node 4) is connected to port 4. These address/port associations

| Signal Name     | Cycle 1 | Cycle 2 | Cycle 3         | Cycle 4     |

|-----------------|---------|---------|-----------------|-------------|

| port1_request   |         |         |                 |             |

| port1_rx_addr   | _X      | 0       | x12             |             |

| port2_request   |         |         |                 |             |

| port2_rx_addr   | _X      | 0       | x34             |             |

| port1_priority  | 1       | 4       | X;              | 3           |

| port2_priority  |         |         | Χ               | 4           |

| table_index     |         | 0x12    | ( <u>0x34</u> ) | < xxxx      |

| table_data_out  | XXX     | x       | ( <u>0x04</u> ) | 0x08        |

| port1_dest_mask | ххх     | x       | X0>             | <b>(</b> 04 |

| port2_dest_mask |         | XXXX    | >               | 0x08        |

Figure 4.5: Table Arbitration Process - Timing Diagram

are determined by the router during clock cycles 3 and 4. During clock cycle 3, one cycle after port 1's table access, the *table\_data\_out* value of 0x04 maps to port 3 as the third bit is a 1. Similarly during clock cycle 4, one cycle after port 2's table access, the *table\_data\_out* value is 0x08 which maps to port 4. These mapping mask values are later used by the port arbiter to enable the connections between Node 1 and Node 3, and between Node 2 and Node 4.

### 4.4.2 Port Arbitration

Once a port has successfully accessed the routing table, the table's output is used to determine with which port the requesting node must connect in order to establish a route to the target node. As mentioned previously, the output of the routing table is a port mask value that consists of a bit for each port associated with that router. Each bit in that mask value that is a 1 represents a port that may be used to establish the desired connection. Once this destination mask has been obtained, the router must determine whether any of the corresponding destination ports are available. A port is unavailable if (a) it is currently used in a previously established connection or (b) if the node attached to it has its  $tx\_cts$  held low, indicating that the node is not ready to accept a connection. Since it is possible that none of the destination ports may be available, each port has a request queue associated with it. A requesting port waits its turn in the queue until the destination port becomes available. At that point a simple arbitration scheme is used to determine which of the available destination ports to use, and the connection is established. A grant signal is then issued to the requesting node and the  $sl\_grant$  is issued to the target node to indicate that a dedicated connection is in effect.

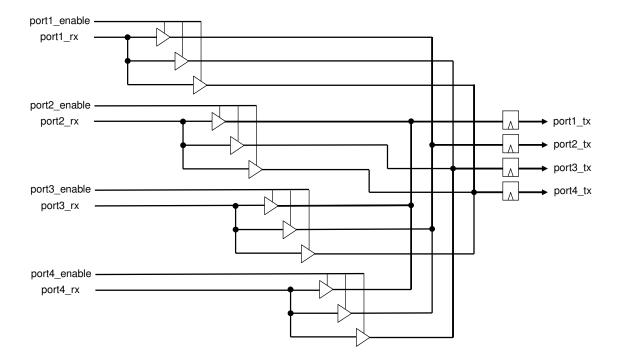

Figure 4.6: Switch-box Hardware Diagram

The actual connection circuitry is implemented as a tri-state enabled switchbox. Each set of *port\_rx* signals, which includes the  $rx\_data$ ,  $rx\_addr$ ,  $rx\_rnw$ ,  $rx\_valid$ , and  $rx\_cts$  signals, has a one-hot *enable\_mask* bus associated with it to enable one of the tri-state buffers that correspond to the target *port\_tx* signals. Figure 4.6 shows how this would look where there exists four port interfaces to the router.

### 4.4.3 Termination Process

There are two instances in which a dedicated connection might be terminated through the assertion of the *release* signal: upon completion of the data transfer, or at the signaling of an optional timeout mechanism. In both cases it is the node that established the connection that must initiate the release.

When the desired data transfer is complete, the master node issues a release command to the router by raising the *release* line. This *release* signal disables the dedicated connection and clears the *grant* signals between the two ports. In situations where a potential hogging of a port might be detrimental to the operation of the system, the master node may monitor a timeout request signal (*pend*) from the router and comply with the assertion of the *release* signal to allow a pending connection to be established.

### 4.4.4 Illustrative Example

A basic example will be used to further illustrate how the router's connection process is realized. In this example it is assumed that there are four port interfaces to the router, and that the module at port 1 desires to connect to port 3, and the module at port 2 desires to connect to either port 3 or port 4. Once the requests have been received by the router, the table arbitration process, as explained in Section 4.4.1, is used to associate each request with its desired destination port mask. For this example the destination port mask for port 1 is 0x04 and the destination port mask for port 2 is 0x0C. Figure 4.7 illustrates the connection process that takes place after the table access has occured.

| Signal Name   | Cycle 1     | Cycle 2 | Cycle 3 |      | Cycle 10 | Cycle 11 |

|---------------|-------------|---------|---------|------|----------|----------|

| port_valid    |             |         | \       |      |          |          |

| dest_mask     | X 0x04 X    | 0x0C    | X       | X    | xxx      |          |

| src_mask      | X0x01X      | 0x02    | Х       | X    | xxx      |          |

| open_mask     | 0x0F        |         |         | (0>  | (00      | 0x0F     |

| grant_mask    | <u>0x00</u> | 0x05    | X       | 0x0F |          | 0x00     |

| port1_enable  | <u>0x00</u> |         | 0x      | 04   |          | 0x00     |

| port2_enable  | 0x00        |         | X       | 0x08 |          | 0x00     |

| port3_enable  | <u>0x00</u> |         | 0x      | 01   |          | 0x00     |

| port4_enable  | 0x00        |         | Х       | 0x08 |          | 0x00     |

| port1_release |             |         |         |      |          |          |

| port2_release |             |         |         |      | /        |          |

Figure 4.7: Port Connection Process

The destination port mask for port 1 becomes valid during clock cycle 1  $(dest\_mask = 0x04)$ . At this point the connection request is loaded into a queue to wait for the availability of port 3, as determined by the *open\\_mask* value. Since initially all the ports are available  $(open\_mask = 0x0F)$ , the destination port can be selected, and the connection established. Therefore during clock cycle 2, the *grant* and *sl\_grant* signals for ports 1 and 3 respectively are raised  $(grant\_mask = 0x05)$ , and the tri-state switch is enabled appropriately  $(port1\_enable = 0x04)$ .